為處理海量數(shù)據(jù)、復(fù)雜算法、超低延時(shí)的應(yīng)用提供數(shù)字化加速驅(qū)動(dòng)力是賽靈思一直的目標(biāo),為此,賽靈思研發(fā) Bootgen 工具支持將二進(jìn)制文件縫合在一起并生成器件啟動(dòng)鏡像。定義了多個(gè)屬性和參數(shù)作為創(chuàng)建啟動(dòng)鏡像時(shí)的輸入

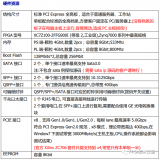

Zynq-7000 SoC 啟動(dòng)鏡像布局

Zynq-7000 SoC 上的 bootROM 作為應(yīng)用處理器單元 (APU) 中運(yùn)行的首個(gè)軟件,可在安全環(huán)境內(nèi)以加密 FSBL 來(lái)執(zhí)行。受支持的啟動(dòng)模式包括:

? JTAG 模式主要用于開發(fā)和調(diào)試

? NAND、并行 NOR、串行 NOR (QSPI) 和安全數(shù)字 (SD) 閃存用于啟動(dòng)器件。

啟動(dòng)頭文件

Versal ACAP 啟動(dòng)鏡像格式

Versal ACAP 中的平臺(tái)管理控制器 (PMC) 負(fù)責(zé) Versal ACAP 的平臺(tái)管理。由 2 個(gè) PMC MicroBlaze 處理器、ROM 代碼單元 (RCU) 和平臺(tái)處理單元 (PPU) 所處理的啟動(dòng)鏡像格式:

? RCU:ROM 代碼單元包含三重冗余 MicroBlaze 處理器和只讀存儲(chǔ)器 (ROM),其中包含可執(zhí)行 bootROM

? PPU:平臺(tái)處理單元包含三重冗余 MicroBlaze 處理器和 384 KB 的專用 PPU RAM

Versal ACAP 啟動(dòng)鏡像模塊框圖

創(chuàng)建啟動(dòng)鏡像

Bootgen 定義了多個(gè)屬性用于生成啟動(dòng)鏡像,并根據(jù)文件中傳遞的內(nèi)容來(lái)解釋和生成啟動(dòng)鏡像。由于有多條命令和多個(gè)屬性可用,Bootgen 定義了啟動(dòng)鏡像格式 (BIF) 來(lái)包含這些輸入。BIF 包含:

? 配置屬性,用于創(chuàng)建安全/非安全啟動(dòng)鏡像

? 啟動(dòng)加載程序,適用于 Zynq 器件和 Zynq UltraScale+ MPSoC 的第一階段啟動(dòng)加載程序 (FSBL);適用于 Versal ACAP 的 Platform Loader and Manager (PLM)

? 一個(gè)或多個(gè)分區(qū)鏡像

責(zé)任編輯:haq

-

控制器

+關(guān)注

關(guān)注

112文章

16445瀏覽量

179451 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131506 -

鏡像

+關(guān)注

關(guān)注

0文章

170瀏覽量

10802

原文標(biāo)題:用戶指南 | Bootgen:生成啟動(dòng)鏡像

文章出處:【微信號(hào):TheAlgorithm,微信公眾號(hào):算法與數(shù)據(jù)結(jié)構(gòu)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于Xilinx ZYNQ7000 FPGA嵌入式開發(fā)實(shí)戰(zhàn)指南

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒有?

當(dāng)ADC3663的LVDS輸出給到ZYNQ-7000的LVDS接收這兩者之間可以直連嗎?

正點(diǎn)原子fpga開發(fā)板不同型號(hào)

zynq7000 BSP無(wú)法在u-boot加載運(yùn)行怎么解決?

正點(diǎn)原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富!

zynq7000 BSP無(wú)法在u-boot加載運(yùn)行,為什么?

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

SoC布局中各種IC簡(jiǎn)介

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

Xilinx ZYNQ 動(dòng)手實(shí)操演練

Zynq-7000為何不是FPGA?

Zynq-7000 SoC 啟動(dòng)鏡像布局

Zynq-7000 SoC 啟動(dòng)鏡像布局

評(píng)論