作者:李秀娟,王祖強,張甜

隨著IC產業的發展,IP核的需求越來越高。微控制器MCU(Micro Control Unit)是嵌入式系統的核心,8位MCU IP核具有很高的通用性和靈活性,廣泛地應用于工業控制、機械設備、家用電器以及汽車等各個領域。本文設計的MCU IP核與Microchip公司的PIC16C57完全兼容。MCU IP核采用哈佛結構,內部單元可簡化為時序控制和數據通道兩部分。時序控制部分為數據通道提供控制信號,控制數據流動方向以及數據通路的選擇,它是IP核的指揮中心;數據通道部分在控制部分的控制下,具體實現MCU IP核的指令功能,它是影響MCU性能、功耗等因素的關鍵,是整個芯片設計的重點。

本文在設計該款MCU IP核的數據通道部分過程中,提出了一種特定的數據通道模型;最后,通過對整個MCU IP核仿真綜合,對該數據通道模型進行了驗證。

1 數據通道模型及數據總線Verilog HDL模型

1.1 數據通道模型結構圖

本文設計的MCU數據通道模型包含各數據通道單元及單條雙向數據總線。其中數據通道單元主要由特殊功能寄存器、通用寄存器及運算單元ALU等電路組成,每個通道單元還可再分為多個子通道單元。數據通道頂層模型如圖1所示,數據主要在數據總線及各數據通道單元中流動,由一條雙向數據總線完成每個數據組元的讀寫操作,充當每個組元源總線及目的總線雙重功能,并由特定電路完成總線數據的讀寫操作。該數據通道模型的最大特點為:通過n個子通道選擇信號,各數據通道單元內部可再分為n個子數據通道,由1/n譯碼器實現每一個時刻只有一條子通道選通。上層的數據通道控制信號仍然有效,作為子層數據通道的公共開關。依次類推,該數據通道模型可以是多層的。數據通道層次模型如圖2所示。

數據通道模型內數據的流動在時間軸上是時刻向前的,而數據流動的軌跡則呈現為相互環繞的螺旋形。

1.2 內部數據總線的Verilog HDL模型

數據通道模型中內部數據總線分別由三態門和多路選擇器實現讀寫操作,使用特定的硬件描述語言Verilog HDL代碼模型進行描述。對于掛接n個數據通道單元的m位數據通道內部數據總線,讀、寫兩種操作的Verilog HDL代碼模型分別表示如下:

2 設計實現

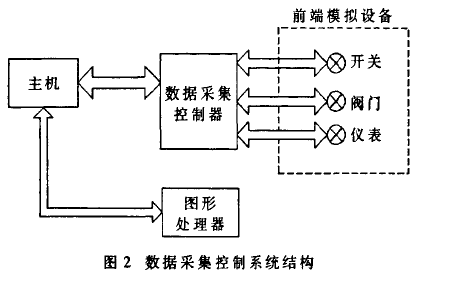

本文以數據通道單元ALU為例介紹數據通道模型的層次結構。ALU是MCU IP核的運算單元,是數據的加工處理部件,是數據通道中最特殊的數據通道單元。它實現加、減、與、或、異或、非、左移、右移、半字節交換等九種運算,其中前五種是雙操作數操作,其余四種是單操作數操作。對于雙操作數操作,ALU數據通道單元一邊采用兩條兩個源操作數數據通道,另一邊采用一條目標操作數數據通道;而單操作數操作僅需開啟一條源操作數數據通道。

本文的ALU采用低功耗設計。通過控制部分譯碼得出ALU主要實現四種運算:算術運算、邏輯運算、移位運算以及半字節交換運算。本文通過加、減操作復用一個8位超前進位加法器,將ALU模塊分為8個運算單元,構成8個子數據通道。通過對ALU子數據通道選通信號aluop[2:0]進行譯碼對8條子通道進行選通,如表1所示。在系統復位或者不工作時,各運算單元處于休眠狀態;在每條指令的執行周期,ALU中8個子數據通道始終只有一條子數據通道處于選通工作狀態。不同類的指令對應不同的數據通道,把對ALU運算的控制轉化為對ALU內子數據通道的選擇,降低了ALU整體功耗。

一般來說,數據通道的選通由選通信號控制,而數據通道的開啟必須由整個MCU IP核控制部分產生的四相不重疊時鐘節拍控制,分別為clk1、clk2、clk3、clk4。時鐘節拍不參與數據通道的選擇,所起作用只是數據通道的開啟。數據通道內數據的流動是有方向的,本文中數據流動的方向性體現為不同時鐘節拍控制的不同數據通道的開啟。以單操作數指令半字節交換指令(SWAP)為例說明,半字節交換指令只需開啟一條源操作數通道。如圖3所示,控制部分在clk1時取出指令,產生控制信號,進入數據通道操作;在clk2時,在存儲單元中選擇源操作數寫入數據總線,開啟ALU運算單元的源操作數alu_xbus_a[7:0]數據通道,此時內部雙向數據總線充當ALU源總線;在clk3時,根據ALU模塊子通道選通信號aluop[3:0]選擇ALU功能模塊SWAP,開啟源操作數進入ALU進行半字節交換運算的數據通道;在clk4時,將ALU運算單元的運算結果aluout[7:0]通過數據總線寫入到各目的數據通道單元中,即開啟目的操作數數據通道,此時內部雙向數據總線充當ALU目的總線。

需要說明的是,圖3中數據databus[7:0]來自數據總線,由數據通道單元特殊功能寄存器和通用寄存器提供數據。其中特殊功能寄存器包括F0間址寄存器、F1實時時鐘/計數寄存器RTCC、F2程序計數器PC,F3狀態計數器STATUS、F4寄存器選擇寄存器FSR以及F5、F6、F7 I/O寄存器。可以向下再分為8條子數據通道,子通道選通信號為fsel[2:0],而上層數據通道開關控制信號為rf_spr_re、rf_spr_we,即特殊功能寄存器讀寫控制信號。其具體實現與ALU數據通道單元類似,這里不再贅述。

在該款MCUIP核數據通道模型中,數據總線全部采用本文所述的Verilog HDL代碼模型描述。基于中心國際SMIC 0.35μm工藝庫(工作電壓為3伏),使用Synopsys公司VCS和 DC對該款MCU IP核進行了仿真綜合,并進行了功耗分析。綜合分析結果得出,該數據通道電路結構規整,設計得到了簡化,總體功耗約為49.5980mW,實現了低功耗設計。

本文使用固定電路結構描述內部數據總線,通過特定層次化數據通道模型的設計,體現了自頂向下(Top-Down)的設計方法,降低了整個MCU IP 核設計的復雜度,縮短了設計周期。該設計適用于大規模系統芯片開發設計。

責任編輯:gt

-

微控制器

+關注

關注

48文章

7649瀏覽量

152106 -

mcu

+關注

關注

146文章

17317瀏覽量

352635 -

寄存器

+關注

關注

31文章

5363瀏覽量

121157

發布評論請先 登錄

相關推薦

FPGA的IP軟核使用技巧

IP核生成文件:XilinxAltera

使用ISE的CIC IP核時仿真出來的結果求幫分析!!

基于層次模型的USB2.0接口芯片IP核固件的設計

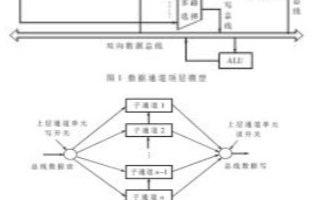

基于FPGA的數據采集控制器IP核的設計方案和實現方法研究

基于VHDL語言的IP核驗證

基于Avalon總線的可配置LCD控制器IP核的設計

如何使用FPGA進行仿真系統數據采集控制器IP核設計的資料概述

測試與驗證復雜的FPGA設計(2)——如何在虹科的IP核中執行面向全局的仿真

MCU IP核特定層次化數據通道模型的設計及仿真驗證分析

MCU IP核特定層次化數據通道模型的設計及仿真驗證分析

評論