無線定位技術是利用無線信號來判定某一半徑范圍內無線信號發射終端物理位置的一種方法。移動通信網絡中移動終端的定位方法可分為兩大類:一類是基于手機的定位方法,通過在每個移動終端(如手機)內部安裝微型GPS接收器進行定位。另一類是基于網絡的定位方法。這種方法與基于移動終端的定位方法正相反,該方法根據移動終端發出的信號到達基站的參數,如到達時間(TOA)參數、到達角度(DOA)參數等進行定位。基于網絡定位的方法需要用到陣列天線,陣列天線傳感器接收到的無線信號經過前端預處理進行放大、取噪,然后進行模數轉換,最后DSP對接收數據進行處理得到方向估計。

因為TMS320VC5402(以下簡稱C5402)內部沒有集成A/D,因此在數據采集時需要使用A/D轉換芯片,A/D芯片與C5402的接口設計成為一個重要的問題。為了充分利用C5402所提供的多通道緩沖串口資源,簡化系統設計,本系統利用兩片C5402來完成四路數據采集,大大提高了串口工作效率。TMS320C54x系列DSP芯片只有同步串口,通常只能用于與具有同步通信接口的外設進行通信。本系統中采用TI公司的的異步通信芯片TL16C550C完成數據的串/并、并/串變換,實現DSP與PC機的高速串行通信。本文在實際經驗的基礎上,給出了兩片DSP組成的無線定位模擬系統,分別介紹了系統中串行A/D TLV1572、異步串行通信芯片TL16C550C的工作原理,同時分析了系統獨立工作的程序裝載原理和可行性。

系統主要器件和原理介紹

串行A/D芯片TLV1572

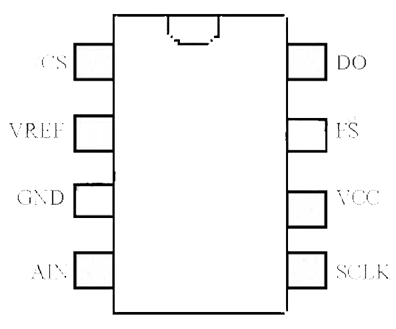

TLV1572是TI公司生產的高速十位串行A/D轉換芯片。TLV1572采用的是8腳的SOIC封裝,如圖1所示。TLV1572所要求提供的供電電壓在3V-5V之間,TLV1572的最小參考電壓為2.7V。在5V供電時,最高轉換速度為1.25MSPS,在3V供電時最高轉換速度為625KSPS。為了使其達到最大的轉換速率,所提供的時鐘分別為20MHz和10MHz。TLV1572可以通過3或4個串行口線直接與DSP或其它數字微處理器串口相連,不需要外加邏輯,但是轉換速度受SCLK供給時鐘的限制。TLV1572與DSP的多通道緩沖串口通過/CS、SCLK、DO和FS四條線相連,此時DSP的CLKR產生移位脈沖,FSR產生幀同步信號,并分別提供給TLV1572。當TLV1572與其它串口微處理器相連接時FS必須提供高電平,通過/CS、SCLK、DO三條線來完成數據傳輸。當/CS為高時,A/D芯片各管腳處于三態狀態。在/CS由高變低時,TLV1572檢測FS引腳的狀態來確定工作模式,若FS為低則為DSP模式,若FS為高則為其它微處理器模式。

圖1 TLV1572引腳圖

當TLV1572工作在DSP模式時,必須保證在/CS變低時,FS為低電平,并且要鎖存一定時間。/CS為低時,DO跳出三態狀態,但是直到FS為高時芯片才脫離休眠狀態。TLV1572在每個時鐘SCLK的下降沿檢測FS的狀態,一旦檢測到FS為高,TLV1572開始采樣。在FS的下降沿,A/D芯片通過移位時鐘將數據移到DO上。在6個前導0傳送之后,DSP可以在時鐘的下降沿得到A/D轉換的數據,如圖2所示。在最低位移出之后,A/D芯片自動進入休眠狀態,直到FS下一次有效。如果FS在16位傳輸完成后立即有效,則A/D開始新的數據轉換,此時A/D為連續轉換。若FS在TLV1572轉換數據的過程中變高,則A/D芯片被復位,開始新的數據轉換周期。因此可以通過設置FS改變數據傳輸的位數。

異步通信芯片TL16C550C

TL16C550C是TI公司的異步通信芯片,具有與DSP的連接硬件簡單,使用經濟、可靠的優點。其主要特點如下:管腳與TL16C450兼容;可由軟件設定16字節的FIFO以減少CPU中斷;波特率發生器可編程;具有可編程的串行數據發送格式;數據位長度為5、6、7、8;具有偶校驗、奇校驗或無校驗模式;停止位長度為1、1.5、2;采用44引腳PLCC封裝。

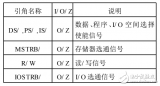

TL16C550C內部共有11個寄存器,這些寄存器分別用于實現通信參數的設置,對線路及MODEM的狀態訪問,數據的發送和接收以及中斷管理等功能。在編程過程中,可由A0、A1、A2 三條片內寄存器選擇線和線路控制寄存器(LCR)的D7位(DLAB)一起訪問或控制TL16C550C的任何一個寄存器。表1給出了訪問這些寄存器時DLAB和A0、A1、A2的狀態。因為接收和發送緩沖寄存器的DLAB、A0、A1、A2各位都相同,因此還必須通過讀寫信號來加以區分。

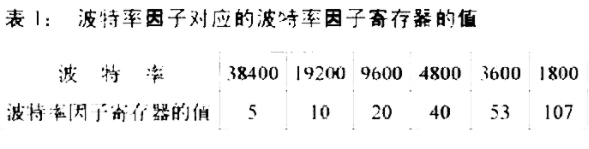

因為接收/發送緩沖寄存器和中斷使能寄存器分別與波特率因子寄存器的低位和高位相同,要通過DLAB加以區分,可以任意選擇寫入波特率因子的高字節和低字節的順序,寫入前必須置LCR的DLAB位為1。寫入波特率因子后應將D7置為0,以便訪問其他寄存器。在外接晶振為3.072MHz時,幾種常用的波特率所對應的波特率因子寄存器的值如表1所列。

C5402的Bootloader原理

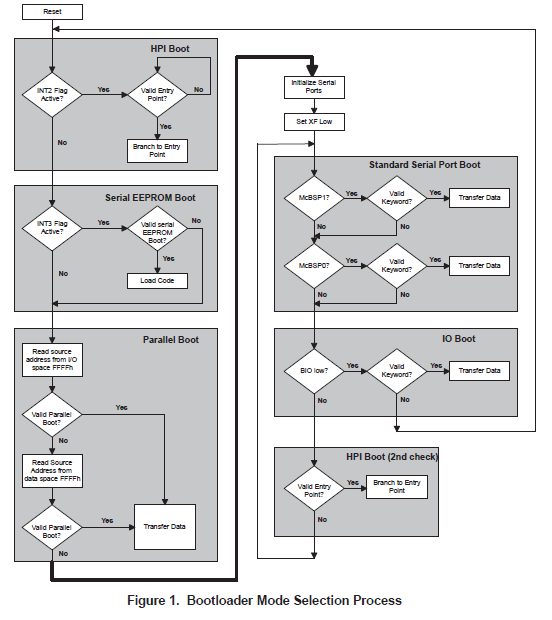

C5402上電后,首先檢查MP/MC引腳的狀態:如果為高電平,說明DSP處于微處理器工作模式,從外部程序存儲器0FF80h地址開始執行用戶程序;若為低電平,DSP被設置為微計算機模式,從片內ROM的0FF80h地址開始執行程序。在C5402的0FF80h地址處存放著一條跳轉至0F800h處執行DSP自行引導裝載(Bootloader)程序的指令。當C5402執行Bootloader程序時,將會按HPI裝載模式→串行EEPROM裝載模式→并行裝載模式→標準串行口裝載模式 →I/O口引導裝載模式的順序循環檢測,以決定執行哪種啟動模式。

對于以C5402為核心的數字信號處理系統來說,并行引導裝載模式被認為是最適用的。因為HPI引導裝載模式、標準串行口引導裝載模式和I/O口引導裝載模式只適用于由其它處理器為C5402提供運行代碼的多處理器系統中,串行EEPROM引導裝載模式只支持價格偏高的SPI端口EEPROM,而并行引導裝載模式可采用的并行EEPROM和Flash種類很多,有的價格比較低,操作起來比較簡單。在不自己編寫Bootloader程序的情況下,并行引導裝載模式最大只能裝載32K字的程序或數據。若程序數據大于32K,此時需要自己編寫一個并行裝載的內核程序,通過片內的裝載程序將編寫的內核程序傳送到片內DRAM中,然后再運行裝載內核程序,將大于32K的程序數據送到片外的SRAM中。在有兩個或兩個以上的C5402或具有標準串口功能的多微處理器的系統中,若為每一個微處理器都配置一個并行的Flash來存儲程序,會很浪費資源,占用總線。而利用一片Flash,主機利用并行裝載,然后主機通過HPI裝載模式對其它C5402進行裝載,這樣就可以節省大量資源。

系統硬件結構及原理分析

系統硬件原理圖

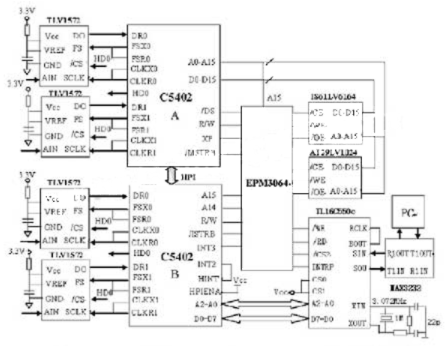

本系統主要完成無線信號的采集、采樣信號的處理得到方向估計及與PC機通信,系統的硬件原理如圖2所示。

圖2 CPLD中的VC5402與TL16C550C的系統邏輯圖

數據采集與通信

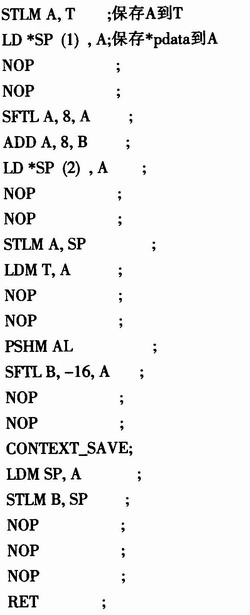

為了達到與C5402很好的匹配,A/D電源和參考電壓都接了3.3V。A/D的FS接DSP的FSX和FSR,使數據輸入的幀同步信號由DSP產生。SCLK接DSP的CLKX和CLKR,這樣數據的輸入和輸出時鐘均來自DSP。C5402與各自兩片A/D進行數據傳輸時,設置串口中斷工作在00模式,即串口數據到達觸發中斷,這樣CPU可以根據A/D傳輸數據產生相應的串口中斷RINT0或RINT1。當兩個串口的數據同時到達,即同時申請中斷時,C5402的CPU會根據中斷優先級響應RINT0中斷,然后再響應中斷RINT1。為了保證數據通信的可靠性,避免數據沖突,在響應RINT1中斷的過程中,串口0無中斷請求。 兩片C5402(A,B)是通過HPI口進行數據交流的,其中C5402(A)作為主機,C5402(B)工作在HPI 模式。兩片DSP分別計算自己的數據的自相關函數Rxx,由C5402(A)將數據送到C5402(B)中,進行互相關函數Rxy計算,然后通過ESPRIT方法計算出方向。估計完方向后,C5402(B)通過TI公司的異步串行芯片TL16C550C將估計結果傳給PC機進行網絡定位,或下一步處理。

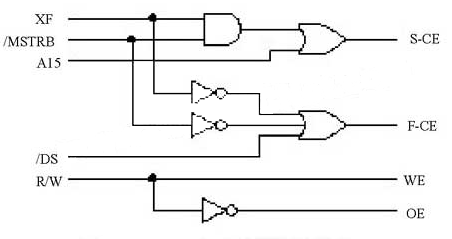

TL16C550C能以16MHz的速度讀寫數據,讀寫信號的脈寬很窄,使用一般的串口微處理器誤碼率較高,而TL16C550C能夠很好的與DSP匹配。這里VC5402以19200的波特率與PC機通信, 當XIN、XOUT端外接3.072MHz晶振時,波特率因子寄存器的低位的值應為0AH,高位值為00H。C5402與TL16C550C之間的邏輯控制通過CPLD來完成,其內部邏輯如圖3所示。

圖3 CPLD中的VC5402與TL16C550C的系統邏輯圖

由于RS-232-C電路電平與CMOS電平不同,因此RS232驅動器與CMOS電平連接時必須經過電平轉換,本系統采用MAXIM公司的MAX232來完成這一功能。

系統獨立工作的程序裝載過程

本系統的程序裝載分為兩部分:C5402(A)自身的并行裝載和C5402(B)的HPI裝載。

C5402(A)與Flash AT29LV1024和SRAM IS61LV6164之間的邏輯如圖4所示。C5402(A)上電復位裝載時,由于Bootloader程序在初始化時設置XF為高電平,在系統進入并行引導裝載模式后,C5402(A)從數據尋址為0FFFFh單元(A15=1,選中Flash)中讀取將要載入的程序存儲區首地址和并行裝載數據流。此時,C5402可以將 Flash地址08000h-0FFFFh單元中的數據讀到C5402對應于0000h-7FFFh尋址區的片內DARAM和片外SRAM中。Bootloader程序結束后用戶程序的第一條語句為RSBX XF,置XF引腳為低電平, Flash始終不選通。這樣,SRAM的高32K區域(08000h-0FFFFh)被釋放出來,可以作為C5402(A)運行時的數據區或程序區使用。C5402(A)裝載進來的程序數據主要分三部分:給C5402(B)的裝載程序,自身的運行程序及C5402(B)的運行程序。

圖4 VC5402與存儲器的邏輯圖

在C5402(A)進行并行裝載的過程中,C5402(B)在判斷是哪種裝載模式。因為C5402(B)的HINT和INT2連在一起,在DSP上電初始化時將07FH單元清0,同時HINT置0,這樣導致了INT2的IFR的相應標志位有效,C5402(B)查詢到INT2的標志位有效后,判斷是HPI裝載模式。C5402(A)在進行完并行裝載后,首先運行裝載程序,將C5402(B)運行程序數據傳送C5402(B)中,最后將C5402(B)的程序入口地址寫到07FH單元,表明HPI裝載結束。

系統軟件設計

系統的軟件設計主要包括,多通道緩沖串口的初始化,串口中斷服務程序,并行裝載程序設計,TL16C550C的初始化及HPI設計等。

程序設計應注意的問題

(1)McBSP工作在數據接收中斷方式,因此全局中斷和串口中斷的相應位應該合理設置。同時,在設置中斷向量表時,使中斷向量表的位置與處理器模式狀態寄存器PMST中的中斷向量指針IPTR相對應,使IPTR的9位地址指向128字的中斷向量所在的程序頁,同時,中斷向量表要嚴格按照C5402規定的格式編寫,否則不能正確地產生需要的中斷結果。

(2)要實現DSP數據采集系統的脫機獨立運行,程序裝載十分關鍵。C5402(A)進行并行裝載,要求AT29LV1024中的程序數據流嚴格按照并行裝載的格式,依次給C5402(B)裝載程序、C5402(A)自身執行程序,C5402(B)的程序裝載到片內DRAM和片外SRAM中。

(3)注意到系統設計中,C5402(B)的HPI口既用來進行程序裝載,又作為兩片DSP通信接口,為了避免混亂,在C5402(B)的程序中應將IFR中INT2的相應位清零,最好在IMR中屏蔽INT2。

(4)為了實現兩路A/D和C5402之間的時序匹配,避免數據沖突,需要注意C5402采樣率發生寄存器SRGR1中CLKGDV位的設置,使C5402工作時鐘周期大于兩個串口中斷的響應時間。

TL16C550C的軟件流程

TL16C550C 初始化程序主要完成波特率及其它工作寄存器的設置。這里設置TL16C550C工作模式為8位數據位,2位停止位,奇校驗狀態。TL16C550C的軟件設置流程如圖5所示。

圖5 TL16C55C工作的軟件流程(略)

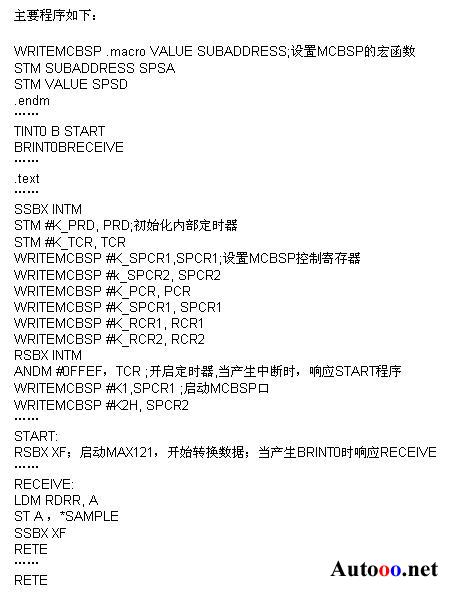

串口接收的部分初始化程序

下面根據多通道緩沖串口的特性和兩路串行A/D工作的要求,主要介紹一下串口接收的軟件設計和串口部分關鍵設置。

;=====初始化串口0========

stm #0, SPSA0

stm #0000h, SPSD0 ; #0000H SPCR10

stm #1, SPSA0

stm #0000h, SPSD0 ; #0000H SPCR20

stm #2, SPSA0

stm #0040h, SPSD0 ; #0040H RCRC10 每字16位

stm #3, SPSA0

stm #0040h, SPSD0 ; #0040H RCR20 每幀一段,每段一字

stm #6, SPSA0

stm #000fh,SPSD0 ; #0009H SRGR1 時鐘周期 CLKG=“6”.4MHz

stm #7, SPSA0

stm #300fh, SPSD0 ; #3010H SRGR20 幀周期為16個CLKG

stm #0eh,SPSA0

stm #0a04h, SPSD0 ; #0A04H PCR0 FSX, CLKX輸出,FSR,

CLKR輸入

;=====初始化串口1======

串口1的初始化程序參見串口0

;=====啟動接收========

stm #0,SPSA0

stm #0001h, SPSD0 ;啟動串口0接收

stm #1,SPSA0

stm #00c0h, SPSD0 ;內部產生時鐘產生FSG

stm #0,SPSA1

stm #0001h, SPSD1 ;啟動串口1接收

stm #1,SPSA1

stm #00c0h, SPSD1 ;內部產生時鐘產生FSG

;==串口0接收中斷子程序===

.sect “brint0”

host_brint0:

rsbx intm ;關中斷

ldm drr0,A

stl A,*ar4+ ; 接收

:::

其它處理程序

rete

結束語

本文利用兩片DSP,根據TM320C5402多通道緩沖串口的特點,提出了由四個陣列天線傳感器陣元組成的DOA估計硬件設計方案,并給出了系統獨立工作的硬件原理圖和軟件設計的部分關鍵程序。并行裝載模式和HPI裝載模式同時使用,有效利用了系統資源,減小成本,同時TL16C550C的使用實現了DSP與PC機的高速串行通信。

責任編輯:gt

-

處理器

+關注

關注

68文章

19407瀏覽量

231183 -

dsp

+關注

關注

554文章

8059瀏覽量

350420 -

無線

+關注

關注

31文章

5470瀏覽量

173829

發布評論請先 登錄

相關推薦

HPI方式自舉在TMS320VC5402 DSP芯片上的實現

在TMS320VC5402處理器上怎么移植μC/OS-II操作系統?

怎樣去設計TMS320VC5402與模擬芯片TLC320AD50C的接口?

基于TMS320VC5402 的DSP基本系統的設計

MAX121與TMS320VC5402在高速數據采集中的接口

μC/OS-II在TMS320VC5402上的移植

TMS320VC5402和TMS320UC5402引導加載程序的特點和操作詳細概述

TMS320UC5402和TMS320VC5402數字信號處理器硅勘誤表詳細分析概述

TMS320VC5402 數字信號處理器

基于TMS320VC5402處理器實現無線定位模擬系統的設計

基于TMS320VC5402處理器實現無線定位模擬系統的設計

評論