作者:龍浩;蘇曉龍;王香婷

1 引言

隨著現代的圖形采集技術發展迅速,各種基于ISA,PCI,USB1.1等總線的圖形采集卡速度已經不能滿足用戶的需求,而采用 USB2.0以后就可以解決這個傳輸速度上的瓶頸,USB2.0的速度是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續處理的要求。系統中采用 DSP+CPLD的硬件設計方案,采用現場可編程芯片 CPLD及兩片 SRAM構成的圖像采集和存儲系統,可以根據不同的需要進行現場編程,具有通用性好、價格相對便宜,易于系統調試,升級等特點。系統中 CPLD選擇的型號是 ALTERA公司的MAX7000系列低功耗芯片EPM7128A。片外大容量 SRAM是DSP與 CPLD的聯系橋梁,系統設計也利用這座橋梁將 USB和 CPLD有機地聯系起來。該系統的市場調查表明,適應于各種主動或被動的監測場合,以及醫療、公安和工業檢測當中。

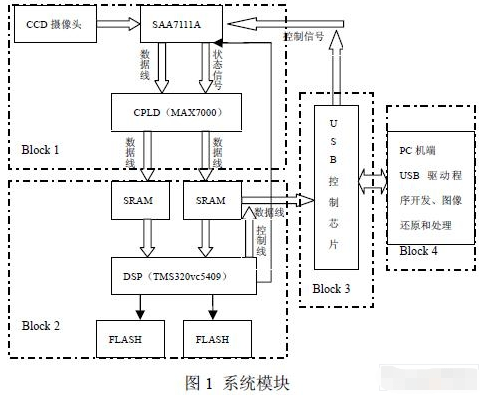

2 系統的硬件設計方案圖像通信系統包括以下四個部分,如圖 1所示:

(1) 圖像采集模塊,由線陣 CCD、CCD 驅動信號增強電路、CPLD 和 A/D 組成,用于采集圖像信號,并將模擬信號數字化,以便 DSP 處理。本系統采用黑白高速線陣TH7814A,該 CCD 為雙路輸出,像敏單元尺寸7 ?m,最高驅動頻率 50 MHz;CCD 驅動信號增強電路是為滿足該 CCD 所需的 9 V 高速驅動而設計的;A/D 芯片采用 SAA7111A,它由雙通道模擬預處理電路、自動鉗位和增益控制、時鐘產生電路、數字多標準譯碼器色度/飽和度/對比度控制電路、彩色空間矩陣和 27MHz數據處理通道七部分組成,并由 DSP模擬I 2C總線進行時序配置,以上器件同步驅動脈沖均由 CPLD 產生。

(2)圖像信號的處理和控制模塊,該模塊由 DSP和兩片 SRAM組成,完成了整個系統圖像數據的處理和對各模塊的集中控制與處理,DSP選用了 TI公司的通用 16位定點 DSP芯片 TMS320VC5409,其指令的處理速度達到 100MIPS,通過片內的鎖相環倍頻使 DSP內部工作在 100M的頻率上,而外部的工作頻率可以相對較低,這就降低了電路設計的要求,提高了工作的穩定性。該系統圖像采集的一幀圖像是 720×576象素,如果取彩色圖像,每象素用 2個字節表示,每幀圖像是 720×576×16=*Mb,分成奇數場和偶數場分別存儲在兩片 SRAM中,則每片的 SRAM存儲 3.2Mb的圖像數據,因此選用了 256K×1*M位的靜態存儲器(SRAM)。在圖像處理領域,通常只需要黑白圖像,可以只取圖像的黑白部分,每象素用 1個字節表示,每幀圖像是 3.2Mb ,每片 SRAM存儲 1.6Mb的圖像數據。所采用的 EZ-USB芯片理論速率是 480Mbps,實際測得的速率是 320Mbps,因此圖像采集卡每秒傳輸約 5幀彩色圖像或 10幀黑白圖像。

(3)USB傳輸和控制模塊,設計中選用的芯片是EZ-USB FX2系列的CY7C68013芯片,該芯片是針對 USB2.0的,而且和 USB1.0兼容,由于 USB2.0的速度可以達到480Mb/S,并且FX2自身具有EP2,EP4,EP6和EP8的4個大流量端點,CY7C68013可以實現從外部存儲器高速的讀取和寫入數據。在圖像的采集、存儲和傳輸設計上,不再是奇數場存儲在奇數SRAM,偶數場存儲在偶數SRAM。最重要的改進是一幀圖像在完成行延時和像素延時之后,當偶數場到來后,先把偶數場的一半存儲在緊鄰奇數場數據的奇數 SRAM中,然后再把余下的偶數場數據的一半存儲在緊鄰偶數場數據的偶數 SRAM中。CY7C68013擁有 4個大容量端點,恰好滿足了整個系統對實時性的要求。在 USB從兩個 SRAM讀取圖像數據時,USB并不是從兩個SRAM“乒乓”式的讀取圖像數據,而是充分地利用 USB2.0的速度特點,由 CPLD的時序調度來先讀取奇數SRAM,然后讀取偶數SRAM。

(4)系統接口以及終端圖像還原和存儲模塊,系統中各個模塊之間都需要通過接口來實現模塊間通信,因此接口的選擇是系統是保證系統通信速度的關鍵。其中CPLD 和 DSP 都具有很高的數據處理速度 ,如何將這兩個器件的處理速度協調起來 ,會直接影響整體系統的運行速度 ,這就涉及到 CPLD如何與 DSP接口的問題。關鍵是選擇 DSP的接口方式和配置CPLD的片內RAM。系統中DSP與 SDRAM 用EMIF 的方式接口。同時,CPLD內部的存儲器主要是 Block RAM ,可用作雙口 RAM ,正好可將 CPLD 模塊中的結果緩沖器設為雙口 RAM ,一端是輸入 ,另一端則模擬為SDRAM 的接口。這樣就將 CPLD 與 DSP 有機地連接在一起。系統與終端的接口采用的是 480Mb/s的 USB2.0通用串行接口,用于發送和接受各種數據及控制信號。PC機端通過 USB接口接受數據,然后存儲到終端硬盤上,進行圖像的還原和處理。

系統工作流程:系統上電以后, DSP從外部 FLASH進行程序自舉,將程序引導進入片內高速 RAM中運行。DSP對 SAA7111A,TL16C750(異步通信芯片)進行初始化配置。初始化結束后,DSP進入等待狀態。當接收到手動或是軟件自動鏈路請求時, DSP進行鏈路撥號。鏈路成功后, DSP通過 CLKX產生觸發脈沖通知 CPLD可以采集圖像。從 CCD捕捉到的模擬視頻信號經過SAA7111A的模數轉換,由CPLD控制寫入片外高速大容量SRAM儲存,直到一幀圖像存儲完畢, CPLD交出總線。然后 USB控制器 FX2從兩片 SRAM中讀取奇數場和偶數場的圖像數據。一幀圖像采集結束后,CPLD置高 HOLD,同時產生中斷,通知 DSP。DSP收回總線,進行圖像傳輸。圖像采集部分的 TOKEN信號外接 LED,LED的亮、滅狀態可以直觀地顯示系統進程階段。 3 系統程序設計

3.1 DSP控制程序設計

DSP硬件控制程序用來管理硬件各部分工作方式及指定數據流向和組織方式 , 從 DSP執行的內外影響主要可以分為內部的算法操作,和對外部的控制操作兩個部分。其中外部的聯系主要是兩個方面:一個是和CPLD控制通道的相互交換;一個是和DSP與CPLD數據交換存儲器進行數據交換。系統的 DSP部分的軟件編寫采用模塊化編程,主程序只是在循環檢測按鍵情況,如果需要就調用需要的功能模塊函數,其主函數中的部分代碼如下:

While (1) { order num=scan key()://掃描按鍵 switch (order num)

{ case collection order://圖像采集命令 image_collection();//圖像采集 image_process();//圖像處理

image_save();//圖像保存 case usb_transfer://USB傳輸數據命令 set usb_transfer();//調用相應模塊 default:; }}

3.2 CPLD控制程序設計

CPLD的作用是產生 CCD、A/D及 DSP視頻端口的同步驅動脈沖。每次采樣時, CPLD將從 SAA7111A接收到一幀圖像數據保存到 SRAM中,此時 DSP等待;采樣結束后, DSP與 CPLD進行總線切換,分別連接到與上次不同的 SRAM上,DSP開始讀取數據,CPLD開始采集數據。每當 DSP和 CPLD 都完成各自的任務時,就進行總線切換 ,交換連接的 SRAM。此過程中由 CPLD控制程序的流程如圖 2所示。

3.3 USB的固件程序及驅動程序

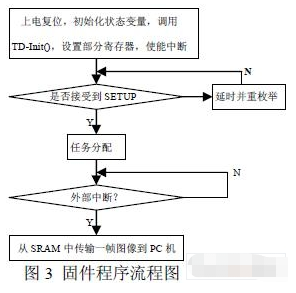

固件程序在該系統中其主要功能是實現 USB芯片的初始化和配置;控制 USB芯片接收并處理 USB驅動程序請求;控制芯片接收控制程序的控制指令。固件程序首先初始化所有的內部狀態變量,調用用戶初始化函數 TD-Init(),初始化 USB總線設備接口為非配置狀態,并打開中斷。當完成上面的任務后,固件程序就開始重新枚舉設備直到在端點收到 SETUP包為止。一旦 CY7C68013收到 SETUP包,固件程序就開始進行任務分配。固件程序流程圖如圖 3所示。

3.4 主機應用應用程序

在 PC機端,用 Visual C++ 6.0編寫客戶應用程序,應用程序通過 USB接收原始的奇數場和偶數場圖像數據,待接收完奇數場和偶數場圖像數據后,應用程序把它們組成完整的一幀圖像,并且把該幀圖像數據存儲到硬盤上,然后把這幀圖像轉化成 BMP格式的圖像存儲在硬盤上,同時以 BMP的形式顯示圖像。

4 結論

從總體來看,該系統以嵌入式設備為核心平臺,在此平臺上完成了機器視覺、圖像實時采集、數據傳輸 3個子系統的無縫連接集成開發。使得本系統只需較少的成本,擁有監測終端,就能完成主動智能監測、用戶遠程現場監控等功能。此外,本系統可針對不同需求,在添加各類相應的傳感器后,將可運用到包括消防、車輛防盜以及工業控制等很多實用領域。

本文作者創新點 :介紹了 DSP與 CPLD協同控制的高速圖像通信系統的設計,采用高速 USB2.0作為圖像傳輸的接口,完成了機器視覺、圖像實時采集、數據傳輸 3個子系統的無縫連接集成開發。

責任編輯:gt

-

dsp

+關注

關注

554文章

8059瀏覽量

350425 -

芯片

+關注

關注

456文章

51176瀏覽量

427263 -

cpld

+關注

關注

32文章

1257瀏覽量

169635

發布評論請先 登錄

相關推薦

數字信號處理器TMS320VC5409相關資料下載

TMS320VC5409 pdf datasheet

TMS320VC5409A pdf datasheet

基于TMS320VC5409的嵌入式WEB數據服務器的實現

TMS320VC5409A-160,pdf(Fixed-Point Digital Signal Processor)

TMS320VC5409-80,pdf(Fixed-Point Digital Signal Processor)

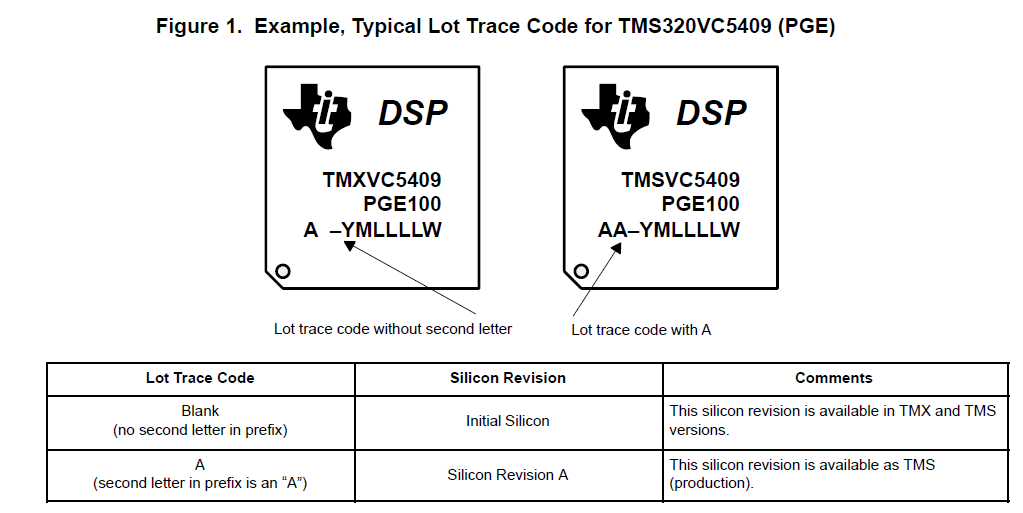

TMS320UC5409/TMS320VC5409 Digital Signal Processors Silicon

TMS320VC5409-100,pdf(Fixed-Point Digital Signal Processor)

基于TMS320VC5409 DSP的閃爍存儲器并行引導裝載

基于TMS320VC5409的汽車減震彈簧故障診斷系統

TMS320UC5409和TMS320VC5409數字信號處理器硅勘誤表的詳細概述

TMS320VC5409A定點c

基于TMS320VC5409和EPM7128A芯片實現高速圖像通信系統的設計

基于TMS320VC5409和EPM7128A芯片實現高速圖像通信系統的設計

評論