異步電路所具有的低功耗、低電磁噪聲輻射、高速等突出特點,使其逐漸成為當前設計的焦點。現有異步電路的實現方法往往通過定制的VLSI結構完成,或者設計獨特的異步FPGA結構來實現,而現有基于常規FPGA設計的異步電路,往往難于解決其中的冒險、延遲等問題。

全局異步局部同步[1]GALS(Globally Asynchronous Locally Synchronous)系統,結合了同步設計和異步設計的優點,在解決多時鐘域問題和模塊更新的復用性等方面有巨大優勢,其特點是在各同步模塊需要處理時才工作,其余時間可以處于暫停狀態,不用引入太多異步單元,較易于使用常規FPGA實現,特別是在現有SoC[2]系統中多同步模塊異步互聯方面有著突出優勢,且其具有低功耗、高吞吐量的特點。

參考文獻[3]描述的是一種全局異步局部同步的專用FPGA(GAPLA),其內部結構通過同步邏輯模塊實現數據計算,在邏輯模塊間由同步、異步互換接口完成異步互聯,其關鍵技術是同步、異步互換接口和時鐘暫停(Pausible clocking)電路結構,而在常規FPGA中不包含這些結構。

參考文獻[4]在常規FPGA實現GALS系統,是通過信號狀態轉換圖(STG)的方法設計接口電路,利用Petrify軟件實現的一種GALS系統異步封裝電路,其將接口模塊同步分解成邏輯門電路,容易產生冒險。參考文獻[5]則通過使用帶復位端的D觸發器及延遲單元來完成接口電路的設計,其接口中的延遲單元要求是FPGA內部的標準單元,而在常規FPGA中不包含此標準單元。

本文基于常規FPGA中大量的LUT結構,通過Quartus軟件的邏輯鎖定[6]技術將設計的C單元鎖定在一定區域,保證了C單元的無冒險性,同時建立標準C單元庫。使用C單元實現了GALS系統所需要的延遲電路、接口電路、時鐘暫停[7]電路。利用狀態機設計的計數器作為同步模塊,基于四相單軌握手協議[8],完成兩同步模塊的異步互聯。

1 點對點GALS系統

GALS系統從局部來看各同步模塊獨立設計;從全局來看,各模塊彼此時鐘獨立,以各自工作頻率獨立運行,其互聯通過設計的異步接口完成。且各同步模塊時鐘具有可暫停性,保證不需要數據處理時時鐘不運行的效果,具有低功耗的特點。點對點GALS系統是采用單點同步模塊對應單點通信的方式實現的異步電路。

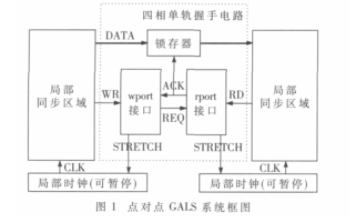

整個結構由三部分組成:局部同步區域、握手區域、時鐘可暫停區域。在同步區域完成的是同步模塊的設計,其同步模塊可更新復用;握手區域通過同步、異步互換接口及鎖存器完成,由兩邊同步模塊發送的WR、RD信號來觸發握手區域進行握手;時鐘可暫停區域由內部產生的時鐘及握手區域輸出的暫停信號(STRETCH)進行時鐘的調整,確保系統的低功耗運行。其組成框圖如圖1所示。

在點對點GALS系統中,設計的重點是接口電路及局部時鐘可暫停模塊,由于不需要引入外部時鐘,所以在全局復位后,時鐘可暫停模塊就應當產生時鐘信號,時鐘信號的頻率根據各同步模塊需求情況設定。在同步模塊的設計中,其既要有數據接收模塊和數據處理模塊,又要產生上級的接收信號(RD)和下級的數據處理完畢信號(WR),以確保電路接連不斷地工作。

2 狀態保持單元的設計

異步電路中為了避免冒險現象的發生,常需要設計一些適合異步電路的狀態保持單元,通常難于設計的就是無冒險的Muller C單元,且其為異步電路的重要組成部分。Muller C標準單元(c_std)的基本功能為:當輸入信號A、B同時為“1”時,輸出S為“1”;當輸入信號A、B同時為“0”時,輸出S為“0”;

當輸入信號A、B處于其他狀態時,輸出保持原信號。從而當輸出信號為“1”時,就能指示輸入信號都為“1”。輸出為“0”的情況同理。

由此可以看出其信號的跳變能夠指示或確認其他信號的跳變情況,這樣就能夠確保電路避免冒險現象的發生。而通過邏輯門設計的C單元,常因內部連線延遲以及門延遲的特性,使得其映射到FPGA內部時會出現冒險現象,因而只有通過建立查找表結構的方式設計C單元,才可使得映射到常規FPGA時避免冒險發生。

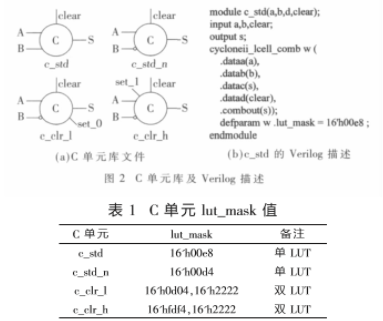

在圖1的GALS系統中使用到的4種標準的C單元,采用Verilog HDL語言編寫,通過編譯生成.QSF文件,利用Logic-Lock技術生成網表文件,通過這三個文件即可建立常規FPGA可調用的無冒險C單元庫。圖2描述的是4種C單元庫文件符號及c_std相應的Verilog描述。在C單元庫中的c_clr_l單元具有置0功能,而c_clr_h具有置1功能。表1列出4種C單元的lut_mask值。

參考文獻[9]使用的是門電路描述的C單元,在EDA軟件對其進行綜合編譯時,容易受到其余同步電路的影響而產生冒險。本文對基于LUT實現的C單元,需要將輸出反饋回輸入的一端,同時使用Quartus軟件的邏輯鎖定(Logic-Lock)方式,將C單元綜合、布局于一定的區域內,可以避免在與其余電路綜合時發生冒險,具有較高實用價值。

3 接口電路及時鐘暫停電路的實現

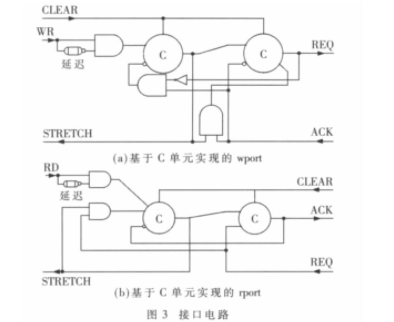

四相單軌握手協議,廣泛應用于時序假設中,通常可以使電路獲得最好的性能。而在控制電路設計中,最簡單的四相單軌握手電路通過一個C門和一個非門組成,即異步電路中常用的Muller流水線[10]。本文采用手工設計方式實現的握手接口電路就是基于Muller流水線的思想,如圖3所示。

圖3(a)實現的wport接口電路,在全局CLEAR信號為高電平時對全局電路進行復位,其輸出REQ、STRETCH信號全為低電平。局部同步模塊產生一個WR信號(即同步模塊處理完畢)時,通過延遲取反相“與”后輸出一個脈沖。當ACK信號為低電平時,左邊的C單元輸出為“1”,即其暫停信號(STRETCH)置為“1”,停止同步模塊時鐘運行,此時由于右邊的C單元的輸入都為“1”,則發出請求信號,完成一次請求;當ACK信號為高電平時,由于右邊C單元的置0位為“1”,從而停止請求,實現了一次四相單軌通信。

圖3(b)中的rport接口電路,在同步模塊發出處理完成信號時,其左邊的C單元置1位輸入是由RD產生的脈沖信號,從而其輸出STRETCH為“1”,即要求同步模塊時鐘停止,在其請求信號REQ為“1”時,ACK輸出為“1”;當REQ為低電位時,由于左邊C單元輸出為低電位,則ACK輸出為“0”,實現了一次四相單軌通信。

結合兩接口電路的四相單軌通信則可實現GALS系統的模塊互聯。對接口電路延遲單元的設計則使用單個標準C單元c_std實現,通過時序約束其延遲量可達到5.125 ns,對整個電路的設計具有較好的延遲效果,且無冒險現象。

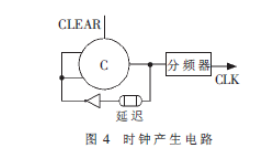

在GALS系統中,有些同步模塊可能沒有自帶的時鐘信號,常需要系統內部產生特定頻率范圍的時鐘信號,所以可暫停時鐘的設計是必須的。實現方法是基于一個C單元及一個延遲單元,以及可隨意調節的分頻器組成,通過C單元設計的時鐘電路可產生頻率高的時鐘。當CLEAR信號置高時,對電路清0,經過延遲取反后,C單元的輸入為1,則輸出即為1,以此類推,則產生時鐘信號。

局部時鐘模塊的實現如圖4所示。通過時序仿真,CLK在未加分頻器的情況下可高達500 MHz以上。由于超過目前FPGA的最高時鐘,從而其需要通過分頻來達到設計要求。此時鐘電路根據同步模塊需求,頻率可進行任意調節,具有較大實用性。

4 GALS系統實現及測試

為了測試由FPGA實現的四相單軌握手協議電路的性能,通過狀態機設計無冒險的計數器作為GALS系統兩端的同步電路,采用Altera公司CycloneⅡEP2C35F6-

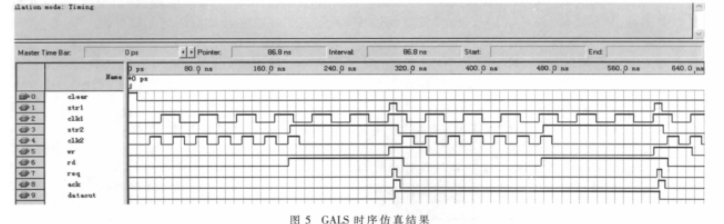

72C6器件作為測試器件,通過邏輯鎖定技術將標準C單元模塊添加進設計中,通過建立wport、rport的父區域(Parent Region)鎖定模塊,將子區域(Child Region)鎖定的C單元添加進父區域鎖定模塊,保證了各自時序的獨立性,確保了電路功能的實現。其時序仿真結果如圖5所示。

對結果進行分析:當全局復位信號為高電平時,對全局電路進行復位。整個握手實現過程通過同步模塊的2個計數器在進位時,輸出各自的進位信號作為wr和rd信號,當二者同時為高電平時發生握手,且作為接口電路rport、wport的輸入信號。當req上升沿到來時,ack響應req信號變為高;

當req下降沿到來時,ack拉低。通過ack的上升沿觸發鎖存器傳遞數據,完成數據的通信,其數據主要是由計數器產生的0、1信號。而對于時鐘暫停模塊,當str1、str2信號為高電平時分別對兩個模塊的時鐘進行暫停,從仿真圖中可見,當兩者為高電平時,將時鐘置為0,保證了時鐘的可暫停。

整個系統通過設計的C單元庫,實現了GALS中的接口模塊、時鐘暫停模塊,達到GALS系統同步模塊間異步互聯的效果,且使用的是四相單軌握手協議,具有較好的握手性能。使用Quartus軟件的邏輯鎖定技術,對子區域(C單元)、父區域(接口電路)進行鎖定,確保了C單元在與整個電路綜合中不出現冒險問題,確保了電路的可行性。對在常規FPGA中實現異步電路帶來新的開發特性,特別對SoC的異步互聯具有較好的實用價值。

編輯:jq

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606064 -

soc

+關注

關注

38文章

4204瀏覽量

219113 -

同步電路

+關注

關注

1文章

60瀏覽量

13350 -

CLK

+關注

關注

0文章

127瀏覽量

17236

發布評論請先 登錄

相關推薦

關于FPGA的全局異步局部同步四相單軌握手協議實現

關于FPGA的全局異步局部同步四相單軌握手協議實現

評論