在 FPGA 設計進程中,時序收斂無疑是一項艱巨的任務。低估這項任務的復雜性常常導致工作規劃面臨無休止的壓力。賽靈思提供了諸多工具,用于幫助縮短時序收斂所需時間,從而加速產品上市。本篇博文描述了一種方法,能夠有效減少時序路徑問題分析所需工作量。

時序路徑問題分析定義為通過調查一條或多條具有負裕量的時序路徑來判斷達成時序收斂的方法。當設計無法達成時序收斂時,作為分析步驟的第一步,不應對個別時序路徑進行詳細時序分析。應首先從系統角度來分析設計,以判定是否有任何因素會對設計中較大區域產生影響,而不只是判定有哪些因素會影響存在最嚴重違例的個別路徑。

如需獲取有關此過程的實用指南,請參閱《UltraFast 設計方法時序收斂快捷參考指南》(UG1292)。

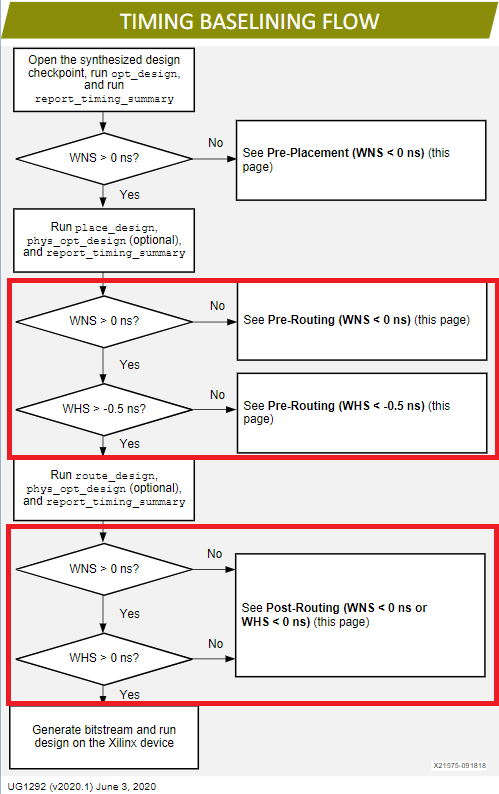

本篇博文旨在描述此文檔中所述的時序基線檢查流程,尤其是當 WNS 《 0ns 或 WHS 《 -.5ns 時的布局后操作以及當 WNS 《 0ns 或 WHS 《 0ns 時的布線后操作(紅圈部分)。

為了解決這些時序收斂失敗問題,用戶可以采用時序路徑分析方法來對布局步驟、phys_opt 步驟和布線實現步驟之后發生的時序收斂失敗問題進行優先級排序。

第一步是使用下列命令生成一組報告。

在 Vivado 非工程模式下,可將這些命令添加到用于運行此流程的 Tcl 腳本中。在 Vivado 工程模式下,則可將這些命令添加到 Tcl 掛鉤腳本中(請參閱 (UG894) 的 “定義 Tcl 掛鉤腳本” 部分)。

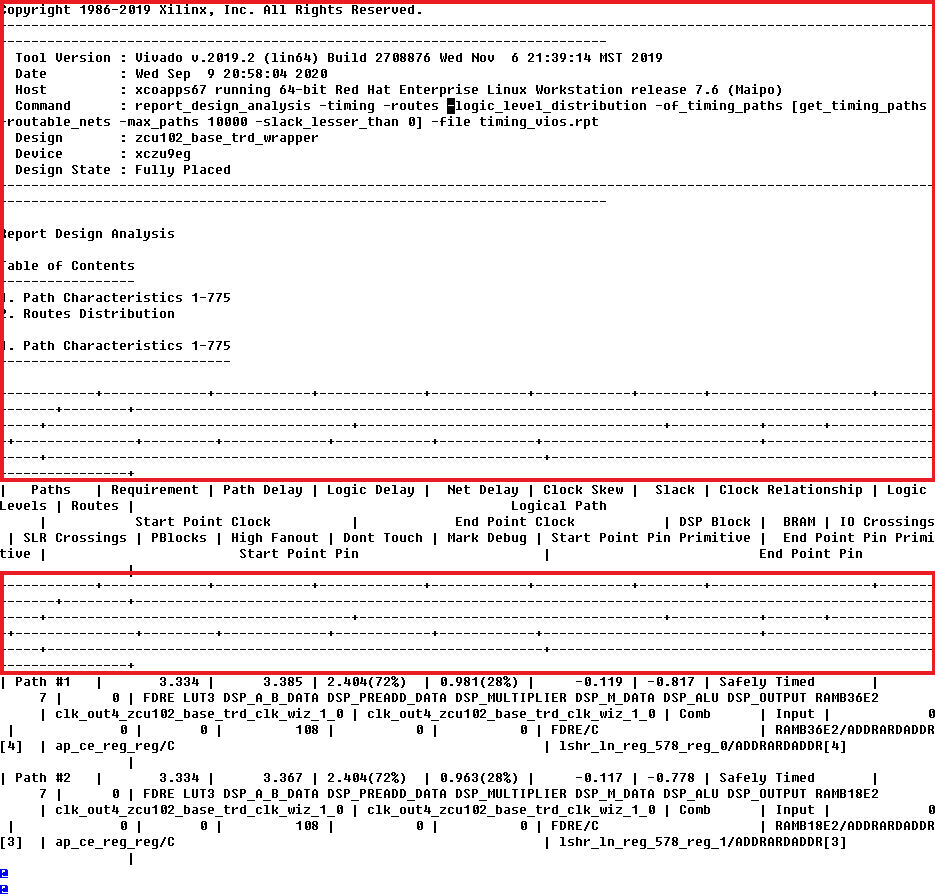

report_design_analysis -timing -routes -logic_level_distribution -of_timing_paths [get_timing_paths -routable_nets -max_paths 10000 -slack_lesser_than 0] -file timing_vios.rpt

report_timing -of [get_timing_paths -routable_nets -max_paths 1000 -slack_lesser_than 0] -file timing_paths.rpt -rpx timing_paths.rpx

這些命令會生成文本報告 timing_vios.rpt 和 timing_paths.rpt,這些報告可通過任意文本編輯器來查看。這些命令還可生成交互報告 timing_paths.rpx,此報告可用于在 Vivado GUI 中進行交叉探測。這些報告可顯示有關設計中時序收斂失敗的主要路徑的信息。通過將這些報告結合在一起,即可快速達成時序收斂。

timing_vios.rpt

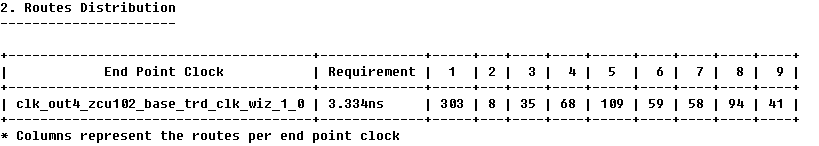

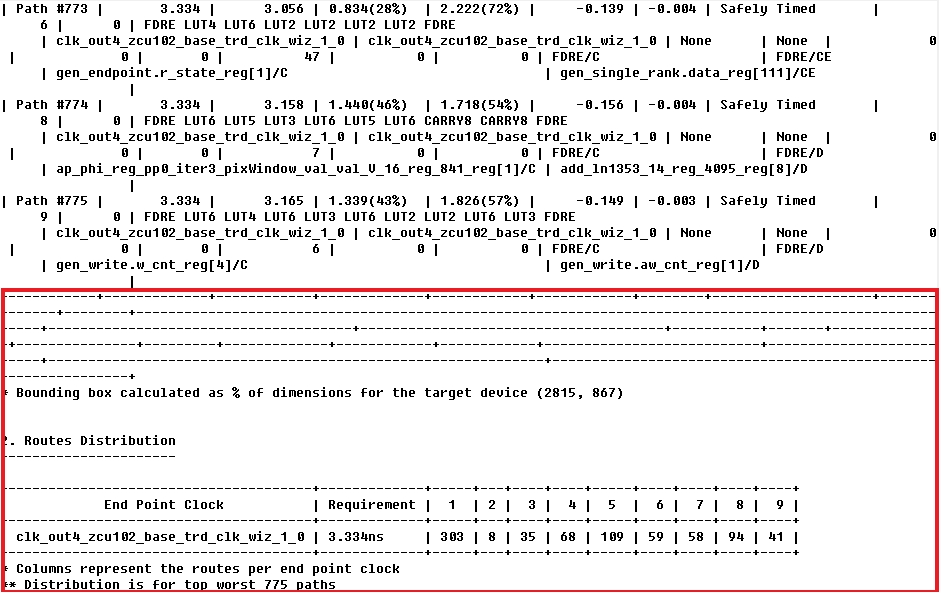

此報告可顯示時序收斂失敗的主要路徑的屬性(根據 Tcl 參數設置,最多可報告 10,000 條路徑)。報告底部顯示的直方圖可顯示每個端點時鐘對應的時序失敗的路徑數量,按邏輯級別分組。此直方圖作為非常實用的高級視圖,可幫助縮小造成最嚴重的時序收斂失敗的時鐘域的范圍。

用戶應首先從造成最嚴重違例的時鐘域開始分析這些失敗問題。在多 SLR 器件中,許多違例所含的邏輯級數為 0,這表示導致時序違例的根本原因可能是沒有足夠的流水打拍,或者 SLR 分區效果不良。

這些都只是時序失敗的線索,而并非真正原因。重要的是首先縮小問題最嚴重的區域的范圍,然后再尋找解決方案。了解最差負時序裕量時序違例的本質有助于用戶確定應執行的補救步驟的優先順序。以下顯示了一個簡單的直方圖示例(僅有 1 個時鐘存在時序收斂失敗路徑)。

報告其余部分可通過文本編輯器來讀取,但由于換行,可能導致難以閱讀。更簡單的數據分析方法是將其導入 Microsoft Excel。 以下過程用于將文本編輯器報告轉換為逗號分隔式報告。

1. 創建 timing_vios.rpt 的副本,并將其重命名為 timing_vios.csv。

2. 使用文本編輯器,移除報告中的頁眉、頁眉分隔符行和頁腳(如下紅框所示):

3. 如果已將 -show_all 選項與 report_design_analysis Tcl 命令配合使用,請將文件中的逗號 (,) 替換為冒號 (:)。

4. 將所有管道字符 (|) 都替換為逗號 (,),然后保存此文件。

5. 關閉文件。

timing_vios.rpt 頂部

timing_vios.rpt 底部

6. 在 Microsoft Excel 中打開此 csv 文件。

7. 移除 A 列,因為此列為空。

8. 在頂部插入空白行。

9. 添加以下等式,以在報告中生成未經篩選的裕量百分比。此百分比將有助于指導完成分析操作。此百分比值越大,則失敗特征對時序的影響越大。

=SUBTOTAL(109,G:G)/SUM(G:G)*100

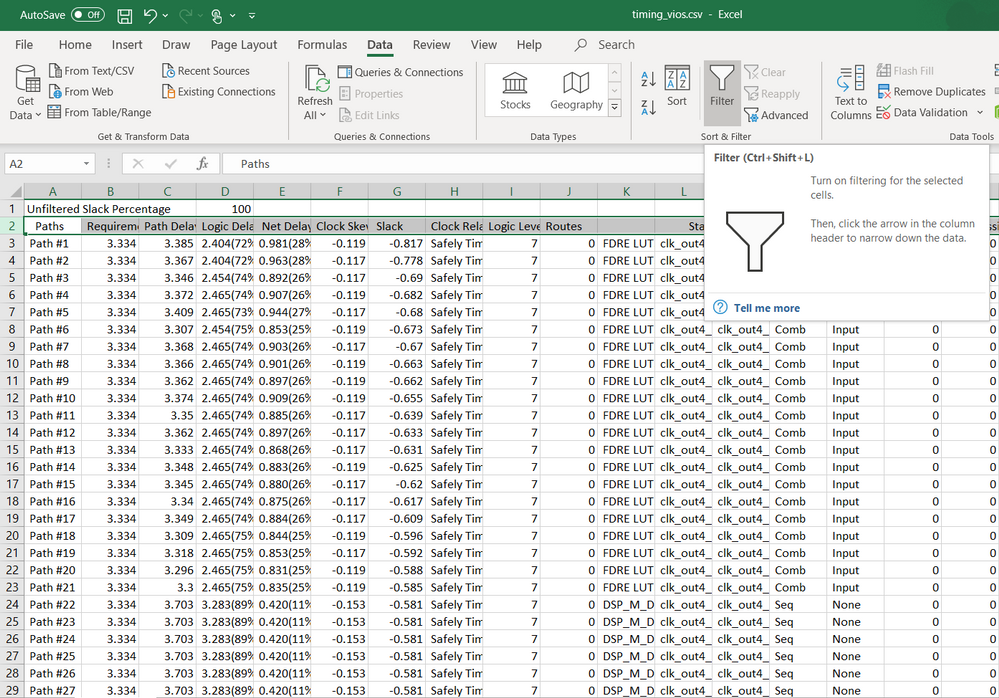

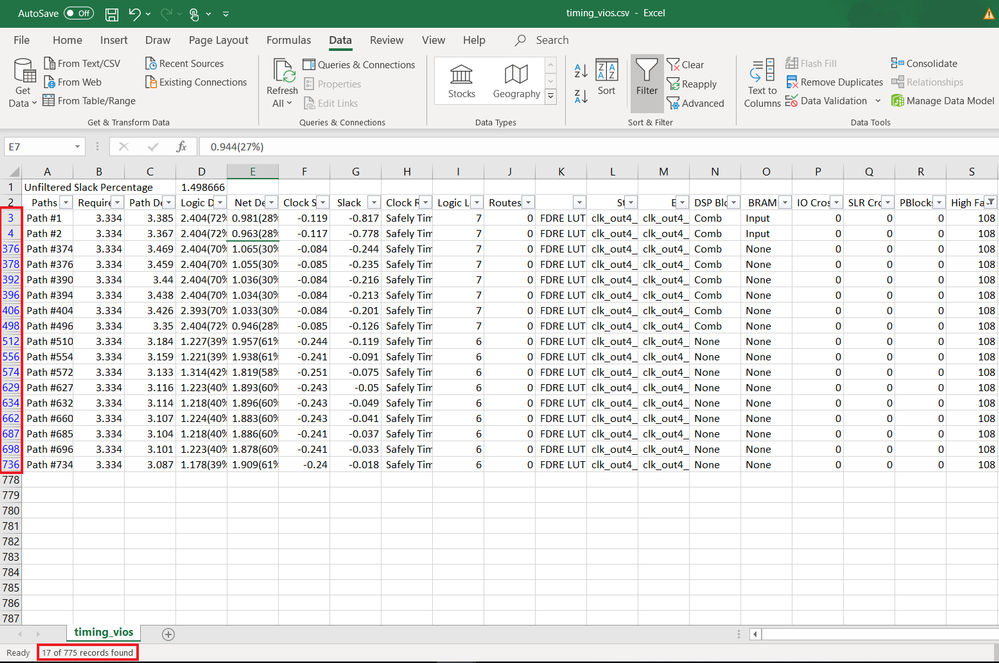

10. 高亮 excel 文檔的第 2 行,該行應為各列的標題行,然后選擇“數據 (Data) -》 篩選 (Filter)”。

對此報告使用篩選,以查找對設計影響最大的失敗類型。

此報告通常本身無法提供時序失敗的準確原因,但可幫助指導用戶發現需進一步調查的路徑,并使用交互時序報告(timing_paths.rpx;稍后將提供此報告的實用技巧)進行調查。

通過篩選,用戶即可看到具有相似屬性(邏輯級數、起點管腳等)的相似失敗路徑(例如,同一條總線的路徑)。用戶可以使用未篩選的裕量百分比來指導他們。并且,用戶還可通過篩選來使用發現的記錄行(如下所示),并留意篩選后顯示的行號(電子表格中行號越小,表示顯示的時序收斂失敗的路徑越差)。

以下是一些有關篩選的實用技巧。

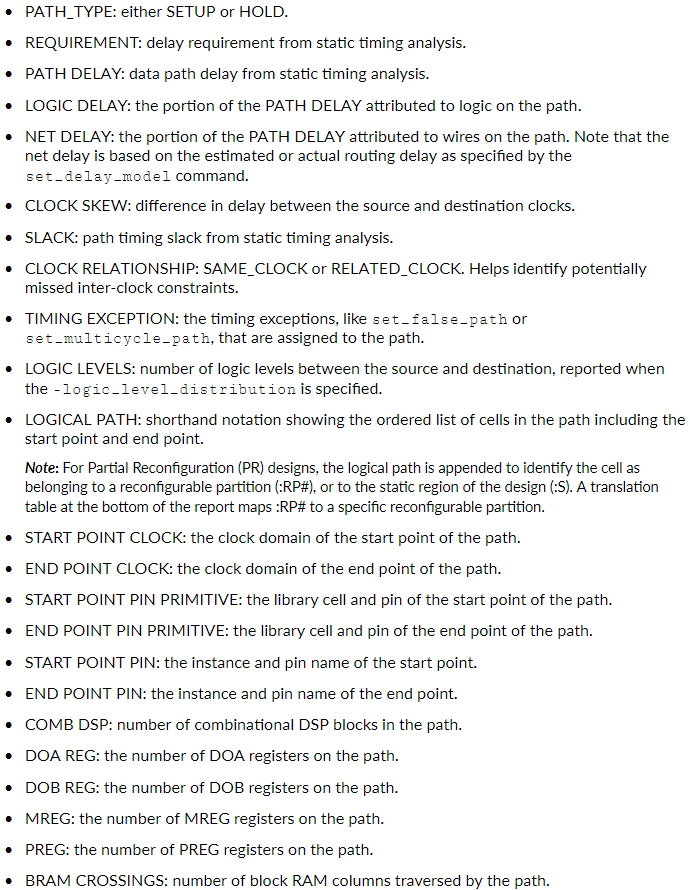

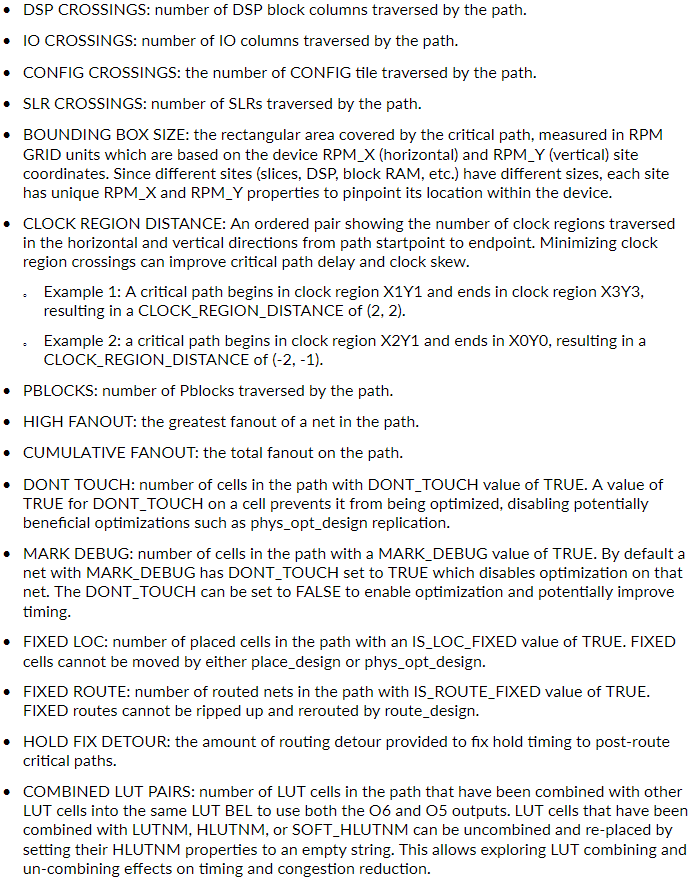

“文本篩選器 (Text Filters) -》 包含 (Contains)”對于篩選“起點管腳 (Start Point Pin)”、“終點管腳 (End Point Pin)”和“邏輯路徑 (Logical Path)”很有用。在 timing_vios.csv 中包含以下列(定義源自 (UG835) v2020.1 第 1324-1325 頁)。

首次生成電子表格時,可根據以下入門指南來嘗試執行下列檢查。這些檢查主要聚焦于講解設計后的時序收斂失敗原因和修復方法。設計師還可以選擇更改硬件描述語言 (HDL) 以縮短路徑長度或者降低時鐘速率,以及運用下文未列出的其它修復方法:

1. 在時鐘關系 (CLOCK RELATIONSHIP) 列中,是否所有時序收斂失敗的路徑都已安全完成時序約束?如果沒有,那么時序約束對于其它路徑是否合適?

2. 是否有任何時序收斂失敗的路徑的時鐘偏差 》 .5ns?如果存在此類路徑,請參閱 (UG1292) v2020.1 第 8 頁,以獲取相關偏差建議。

3. 對于 SSI 器件,跨 SLR 的路徑的未篩選的裕量百分比為多少?如果此比值過高,請參閱(UG1292) v2020.1 第 7 頁。

4. 有多少時序收斂失敗的路徑具有與之關聯 Pblock?如果此比值較高,請參閱 (UG1292) v2020.1 第 7 頁。

5. 是否有大量時序收斂失敗的路徑的扇出都偏高 (》=512)?在 (UG1292) v2020.1 第 6 頁中,如果工具存在較大的信號線延遲,則建議對具有 512 個端點的高扇出信號線進行最優化。

6. 是否有任何時序收斂失敗的路徑具有 DONT_TOUCH 或 MARK_DEBUG?包含這些時序路徑的邏輯是否屬于非第三方邏輯或非賽靈思 IP?

這些屬性會阻礙工具執行有助于改善時序的最優化操作。

7. 有多少比例的路徑所含的起點管腳原語或端點管腳原語不屬于寄存器類型(非 FDPE、FDCE、FDRE 或 FDSE)?是否存在類似的失敗特征?

8. 對于布線后操作,包含非零保持時間繞行 (HOLD FIX DETOUR) 的時序路徑所占比例為多少?

timing_paths.rpt

這是基于文本的時序分析報告,包含對應設計中的主要時序收斂失敗路徑(根據 Tcl 命令參數,最多可包含 1000 條路徑)的時序分析。它可通過使用簡單的 Linux grep 來幫助生成前 1000 條路徑的失敗源和目標列表。 例如,用戶可以按如下方式來識別排名前 100 的時序起點和端點。

grep -m 10 “Source:” place_paths.rpt 》 top_100_startpoints.rpt

grep -m 10 “Destination:” place_paths.rpt 》 top_100_endpoints.rpt

timing_paths.rpx

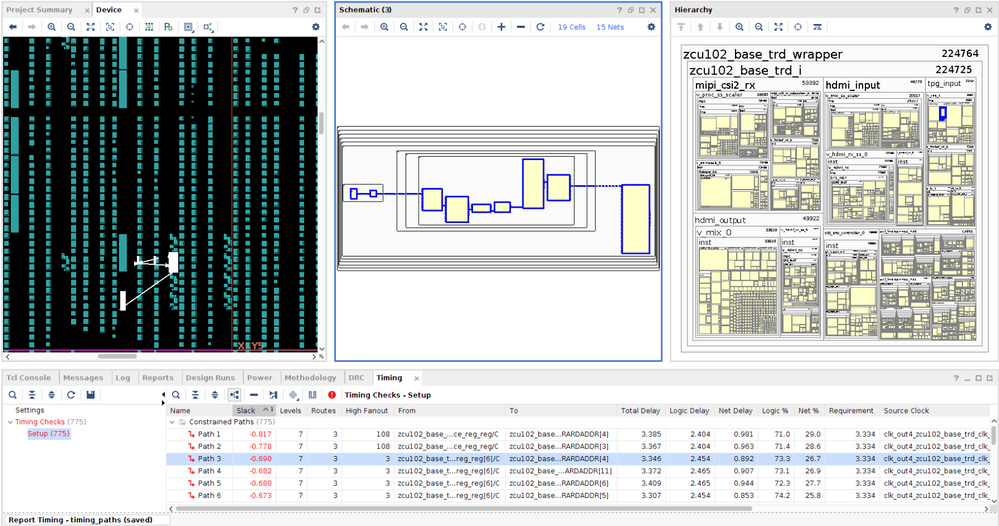

這是 timing_paths.rpt 的交互式報告版本。最實用的 3 個窗口分別是“器件 (Device)”窗口、“層級 (Hierarchy)”窗口和“原理圖 (schematic)”窗口。

一旦確定某個失敗特征對于設計的時序影響較大,即可使用 timing_paths.rpx 報告來對其進行深入挖掘。用戶通過在 Vivado 中使用 timing_paths.rpx 報告即可借助具有失敗特征的主要失敗路徑來判定出現時序收斂失敗特征的原因。

要查看 timing_path.rpt 中包含的每條路徑的信息,請在 Vivado 交互式報告中雙擊相應的時序路徑。這樣即可顯示路徑報告匯總信息窗口,其中包含時鐘和數據路徑等路徑信息。查看原理圖中的路徑是很有用的。通過使用原理圖,即可查看有哪些時鐘被用作為數據路徑中的時序元件的時鐘源。在原理圖中還能同時展開此時序收斂失敗路徑的前后級路徑,這些信息有助于更準確了解數據路徑。

此外,還可查看原理圖中的單元屬性、信號線屬性和管腳屬性,因為原理圖可顯示時序收斂失敗的路徑附近的固定布局單元(例如,收發器)或受限布局單元(例如,塊存儲器)。

用戶還可高亮時序報告中的路徑,這樣即可在“Hierarchy”窗口中高亮相應的模塊。如果用戶選擇前 10、100 或 1000 條路徑,則可查看收斂失敗的時序路徑是否集中于層級內某一部分。已知路徑在層級中所在位置有助于將時序收斂工作重心集中于明確設計的某一區域內包含較多違例的原因。

最后,用戶可以在時序報告中將路徑高亮,這些路徑也會顯示在“Device”窗口中,以顯示物理器件中邏輯的布局位置(如下所示)。

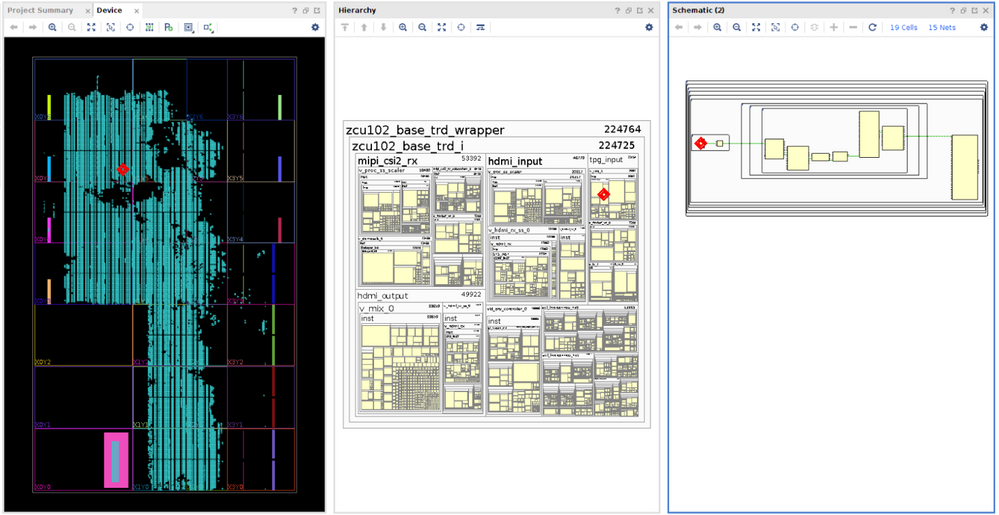

通過使用“Schematic”窗口,即可在時序路徑內標記單元以幫助用戶在“Schematic”窗口、“Hierarchy” 窗口和 “Device”窗口之間進行瀏覽(如下所示)。

將構建模塊放置在一起

本篇博文提供了一種時序路徑分析優先排序方法,此方法可在 (UG1292) 的時序基線檢查流程中使用。

本篇博文中涵蓋了下列話題:

1. 如何為此時序分析生成重要報告(timing_vios.rpt 和 timing_paths.rpx)。

2. timing_vios.rpt 的分析過程包括將其轉換為便于分析的 Excel 格式 (timing_vios.csv)。

3. 使用timing_paths.rpx 來幫助確定時序收斂失敗的原因。

在發生時序收斂失敗的大型設計中,用戶將在 2 份報告之間進行迭代(timing_vios.csv 和 timing_paths.rpx)。timing_vios.csv 報告提供了失敗的高級別視圖(例如,森林級視圖)。timing_paths.rpx 報告包含 “Schematic” 窗口、“Device” 窗口和路徑報告,可提供各條路徑的具體信息(例如,單獨的樹視圖)。

您可反復切換回 timing_vios.csv 以查看共有的失敗特征。即使大偵探面對千頭萬緒也可能一籌莫展,負裕量最高的路徑也可能無法輕易解釋其時序收斂失敗原因。如果發生這種情況,那么應分析負裕量僅次于它的另一組時序路徑,查看其失敗原因。

這樣做的目的是通過明確最常見的時序收斂失敗的原因來盡可能快速使工作取得進展。希望能夠藉此加快達成時序收斂,少受殫精竭慮之苦。

祝狩獵愉快!

文中提到的 User Guide 可復制如下網址進行查閱:

UG894: https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/ug894-vivado-tcl-scripting.pdf

UG835: https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/ug835-vivado-tcl-commands.pdf

UG1292: https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/c_ug1292-ultrafast-timing-closure-quick-reference.pdf

編輯:jq

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606037 -

TCL

+關注

關注

10文章

1742瀏覽量

88879 -

編輯器

+關注

關注

1文章

806瀏覽量

31293 -

SSI

+關注

關注

0文章

38瀏覽量

19302

原文標題:開發者分享 | 時序路徑分析提速

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電源時序器跳閘的原因和解決方法

鎖存器的基本輸出時序

時序邏輯電路故障分析

時序邏輯電路的功能表示方法有哪些

電源時序器的電壓顯示功能

FPGA 高級設計:時序分析和收斂

求助,求大神幫忙解答下AN65974同步Slave FIFO的讀時序

Xilinx FPGA編程技巧之常用時序約束詳解

FPGA工程的時序約束實踐案例

全面解讀時序路徑分析提速

全面解讀時序路徑分析提速

評論