學習內容

近期設計需要用到AXI總線的IP,所以就對應常用的IP進行簡要的說明,本文主要對AXI互聯IP進行介紹。

基礎架構IP

基礎的IP是用于幫助組裝系統的構建塊。基礎架構IP往往是一個通用IP,它使用通用的AXI4接口在系統中移動或轉換數據,而不解釋數據。

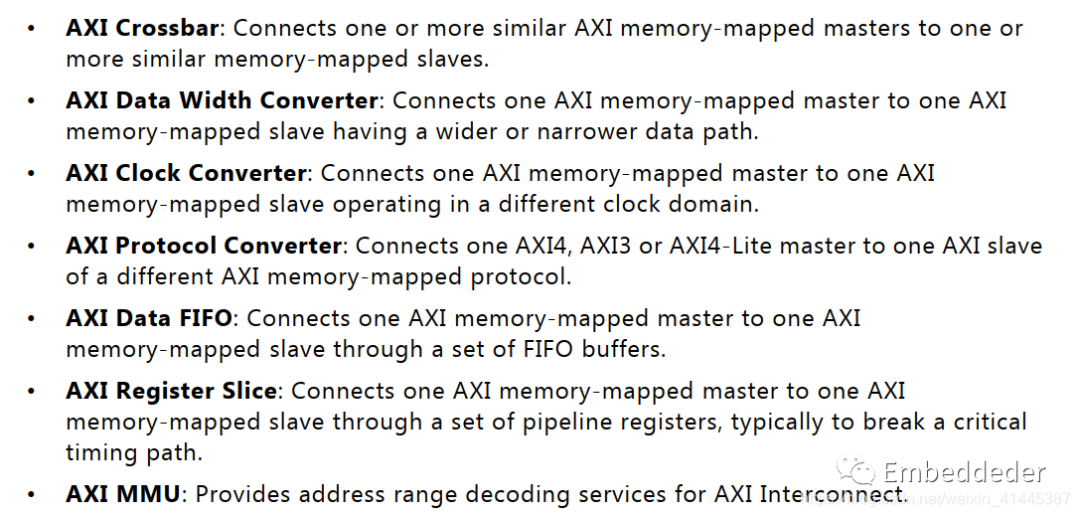

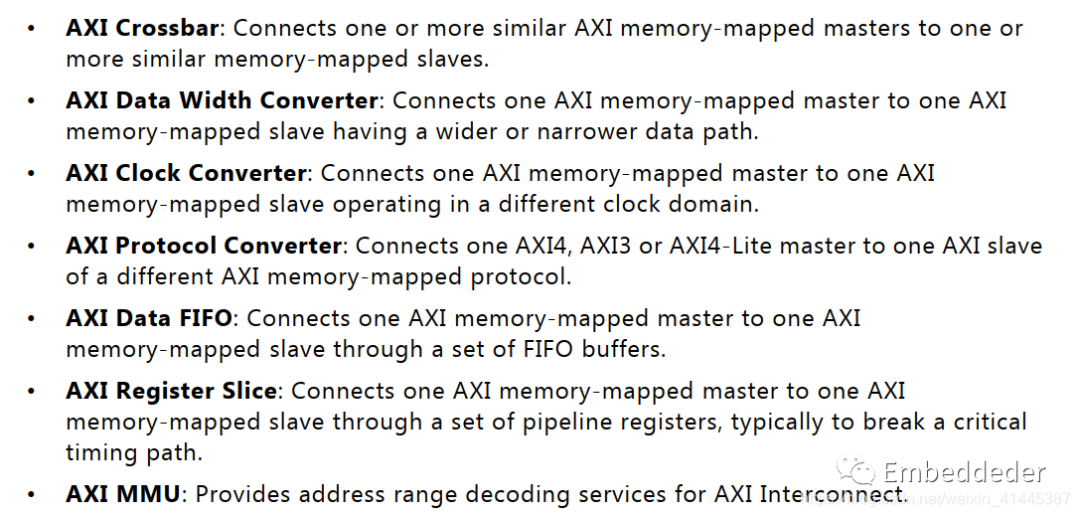

這些基礎的IP各自有自己的常用的功能,下面列舉出一部分AXI接口的基礎構架IP。

° AXI Register slices (for pipelining)用于流水線操作。° AXI FIFOs (for buffering/clock conversion)用于緩存和時鐘轉換。° AXI Interconnect IP and AXI SmartConnect IP (for connecting memory-mapped IP together)用于連接存儲器映射的IP互連。

° AXI Direct Memory Access (DMA) engines (for memory-mapped to stream conversion)用于存儲器映射和數據流接口的轉換。° AXI Performance Monitors and Protocol Checkers (for analysis and debug)用于分析仿真。° AXI Verification IP (for simulation-based verification and performance analysis) 用于仿真驗證。

Xilinx AXI SmartConnect IP and AXI Interconnect IP(AXI互聯IP)介紹

Xilinx AXI Interconnect IP和AXI SmartConnect IP都可以將一個或多個AXI存儲器映射的主設備連接到一個或多個存儲器映射的從設備。而使用AXI SmartConnect IP,更緊密地集成到Vivado設計環境中,用戶以最小的用戶干預自動配置和適應已連接的AXI主從IP。AXI互聯IP(AXI SmartConnect IP and AXI Interconnect IP)可以用于所有的存儲器映射設計中。

在某些情況下,對于高帶寬應用程序,使用SmartConnect IP可以提供更好的優化。AXI SmartConnect IP通過綜合針對重要接口進行優化的低區域自定義互連,在低延遲下提供最大的系統吞吐量。

AXI Interconnect IP(axi_interconnect)可以將一個或多個AXI存儲器映射的主設備連接到一個或多個存儲器映射的從設備。Interconnect 相對于SmartConnect IP更符合來自ARM的AMBA AXI4規范,包括AXI4-Lite 接口。

AXI Interconnect IP和AXI SmartConnect IP僅用于存儲器映射傳輸。AXI4-Stream傳輸不適用。但可以使用AXI4-Stream Interconnect IP (axis_interconnect)。帶有AXI4-Stream接口的IP通常彼此連接到DMA IP或者AXI4-Stream Interconnect IP上。

綜上:對于中到高性能設計,推薦使用AXI SmartConnect IP,因為它在面積和時間上提供了更好的向上擴展。對于低性能(AX14-Lite)或中小型復雜性設計,AXI Interconnect IP可能更有效的面積。

AXI Interconnect IP使用方式

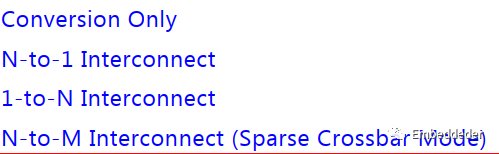

對于互聯IP的使用,在xilinx的指導手冊中提到了下述四種方式。

1. Conversion Only(僅轉換操作)

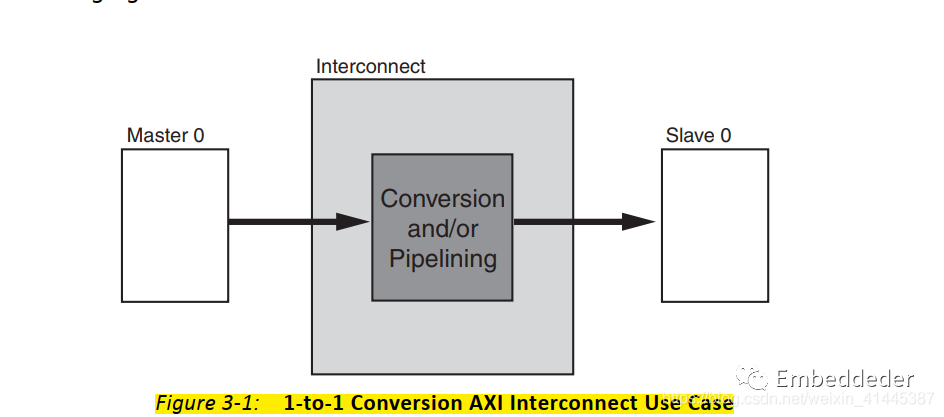

當一個主設備連接到一個從設備時,AXI Interconnect IP可以執行各種轉換和流水線功能。這些操作如下述:

數據寬度轉換

時鐘速率轉換

AXI4-Lite從機自適配

AXI4-3從機自適配

流水線,如寄存器或數據通道FIFO操作。

在這些情況下,AXI Interconnect IP不包含仲裁、解碼或路由等邏輯。可能會導致延遲,延遲大小取決于正在執行的轉換類型。

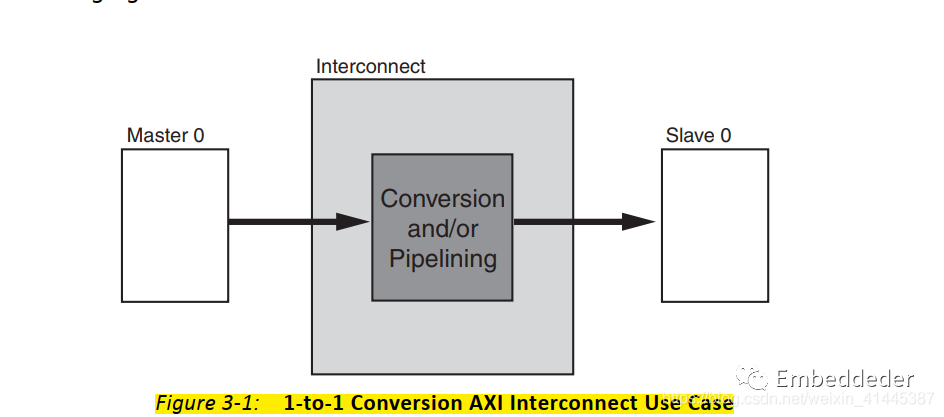

下圖顯示了一個轉換的示例:

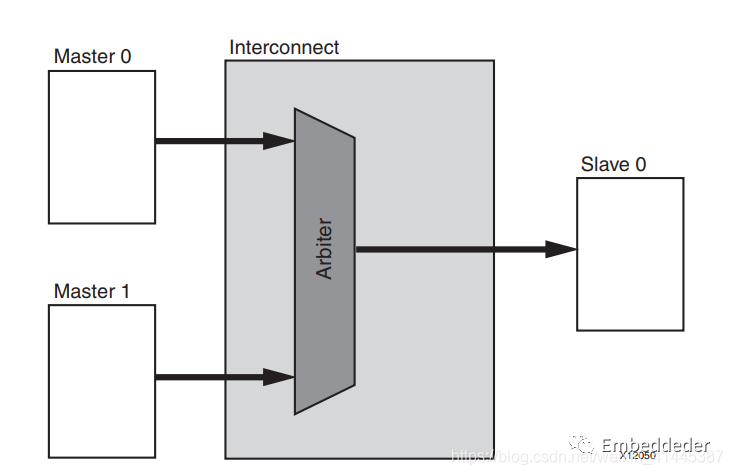

2. N-to-1 Interconnect

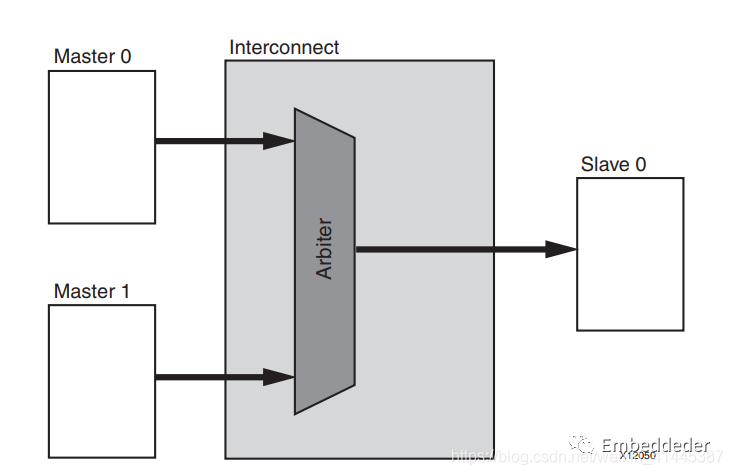

AXI Interconnect IP的一個常見退化配置(或者我翻譯為簡化配置)是多個主設備為訪問一個從設備(通常是一個內存控制器)進行仲裁。在這些情況下,地址解碼邏輯可能是不必要的,并且在AXI Interconnect IP被省略(除非需要地址范圍驗證)。在這種配置下,還可以執行數據寬度和時鐘速率轉換等轉換功能。N-to-1 AXI互聯示例如下圖所示:

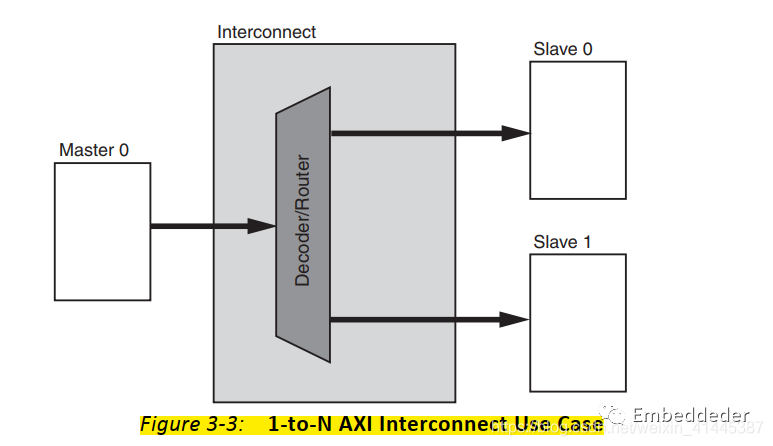

3. 1-to-N Interconnect

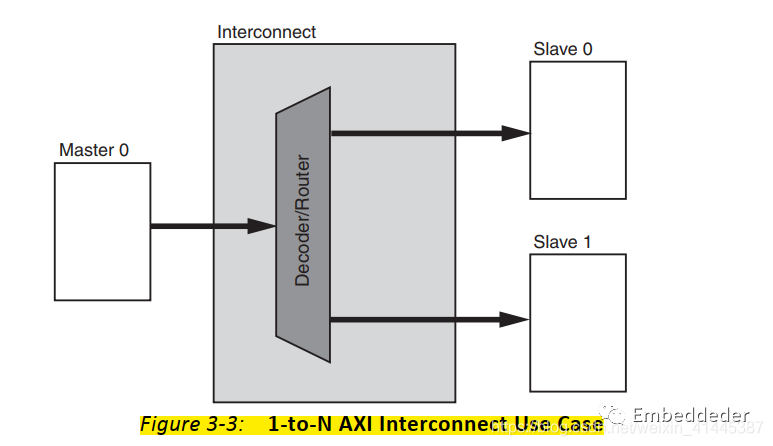

AXI Interconnect IP的另一種退化配置(簡化配置)是當一個主設備(通常是一個處理器)訪問多個內存映射的從外圍設備時。在這些情況下,仲裁(在地址和寫數據路徑)不執行。1 - N互聯示例如下圖所示:

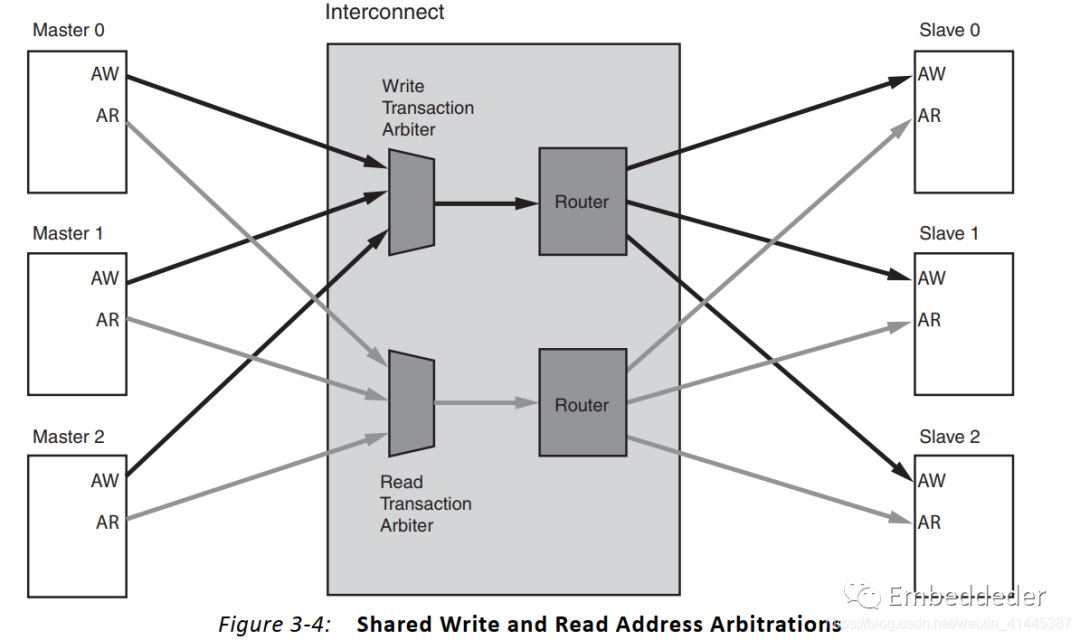

4. N-to-M Interconnect (Sparse Crossbar Mode)

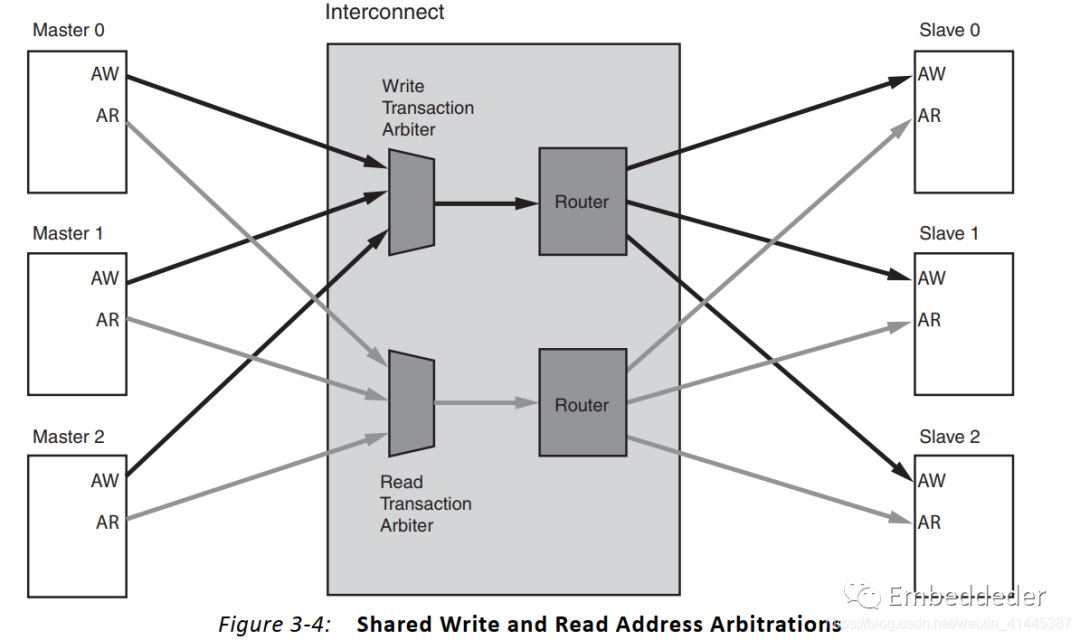

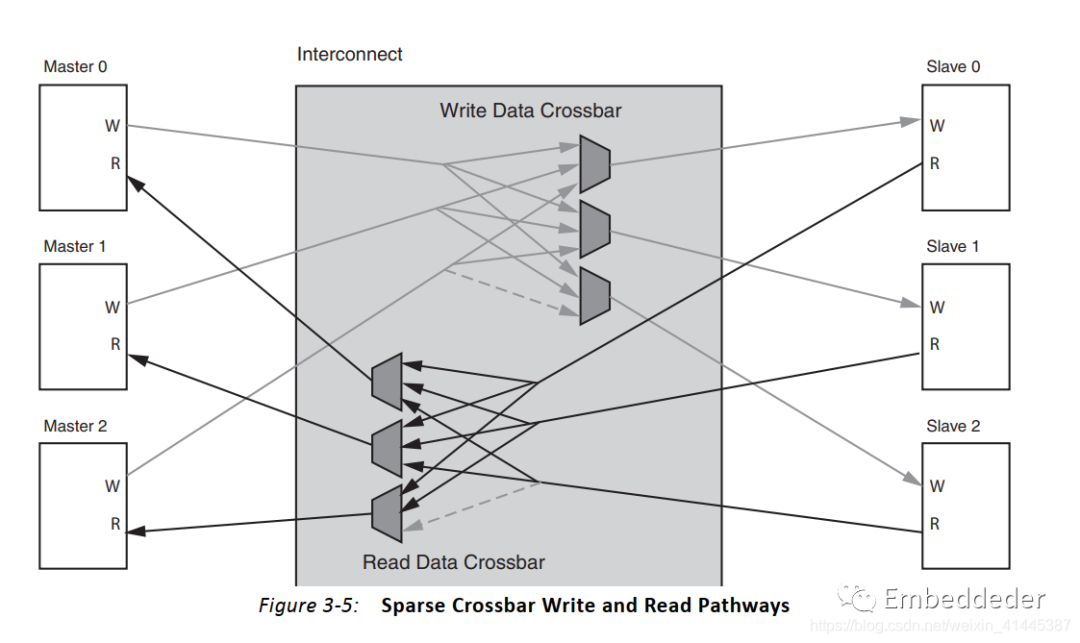

AXI Interconnect的N-to-M用例采用共享地址多數據(SAMD)拓撲,稀疏數據交叉連接,單線程寫和讀地址仲裁,如下圖所示:

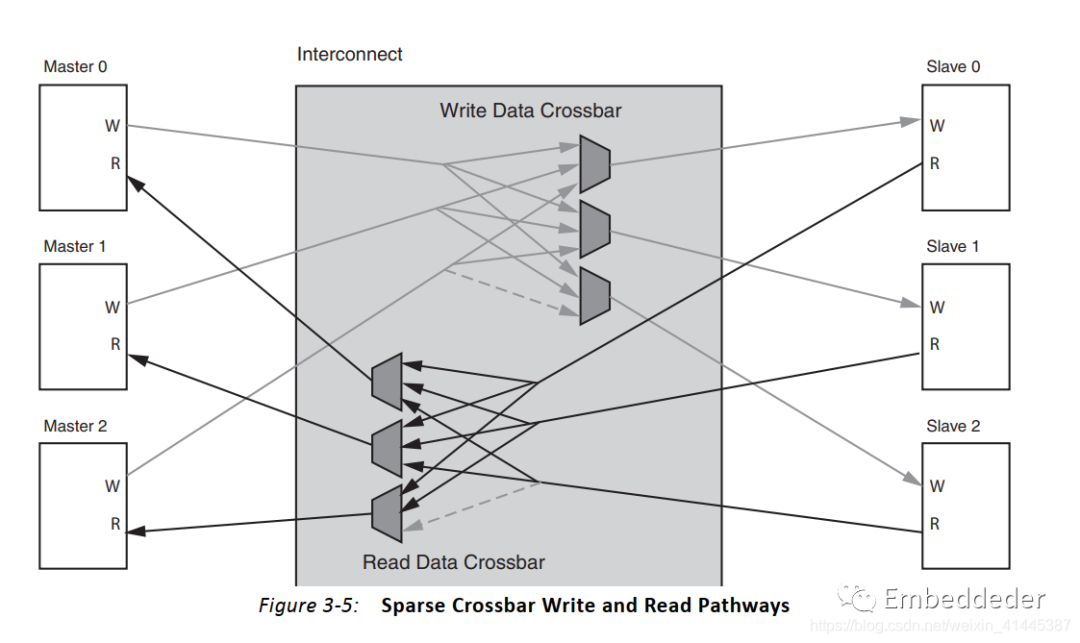

下圖展示了稀疏交叉寫和讀數據路徑:

根據配置的稀疏連接映射,并行寫和讀數據通道將每個SI插槽(連接到左邊的AXI主機上)連接到它可以訪問的所有MI插槽(連接到右邊的AXI從機上)。當多個源有數據要發送到不同的目的地時,只要滿足AXI排序規則,數據傳輸就可以獨立并發地進行。在所有SI槽(如果> 1)中的寫地址通道饋送到一個中心地址仲裁器,它一次授予對一個SI槽的訪問權,對于讀地址通道也是如此。

AXI4-Stream Interconnect Core IP介紹

AXI4-Stream Interconnect Core IP(axis_interconnect)將一個或多個AXI4-Stream主設備連接到一個或多個AXI4-Stream從設備。AXI4-Stream Interconnect Core IP 僅用于AXI4-Stream 傳輸;AXI4存儲器映射傳輸不適用。

AXI4-Stream Interconnect Core 內部框圖

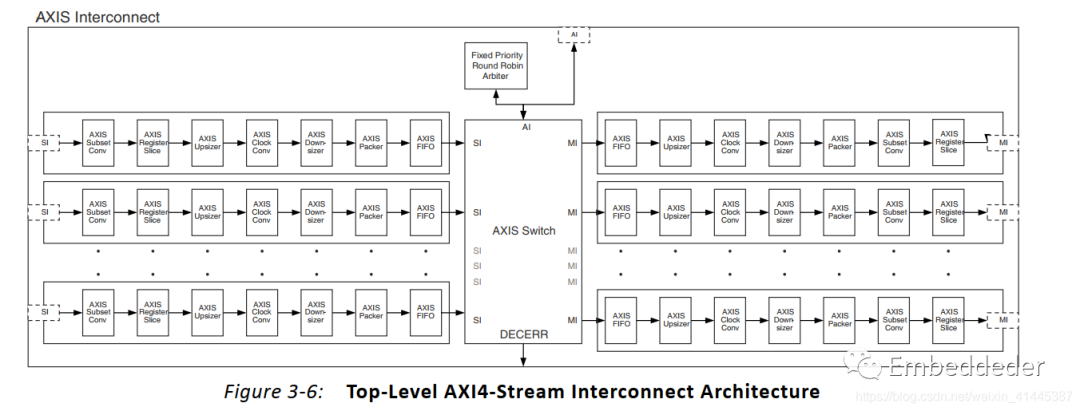

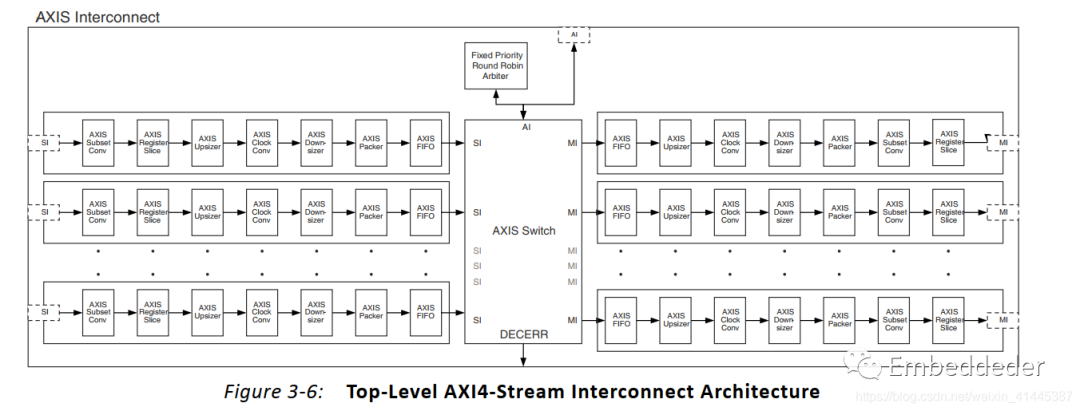

AXI4-Stream Interconnect Core IP由SI、MI和包括它們之間的AXI通道的功能單元組成。

SI接受來自連接的主設備的事務請求。

MI向從設備發送事務。

在中心是交換機,它仲裁和路由連接到SI和MI的各種設備之間的通信。

AXI4-Stream Interconnect Core IP還包括位于交換機和每個SI和MI接口之間的其他功能單元,可選擇性地執行各種轉換和存儲功能。該開關有效地將AXI4-Stream Interconnect Core IP從SI相關功能單元(SI半球)和MI相關單元(MI半球)中間分開。這個架構類似于AXI Interconnect IP的架構。

AXI4-Stream Interconnect IP使用方式

AXI4-Stream Interconnect IP將一個或多個AXI4-Stream主設備連接到一個或多個AXI4-Stream從設備。對于AXI4-Stream Interconnect IP,主要有兩種使用方式:

流數據路由和交換

流多路復用和去多路復用

Streaming Data Routing and Switching (Crossbar Mode)流數據路由和交換

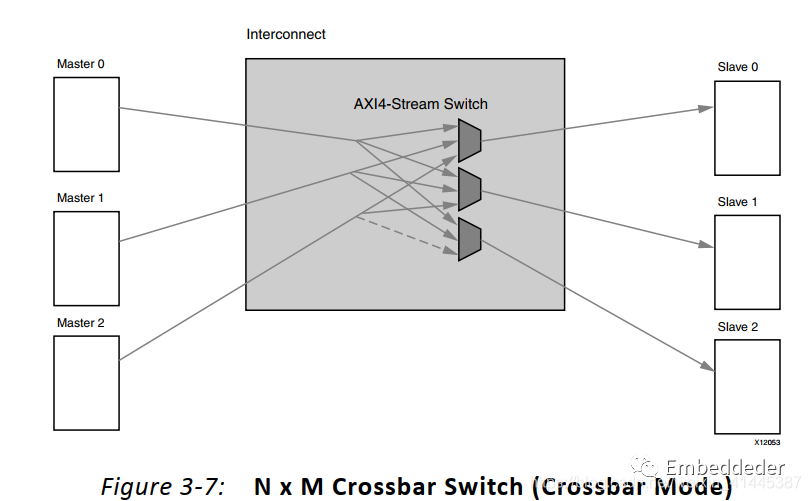

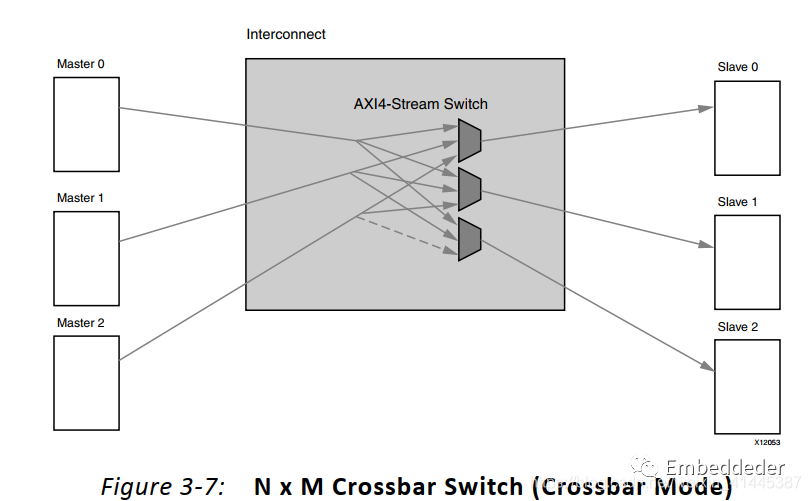

ax14流互連可以實現N × M全交叉開關,如下圖所示。它支持從端仲裁,能夠在N個主服務器和M個從服務器之間并行數據傳輸。解碼器和仲裁者服務于主從之間的路由數據傳輸交互。

Stream Multiplexing and De-multiplexing(流多路復用和去多路復用)

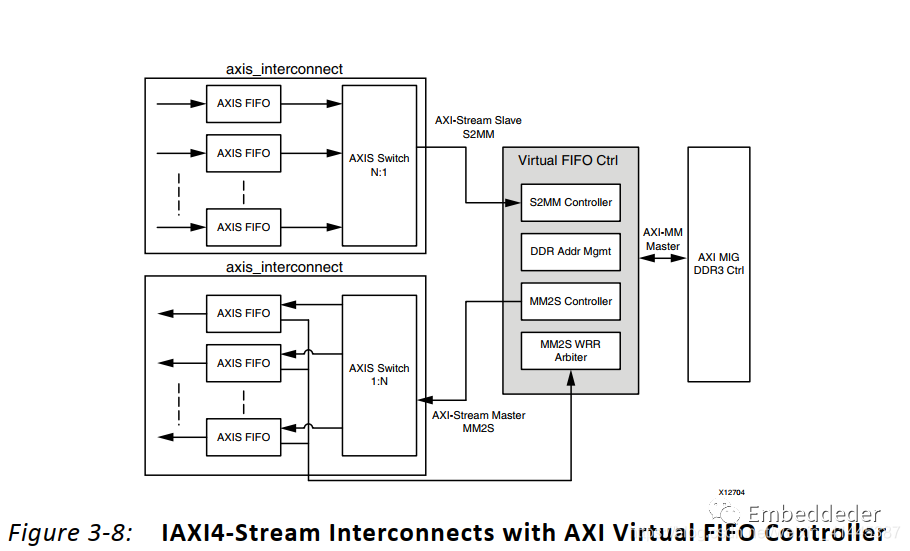

你可以在Nx1配置中將AXI4-Stream Interconnect IP配置為一起多路傳輸流,然后配置為1xM來解多路傳輸流。使用多路復用和多路復用解復用來創建多通道流,其中較小數量的導線可以攜帶來自多個主從的共享流量。

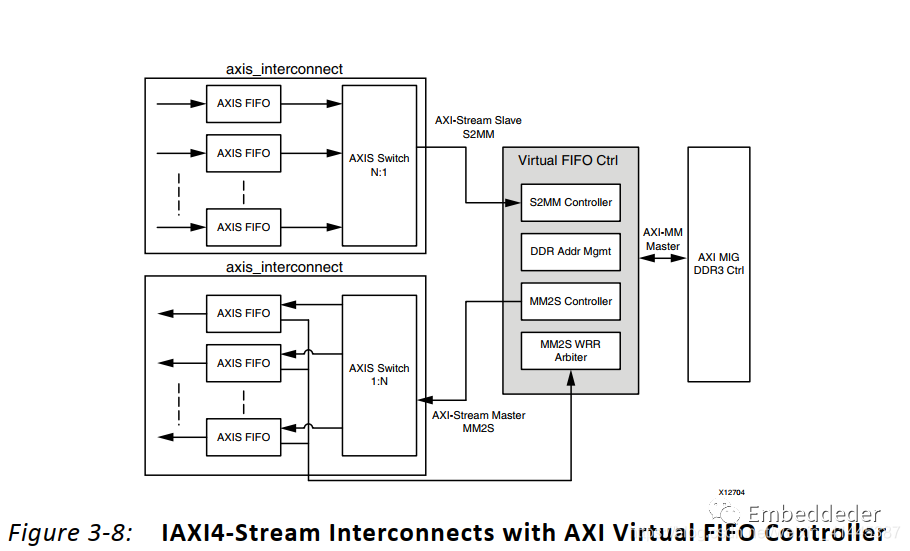

例如,在下面的圖中,AX14-Stream互連與AXI虛擬FIFO控制器一起用于從多個端點主從復用和解復用多個流。

Reference

正點原子講解視頻

UG1037

Vuko csdn博客同步更新~

歡迎大家關注我的博客。如果需要工程微信后臺留言即可~

學習內容

近期設計需要用到AXI總線的IP,所以就對應常用的IP進行簡要的說明,本文主要對AXI互聯IP進行介紹。

基礎架構IP

基礎的IP是用于幫助組裝系統的構建塊。基礎架構IP往往是一個通用IP,它使用通用的AXI4接口在系統中移動或轉換數據,而不解釋數據。

這些基礎的IP各自有自己的常用的功能,下面列舉出一部分AXI接口的基礎構架IP。

° AXI Register slices (for pipelining)用于流水線操作。° AXI FIFOs (for buffering/clock conversion)用于緩存和時鐘轉換。° AXI Interconnect IP and AXI SmartConnect IP (for connecting memory-mapped IP together)用于連接存儲器映射的IP互連。° AXI Direct Memory Access (DMA) engines (for memory-mapped to stream conversion)用于存儲器映射和數據流接口的轉換。° AXI Performance Monitors and Protocol Checkers (for analysis and debug)用于分析仿真。° AXI Verification IP (for simulation-based verification and performance analysis) 用于仿真驗證。

Xilinx AXI SmartConnect IP and AXI Interconnect IP(AXI互聯IP)介紹

Xilinx AXI Interconnect IP和AXI SmartConnect IP都可以將一個或多個AXI存儲器映射的主設備連接到一個或多個存儲器映射的從設備。而使用AXI SmartConnect IP,更緊密地集成到Vivado設計環境中,用戶以最小的用戶干預自動配置和適應已連接的AXI主從IP。AXI互聯IP(AXI SmartConnect IP and AXI Interconnect IP)可以用于所有的存儲器映射設計中。

在某些情況下,對于高帶寬應用程序,使用SmartConnect IP可以提供更好的優化。AXI SmartConnect IP通過綜合針對重要接口進行優化的低區域自定義互連,在低延遲下提供最大的系統吞吐量。

AXI Interconnect IP(axi_interconnect)可以將一個或多個AXI存儲器映射的主設備連接到一個或多個存儲器映射的從設備。Interconnect 相對于SmartConnect IP更符合來自ARM的AMBA AXI4規范,包括AXI4-Lite 接口。

AXI Interconnect IP和AXI SmartConnect IP僅用于存儲器映射傳輸。AXI4-Stream傳輸不適用。但可以使用AXI4-Stream Interconnect IP (axis_interconnect)。帶有AXI4-Stream接口的IP通常彼此連接到DMA IP或者AXI4-Stream Interconnect IP上。

綜上:對于中到高性能設計,推薦使用AXI SmartConnect IP,因為它在面積和時間上提供了更好的向上擴展。對于低性能(AX14-Lite)或中小型復雜性設計,AXI Interconnect IP可能更有效的面積。

AXI Interconnect IP使用方式

對于互聯IP的使用,在xilinx的指導手冊中提到了下述四種方式。

1. Conversion Only(僅轉換操作)

當一個主設備連接到一個從設備時,AXI Interconnect IP可以執行各種轉換和流水線功能。這些操作如下述:

數據寬度轉換

時鐘速率轉換

AXI4-Lite從機自適配

AXI4-3從機自適配

流水線,如寄存器或數據通道FIFO操作。

在這些情況下,AXI Interconnect IP不包含仲裁、解碼或路由等邏輯。可能會導致延遲,延遲大小取決于正在執行的轉換類型。

下圖顯示了一個轉換的示例:

2. N-to-1 Interconnect

AXI Interconnect IP的一個常見退化配置(或者我翻譯為簡化配置)是多個主設備為訪問一個從設備(通常是一個內存控制器)進行仲裁。在這些情況下,地址解碼邏輯可能是不必要的,并且在AXI Interconnect IP被省略(除非需要地址范圍驗證)。在這種配置下,還可以執行數據寬度和時鐘速率轉換等轉換功能。N-to-1 AXI互聯示例如下圖所示:

3. 1-to-N Interconnect

AXI Interconnect IP的另一種退化配置(簡化配置)是當一個主設備(通常是一個處理器)訪問多個內存映射的從外圍設備時。在這些情況下,仲裁(在地址和寫數據路徑)不執行。1 - N互聯示例如下圖所示:

4. N-to-M Interconnect (Sparse Crossbar Mode)

AXI Interconnect的N-to-M用例采用共享地址多數據(SAMD)拓撲,稀疏數據交叉連接,單線程寫和讀地址仲裁,如下圖所示:

下圖展示了稀疏交叉寫和讀數據路徑:

根據配置的稀疏連接映射,并行寫和讀數據通道將每個SI插槽(連接到左邊的AXI主機上)連接到它可以訪問的所有MI插槽(連接到右邊的AXI從機上)。當多個源有數據要發送到不同的目的地時,只要滿足AXI排序規則,數據傳輸就可以獨立并發地進行。在所有SI槽(如果> 1)中的寫地址通道饋送到一個中心地址仲裁器,它一次授予對一個SI槽的訪問權,對于讀地址通道也是如此。

AXI4-Stream Interconnect Core IP介紹

AXI4-Stream Interconnect Core IP(axis_interconnect)將一個或多個AXI4-Stream主設備連接到一個或多個AXI4-Stream從設備。AXI4-Stream Interconnect Core IP 僅用于AXI4-Stream 傳輸;AXI4存儲器映射傳輸不適用。

AXI4-Stream Interconnect Core 內部框圖

AXI4-Stream Interconnect Core IP由SI、MI和包括它們之間的AXI通道的功能單元組成。

SI接受來自連接的主設備的事務請求。

MI向從設備發送事務。

在中心是交換機,它仲裁和路由連接到SI和MI的各種設備之間的通信。

AXI4-Stream Interconnect Core IP還包括位于交換機和每個SI和MI接口之間的其他功能單元,可選擇性地執行各種轉換和存儲功能。該開關有效地將AXI4-Stream Interconnect Core IP從SI相關功能單元(SI半球)和MI相關單元(MI半球)中間分開。這個架構類似于AXI Interconnect IP的架構。

AXI4-Stream Interconnect IP使用方式

AXI4-Stream Interconnect IP將一個或多個AXI4-Stream主設備連接到一個或多個AXI4-Stream從設備。對于AXI4-Stream Interconnect IP,主要有兩種使用方式:

流數據路由和交換

流多路復用和去多路復用

Streaming Data Routing and Switching (Crossbar Mode)流數據路由和交換

ax14流互連可以實現N × M全交叉開關,如下圖所示。它支持從端仲裁,能夠在N個主服務器和M個從服務器之間并行數據傳輸。解碼器和仲裁者服務于主從之間的路由數據傳輸交互。

Stream Multiplexing and De-multiplexing(流多路復用和去多路復用)

你可以在Nx1配置中將AXI4-Stream Interconnect IP配置為一起多路傳輸流,然后配置為1xM來解多路傳輸流。使用多路復用和多路復用解復用來創建多通道流,其中較小數量的導線可以攜帶來自多個主從的共享流量。

例如,在下面的圖中,AX14-Stream互連與AXI虛擬FIFO控制器一起用于從多個端點主從復用和解復用多個流。

編輯:jq

-

控制器

+關注

關注

112文章

16448瀏覽量

179462 -

數據

+關注

關注

8文章

7145瀏覽量

89582 -

IP

+關注

關注

5文章

1718瀏覽量

149968 -

fifo

+關注

關注

3文章

389瀏覽量

43860

原文標題:ZYNQ-AXI互聯IP介紹

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ZYNQ基礎---AXI DMA使用

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

AMBA AXI4接口協議概述

東京裸機云多IP服務器全面分析

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

SoC設計中總線協議AXI4與AXI3的主要區別詳解

全面介紹ZYNQ-AXI互聯IP

全面介紹ZYNQ-AXI互聯IP

評論