Jaya 本期帶來的開發板是ALINX 基于Xilinx Zynq ultraScale+ MPSoC的異構FPGA開發板ALINX AXU2CGA/AXU2CGB。這兩塊開發板的區別是:AXU2CGA是2片DDR4 32bit的,不帶EMMC;而AXU2CGB是4片DDR4 64bit的,帶EMMC,因此本文主要評測的是AXU2CGB 開發板。

盡管板卡使用的使XCZU2CG 使Xilinx Zynq ultraScale+ 系列的丐版,但是拿來上手Xilinx Zynq ultraScale+ 系列FPGA再適合不過。

我們先來開箱,看下AXU2CGB開發板,簡單的了解開發板的整體套件組成。先來看外包裝。

外包裝相對樸實了一點,不像AXU3CG的主板外包裝,標準硬紙殼,少了黑色底金色logo的氣質。不過整體來說,還在中規中矩的范圍范圍,內部加了海綿進行緩沖,外包裝的紙盒也是比較硬朗的那種,對板子的保護性能來說不必黑底金字的包裝差,只是看起來沒有那么高大上。畢竟價格還不到對方的三分之一,想要同等待遇,確實有點過分。

OK就說到這,我們看下套件的組成,雖然外包裝有點縮水,不過我們買板子最重要的當然不是看外包裝玩對吧,我們最關注的肯定是板子和配套的的器件對吧!把包裝盒打開來看看!器件的已經拿出來了,首先我們最關注的核心板被包裝盒的海綿保護的好好的,絲毫不用擔心,線看看其他的配件,這些配件還是老樣子,除了開發板,ALINX的配套器件基本一樣,一套Jtag的調試器,一根USB MINI 轉Tyep A口的數據線,一個12V 3A的電源,一個川宇藍白相間的讀卡器,保修卡,以及和調試器配套的線材,與AXU3CG開發板相比,唯獨的區別就是AXU3CG 適用的是一個風扇作為開發板的散熱,而AXU2CGB開發板是用的一個很大塊的散熱片。對于ZYNQ UltraScale+ 系列的板卡來說,功耗可以達,也可以相對較小,主要差異就是邏輯資源使用的多少,邏輯資源使用的越多,那么需要的瞬間功耗也就會越大,如果電源無法支撐,就會無法運行,一般情況下損壞的概率還是不大的。所以電源的動態響應要高一些。

這里呢,簡單的說配件,其實從個人使用習慣來說,比較希望板卡的最多插三根線,一個根電源線,一根網線,一根串口線,當然串口可以和電源合并當然最好。ALINX大大給提供的配件中包含JTAG,我也在思考ALINX 大大為什么不把JTAG坐在板卡上呢?,做在板子上,如果使用FT2232的方案,就可以將串口和JTAG同時從要給USB MINI 口引入,對于我們這種懶癌重度患者起步美哉?后面小編仔細的想了下,分離的JTAG有分離的好處,首先就是成本的問題,這個成本是針對用戶來說的,如果我們手中有了一個ALINX JTAG的調試器,這樣就可以使用這個調試器調試n多塊擁有JTAG的板子,這些板子也不需要板載調試器,學習的成本就會節省。其次呢,我們使用的Zynq系列的開發板,這系列的芯片最主要的特性就是包含了FPGA和ARM SoC兩個部分,FPGA的調試是使用JTAG比較方便,不過到了ARM的部分,JTAG就沒有那么重要了,多數的PS 端開發,完全不需要使用JTAG,so ALINX 大大這樣做是有充分思考的,JTAG CABLE 使用的都是標準JTAG接口,一個是2.54mm 的兩一個是2.0mm 的,可以相容大多數FPGA的板卡,即使少部分不相容可以使用2.54的排針進行端口轉接。

然后就是串口線的部分,現在來說Type C大行其道,逐步成為外設接口的主流,在USB3.2的協議中明確規定將不再支持USB YTPE A ,TYPE B,以及所衍生的MINI USB 和MICRO USB 接口,ALINX 大大可能進展還沒那么沒有跟上,不過我相信,也許新的版本上就會更新的Tyep C版本的開發,一根線橫掃供電和通信。其他的部分JAYA沒什么感覺畢竟都是ALINX 大大驗證過的標準備件。

下面就是我們開發板的主題,這次的AXU2CGB 開發板,可以算是面向學習者的入門級開發板,作為入門級的開發板,ALINX AXU2CGB 開發板可以算是把入門FPGA的基礎資源準備的一應俱全,當然對于入門級開發板來說,是以學習為主,相關的擴展性會稍微差一點,成本也會更低些,重要體現在,ALINX AXU2CGB 開發板,并沒有使用核心板加擴展板的方案,也就是說這款開發板的核心器件是不可以更換的,在項目中,如果評估的不完善,或者需要加入新的模塊,原本的開發板可能會出現資源不夠的情況,這時候就可以通過更換核心板而將系統的資源再次擴展,當然對于學習來說這個部分的意義不大。

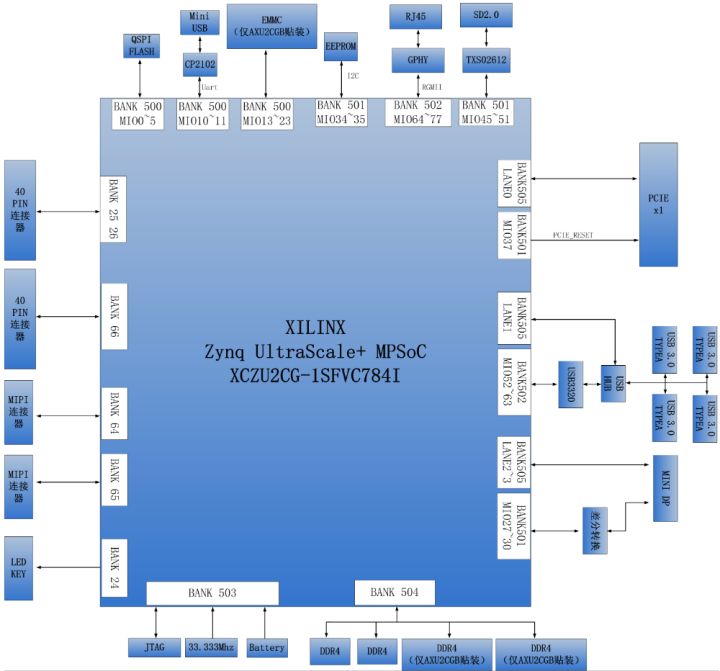

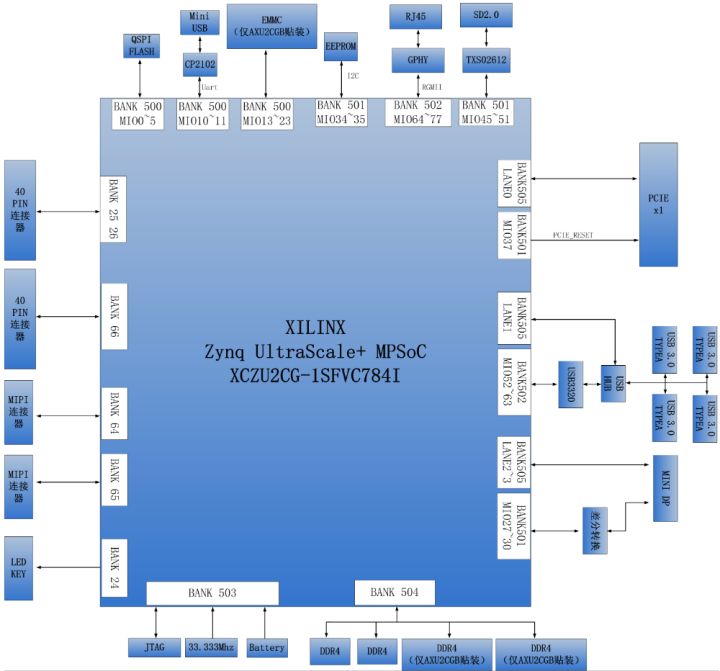

下面我就來看下我們的這塊入門級開發板的硬件按配置,接口如下圖,整體來說接口很完善,常見的接口,十分適合初學者與有一定FPGA基礎的童鞋學習玩耍。

我先從硬件來開始分析分析這款款開發板,看看入門級別的開發板的用料到底怎么樣,我們從最基礎的結構開始逐步向外發散到接口,分析下板卡的用料。

最基礎的結構都包括什么呢?這個問題非常簡單,在整個系統中,沒了哪些部分整個系統將會無法運行呢?那么這些就整個系統的最基礎的部分,比如電源,時鐘,存儲,處理器這幾樣,如果少了些系統時不會跑得起來的。下面我們來看下具體的位置。

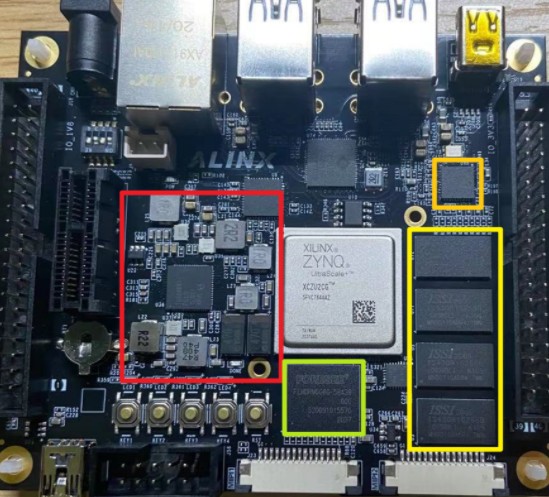

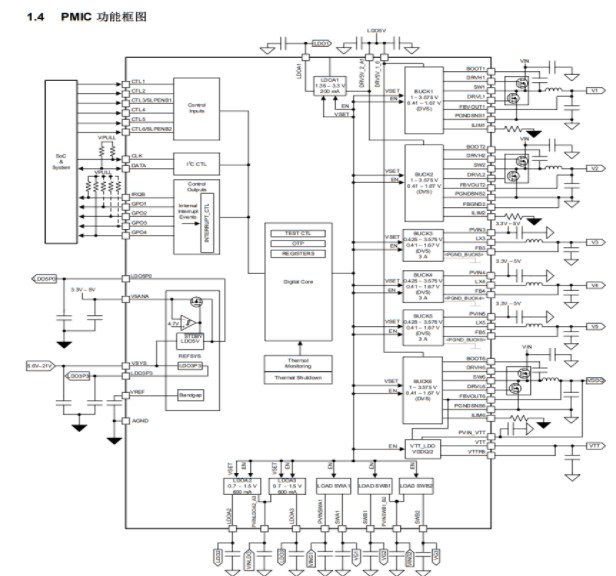

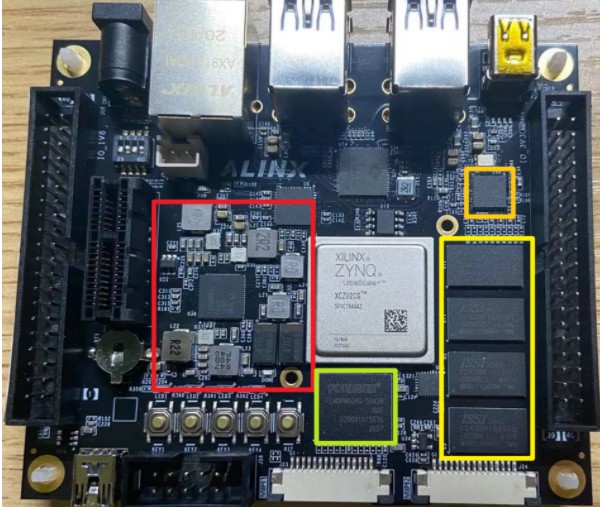

如上圖,紅框內遍布著大量電感的部分就是本次入門級開發板的供電部分,也就是開發板的心臟,由心臟來提供電能給整塊板卡,使整塊板卡運動起來,對于FPGA來說,對于電源的要求是比較高的,因為FPGA啟動的瞬間會有超多的邏輯在一瞬間動起來,這里就是考驗一個電源實力的時刻,并且由于Zynq 集成了FPGA 和ARM 硬核的原因,需要的電源數量也是極其的多。這里我們課可以看間ALINX 大大,使用了一塊來自TI 德州儀器半導體的TPS650864 多軌可調的PMU(power management unit)。使用電源管理電源的好處是整體電源結構比較集中,可以提高電源密度,并且在德州儀器半導體的加持下電源的質量是不用擔心的。這顆TPS650864 多軌可調PMU 適用于多核處理器,FPGA,以及整套系統。

可以看見這周圍的電路比較復雜,附一張Spec中的結構圖紙。

圖中的黃色部分是AXU2CGB 入門開發板的DDR 部分:

AXU2CGA板上PS端配有2片Micron(美光)的共1GB的DDR4芯片,型號為MT40A512M16LY-062EIT,組成32位數據總線帶寬和1GB的容量。AXU2CGB板上PS端配有4片Micron(美光)的1GB的DDR4芯片,型號為MT40A512M16LY-062EIT,組成64位數據總線帶寬和2GB的容量。PS端的DDR4 SDRAM的最高運行速度可達1200MHz(數據速率2400Mbps)。

如圖中,綠色部分位是eMMC,AXU2CGB 配有一片來自江波龍半導體,容量為 8GB 的 eMMC FLASH 芯片。eMMC FLASH 連接到 ZYNQ UltraScale+的 PS 部分 BANK500 的 GPIO 口上。

橙色的部分是SILICON LABS的時鐘芯片Si5332B,Si5332B 任意頻率時鐘發生器提供高集成水平,可在 ADAS、信息娛樂和自主駕駛硬件平臺中實現完整時鐘樹整合。可以任意輸出范圍為 10 – 200M頻率,該設備具有 MultiSynth? 分數和整數分頻器,可同時輸出多達 8 種不同的時鐘。

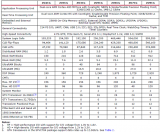

然后最后的主要就器件就是我們的MPSoC,Zynq UltraScale+ CG核心芯片了,這里ALINX提供了我們兩種規格的核心板,分別是AXU2CGA,以及AXU2CGB。兩塊入門級開發板參數對比如下表:

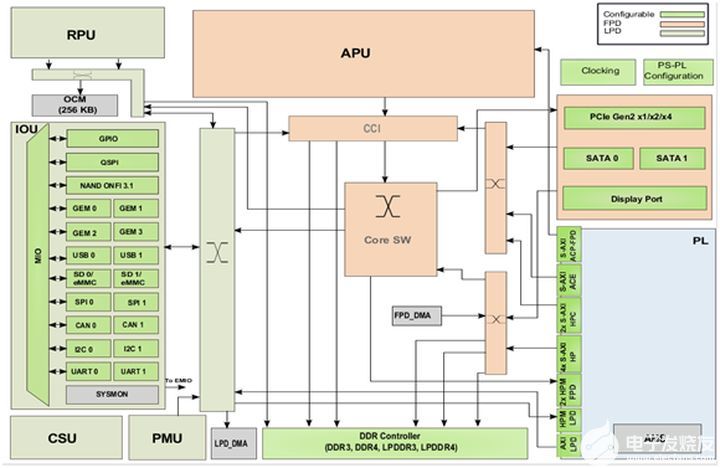

MPSoC均采用XCZU2CG,相關資源如下圖:核心部分是適用雙核的ARM Cortex-A53,1.2GHz,和雙核的Cortex-R5,500MHz。

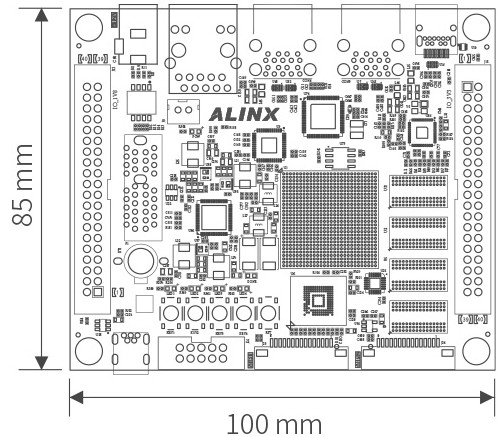

這樣板子的上核心器件我們簡單的介紹完畢,下面就是怎么板卡的接口,如果我們想要和FPGA 或者ARM愉快的玩耍就離不開板卡的外設,想實現一些有趣的功能也少不了與接口的互動,板子上的接口主要包含DP接口,PCIE接口,MIPI接口,USB3.0接口,MINI USB 串口接口,千兆以太網RJ45接口,JTAG接口,EEPROM,SD卡接口,以及我們剛剛開始接觸板卡的第一程序,4個LED燈,以及4個用戶Button,和撥碼開關,以及Reset Button。整體尺寸為85mm * 100mm,相對來說在FPGA 開發板的族群里算是比較苗條的了,同時還可以給我們提供足夠的暢玩空間。

對于JTAG的接口來說,是我們玩耍PL端的所不能或缺的,ALINX適用的是標準的jtag接口,通過連接JTAG接口就可以對PL 以及PS的運行狀態進行監控。

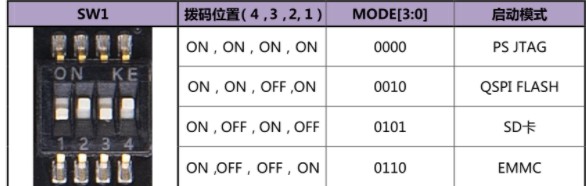

撥碼開關的部分,主要用來配置ALINX AXU2CGB 開發板的啟動模式,具體的配置方法如下表:

LED,BUTTON均位于JTAG接口的上面,BUTTON的按鍵因為有一個較高的JTAG接口在當著,按下時會比較費事,應該是板卡的密度太高,周邊都被豐富的接口堵住,導致按鍵BUTTON沒有了板邊的空間。相應的,每個BUTTON上都有相關的絲印。只是部分被JTAG接口蓋上,但是基本不妨礙我們來閱讀,還是給好評的。

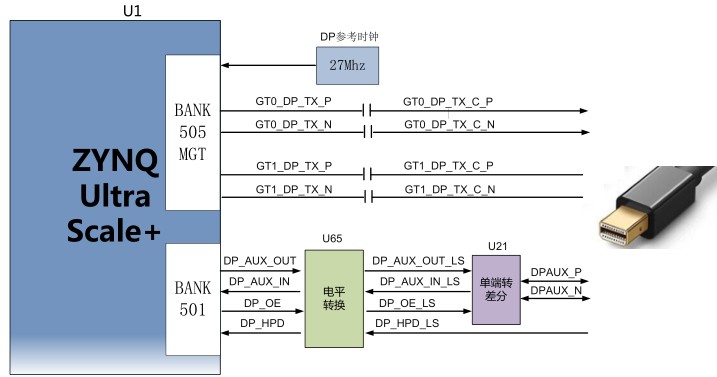

MINI DP 接口為于USB 3.0右邊,AXU2CGA/B 帶有 1 路 MINI 型的 DisplayPort 輸出顯示接口,用于視頻圖像的顯示,最高支持 4K x 2K@30Fps 輸出。ZU2CG PS MGT 的 LANE0 和 LANE1 的 TX 信號以差分信號方式連接到 DP 連接器。DisplayPort 輔助通道連接到 PS 的 MIO 管腳上。

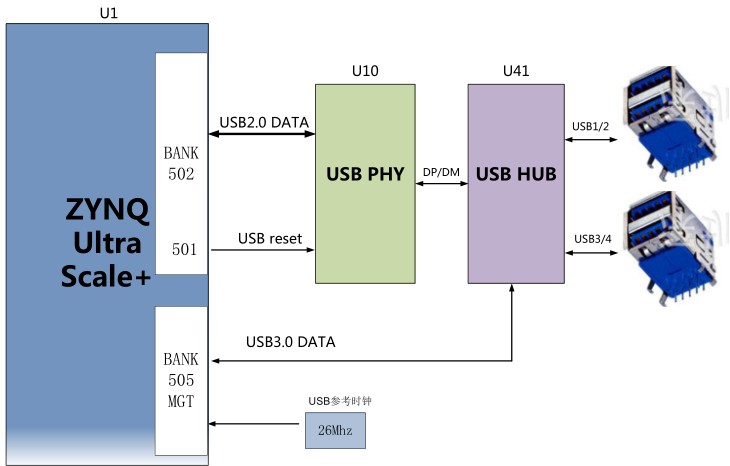

AXU2CGA/B 板上有 4 個 USB3.0 接口,接口為 HOST 工作模式(Type A),數據傳輸速度高達 5.0Gb/s。USB3.0 通過 ULPI 接口連接外部的 USB PHY 芯片和 USB3.0 HUB 芯片,實現高速的 USB3.0 數據通信。

相應的PHY的管腳分配如下圖:

AXU2CGA/B 配備了一個 PCIE x1 的插槽,用于連接 PCIE 外設,PCIE 通信速度高達5Gbps。PCIE 信號直接跟 BANK505 PS MGT 收發器的 LANE0 相連接。這樣我們就可以適用外接的方式擴展PCIE 設備,雖然只有X1,但對于初學者入門,再適合不過了。

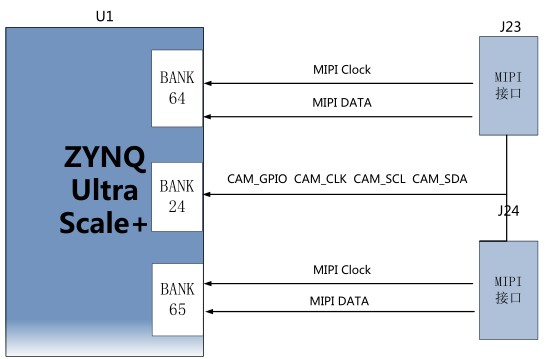

AXU2CGA/B 板上有 2 路 MIPI 接口,用于連接 MIPI 攝像頭。MIPI 的差分信號分別連接到 BANK64、65 的 HP IO 上,電平標準為+1.2V;MIPI 的控制信號連接到 BANK24 上,電平標準為+3.3V。

到這里呢板子上的控制接口和高速接口也就大概的介紹完畢,主要就是DP,USB,PCIE,MIPI。剩下的一些比如SPI NOR Flash,比如I2C的EEPROM,再比如40PIN GPIO接口什么的,基本是都是大家耳熟能詳的了,就再具體說明了,額對大家要注意,板卡的兩邊的40PIN接口并不是完全一樣的,電源口朝前的時候,左手邊的40PIN 接口的IO點評是1.8V,右手邊的40PIN接口IO電平才是3.3V。在接模塊的時候要千萬要注意。

硬件部分的介紹告一段落,在我們進入軟件實操之前,這里還是有一點要大家注意的,在整套的配件包里是有一個散熱片的,Jaya在最開始的時候將他忽略了,也不是故意將散熱片忽略,主要還是想看看2CG系列的芯片溫度怎么樣,于是就是裸著上電了,系統正常跑起來,跑了能有5分支左右,Jaya摸了下AXU2CGB的ZYNQ,由于室內溫度只有十四五度,芯片表面的溫度大概有50度左右,相對來說還好,不過Jaya還是推薦將散熱片加上,芯片表面50度,內部核心可能已經接近八九十度了,一般來說芯片的結溫是125度(商用,高于結溫會有損壞的風險),并且適用時間還不是很長,溫度應該還沒有趨于熱平衡,再加上FPGA的邏輯資源還沒有全部運轉,如果全部加在一起這個溫度可能會瞬間翻倍,雖然不至于燒壞芯片,如果長期適用還是對板卡有損耗。

先來嘗試下PL部分的適用,其實和操作FPGA是一樣的。簡單適用PL端點一個燈,首先我們要安裝FPGA的開發幻劍Vivado,或者Vitis。vitis HLS 能提高系統設計的抽象層次,為設計人員帶來切實的幫助。vitis HLS 通過下面兩種方法提高抽象層次:第一,使用 C/C++作為編程語言,充分利用該語言中提供的高級結構。第二,提供更多數據原語,便于設計人員使用基礎硬件構建塊(位向量、隊列等)。與使用 RTL相比,這兩大特性有助于設計人員使用 vitis HLS 更輕松地解決常見的協議系統設計難題。最終簡化系統匯編,簡化 FIFO 和存儲器訪問,實現控制流程的抽象。

這個部分就具體描述了,官網下載,然后安裝軟件。基本沒有什么難度。下圖就是vitis的啟動界面,vitis 集成vivado,可以滿足我們PL的適用。

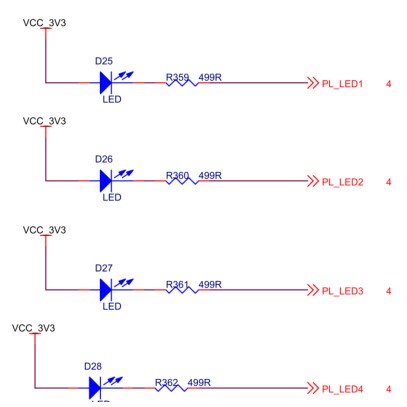

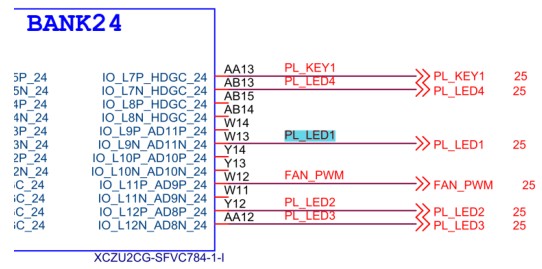

我們既然想要點燈,第一點就必須要了解LED燈的硬件電路是怎么設計的。

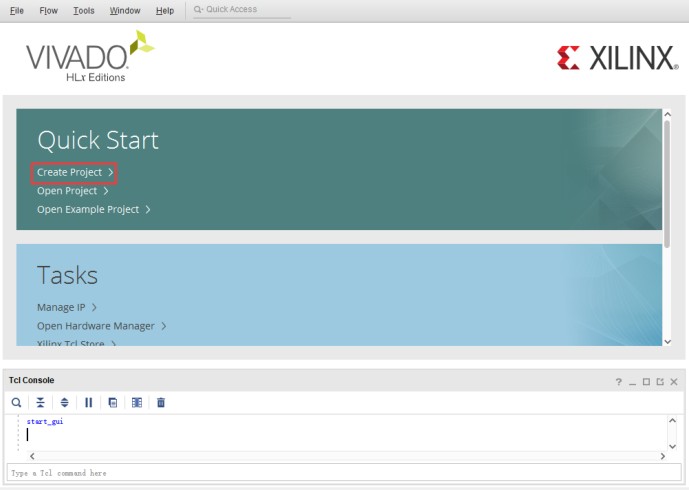

然后打開vivado 創建工程:

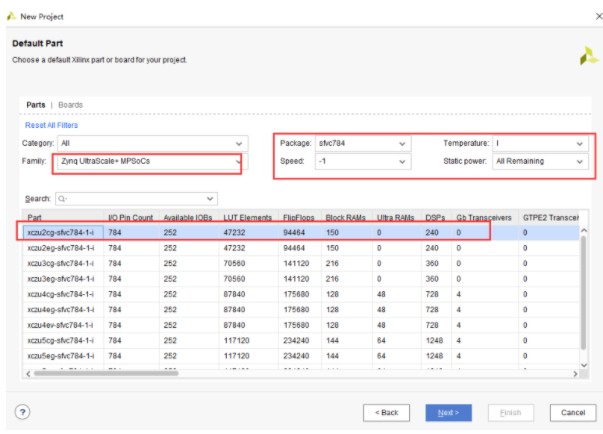

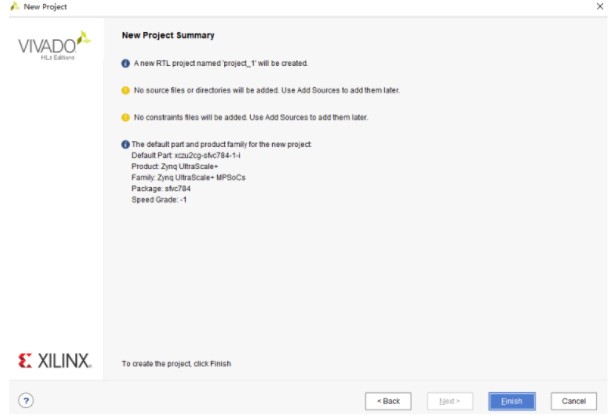

在不斷的下一步過程中,需要選擇芯片的型號時,在“Part”選項中,器件家族“Family”選擇“Zynq UltraScale+ MPSoCs”,封裝類型“Package”選擇“sfvc784”,Speed 選擇”-1”,Temperature 選擇“I”減少選擇范圍。在下拉列表中選擇“xczu2cg-sfvc784-1-i”,“-1”表示速率等級,數字越大,性能越好,速率高的芯片向下兼容速率低的芯片。點擊Next

這時候我們就可以選擇Finish,來完成工程的創建。

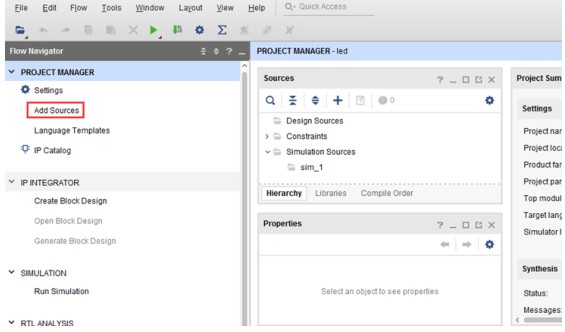

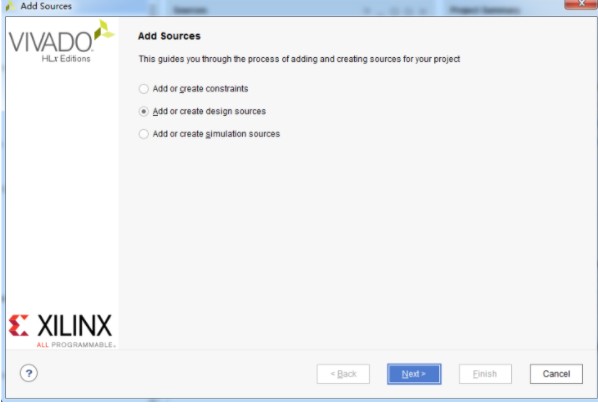

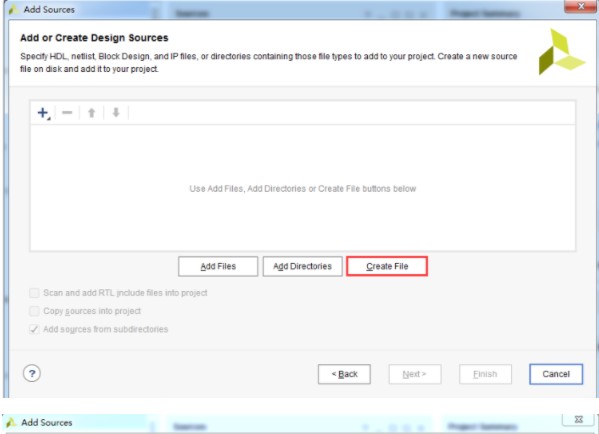

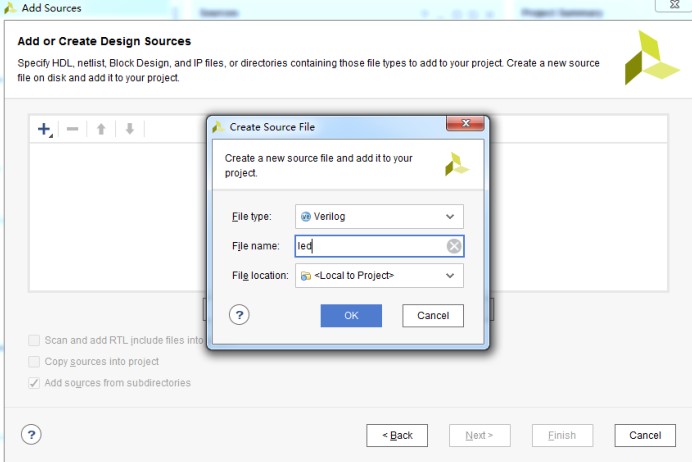

然后我們在工程創建以個LED的verilog文件,選擇add sources。 -》 選擇添加或創建設計源文件“Add or create design sources”,點擊“Next” -》 選擇創建文件“Create File” -》 文件名“File name”設置為“led”,點擊“OK”

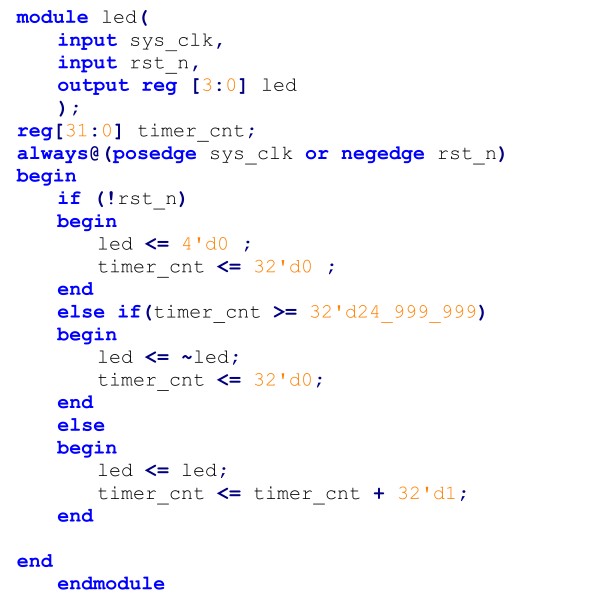

這樣我們就創建好一個LED.v 的文件。在文件中輸入Code,定義一個寄存器,用于循環計數,寄存器 timer 變為 0,并翻轉四個 LED。這樣就是實現了一個點燈的流程。

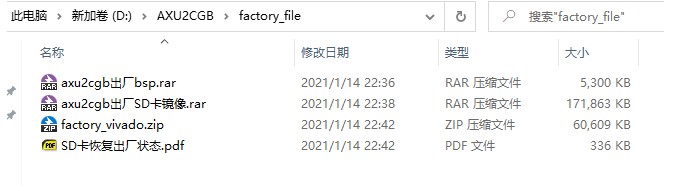

PL部分的簡單例子就到這這里。下面我簡單使用下PS端的資源。我們將板卡的撥碼開關撥到SD卡啟動,然后再SD卡中安裝ALINX AXU2CGB 開發板的測試image。相關的文件存儲在,資料文件中的factory_file中。

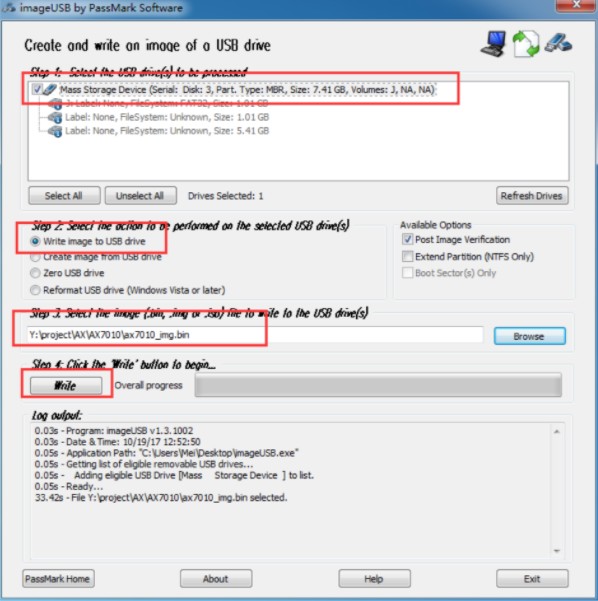

在文件中會有相關的說明,告知我們應該怎樣回復SD卡的內容。使用ALINX大大提供的工具,將相應的文件選上既可以完成SD Zynq啟動卡的制作。

熟悉Zynq 環境的小伙伴也可以通過Petalinux來制作屬于自己定制的Petalinux 系統。相應的燒卡方法也時很簡單的,使用fdisk給SD卡分區,0分區為fat32,1分區為ext4,將rootfs使用dd命令燒錄到分區1,再把打包好的BOOT.bin 和 iamge.ub cp 到0分區大功告成。當然后如果沒有Linux 的環境就比較麻煩了。還需要將環境搭建起來才可以進行SD卡的制作。

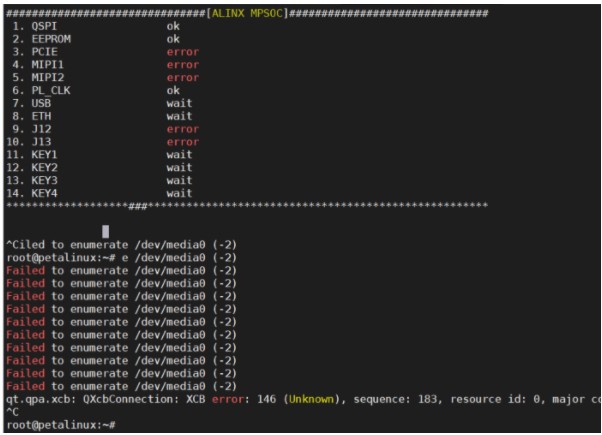

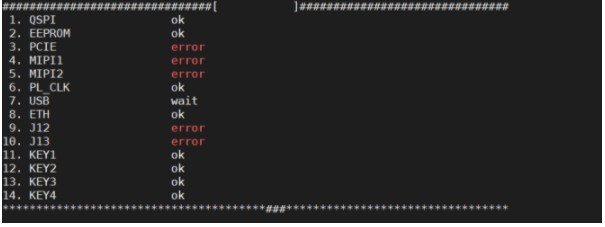

SD卡也有了我們上板使用。如果使用ALINX大大提供的image的話,開機就會進入檢測階段。整個時間大概會持續幾分鐘,插入網線后ETH會狀態會從wait變為OK,按按鍵1-4也是會有同樣的效果。

++++++++++++++++++++++++++++

如果對應輸入后:

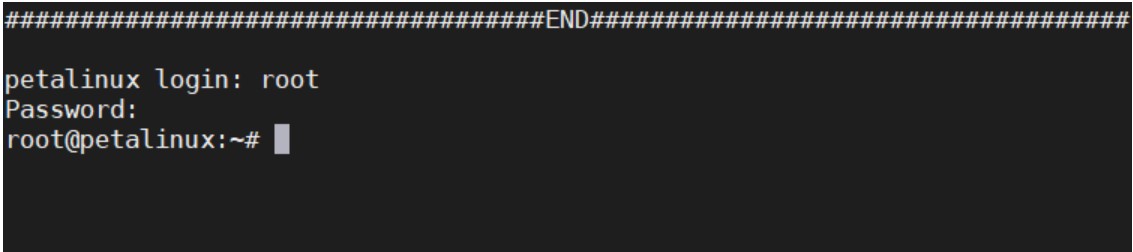

我們輸入用戶名和密碼進入系統,一般來說petalinux 如果沒有特意修改的話,用戶名和密碼都是root。

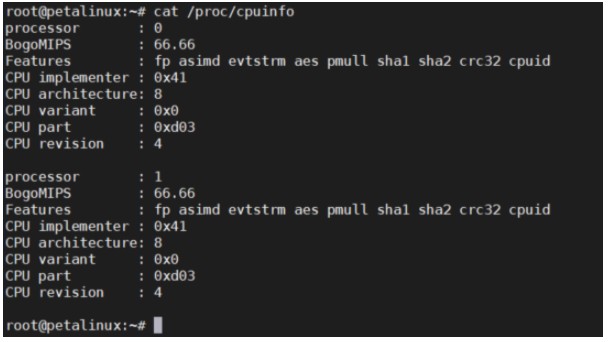

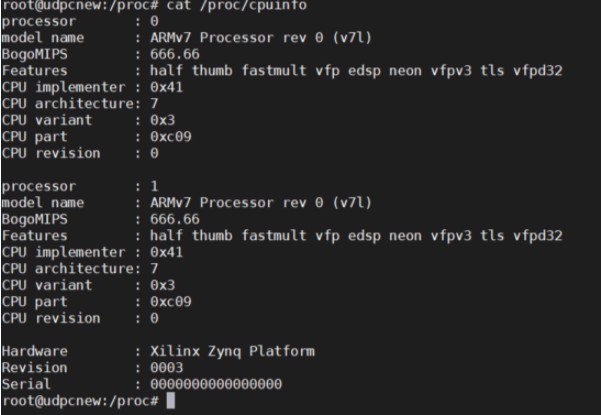

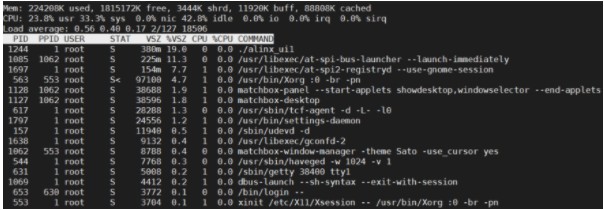

Ok這樣我們就進入到系統里了。我們來讀下CPU看看是不是有兩顆CPU。看了下cpuinfo,確實是兩顆CPU但是并沒有識別到CUP的型號。

但是有點奇怪的是這里并沒有把Model name讀出來,下圖是我順手讀了了下ZYNQ 7010的板子,可意見Model name一欄會有ARMv7的標值。

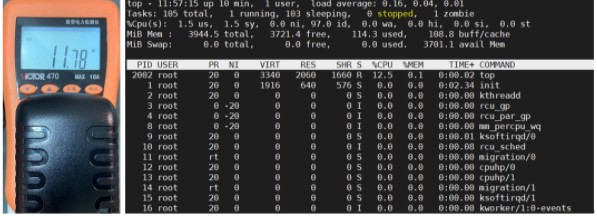

空載的情況下,ALINX AXU2CGB 開發板的功耗基本維持7W左右,由于系統是12V供電中間還有電源的轉換效率,按照80%來算板卡的空載功耗可能接近6W。對于這個級別的FPGA來說也中規中矩。

再來一張之前的ALINX AXU3EG 開發板功耗對別

可看的出來EG的芯片比CG多出一個GPU以及一些邏輯單元功耗上要多出來50%,總的來說對于初學者來說尤其是想要了解FPGA和ARM兩頭抓的小伙伴,ALINX AXU2CGB 開發板再合適不過了,老的ZYNQ 7000系列相對來說是最初賽靈思相對試水的產品,并且整體更偏向于FPGA的部分,使用ARMv7來給FPGA打輔助,EG系列開始,ARM A53才開始爆發出ARM的性能,使得FPGA和ARM完美的配在一起,相輔相成,新的開發環境vitis又再FPGA和ARM兩端搭建橋梁,使整體的開發更加流暢,新版本的Petalinux,也一改之前問題連篇的情況,趨于更加好用,協助我們完成相應的設計以及學習和開發工作。

責任編輯:pj

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

讀卡器

+關注

關注

2文章

419瀏覽量

39463 -

開發板

+關注

關注

25文章

5121瀏覽量

98190

發布評論請先 登錄

相關推薦

Xilinx宣布推出汽車級Zynq UltraScale+ MPSoC系列

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

詳解Xilinx公司Zynq? UltraScale+?MPSoC產品

ZYNQ Ultrascale+ MPSOC FPGA開發系統的結構示意圖

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二章 硬件原理圖介紹

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

AXU2CGB Zynq UltraScale板上的GNU Radio工具包 第4部分

AXU2CGB Zynq UltraScale板上的GNU Radio工具包 第3部分

AXU2CGB Zynq UltraScale板上的GNU Radio工具包 第1部分

適用于Xilinx Zynq UltraScale+ MPSoC應用的電源參考設計

AMD推出全新Spartan UltraScale+ FPGA系列

基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 開發板評測

基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 開發板評測

評論