現(xiàn)代的CPU基本上歸為馮諾伊曼結(jié)構(gòu)(也成普林斯頓結(jié)構(gòu))和哈佛結(jié)構(gòu)。

馮洛伊曼結(jié)構(gòu)就是我們所說(shuō)的X86架構(gòu),而哈佛結(jié)構(gòu)就是ARM架構(gòu)。一個(gè)廣泛用于桌面端(臺(tái)式/筆記本/服務(wù)器/工作站等),一個(gè)雄踞移動(dòng)領(lǐng)域,我們的手持設(shè)備(平板手機(jī)用的大多就是他了)。

01馮·諾依曼體系

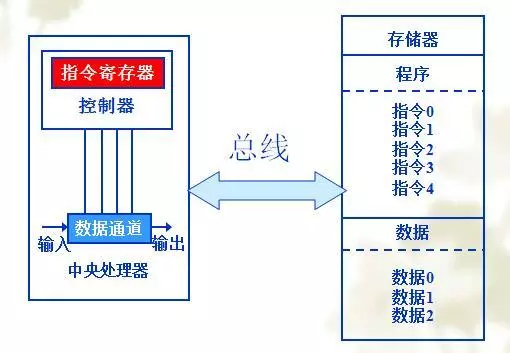

馮·諾依曼體系結(jié)構(gòu)圖如下

馮·諾依曼體系的特點(diǎn):

A、數(shù)據(jù)與指令都存儲(chǔ)在同一存儲(chǔ)區(qū)中,取指令與取數(shù)據(jù)利用同一數(shù)據(jù)總線(xiàn)。

B、被早期大多數(shù)計(jì)算機(jī)所采用。

C、ARM7——馮諾依曼體系結(jié)構(gòu)簡(jiǎn)單,但速度較慢。取指不能同時(shí)取數(shù)據(jù)

馮·諾依曼結(jié)構(gòu)也稱(chēng)普林斯頓結(jié)構(gòu),是一種將程序指令存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器合并在一起的存儲(chǔ)器結(jié)構(gòu)。程序指令存儲(chǔ)地址和數(shù)據(jù)存儲(chǔ)地址指向同一個(gè)存儲(chǔ)器的不同物理位置,因此程序指令和數(shù)據(jù)的寬度相同,如英特爾公司的8086中央處理器的程序指令和數(shù)據(jù)都是16位寬。

馮。諾依曼結(jié)構(gòu)處理器具有以下幾個(gè)特點(diǎn):

1:必須有一個(gè)存儲(chǔ)器;

2:必須有一個(gè)控制器;3:必須有一個(gè)運(yùn)算器,用于完成算術(shù)運(yùn)算和邏輯運(yùn)算;4:必須有輸入設(shè)備和輸出設(shè)備,用于進(jìn)行人機(jī)通信。另外,程序和數(shù)據(jù)統(tǒng)一存儲(chǔ)并在程序控制下自動(dòng)工作。馮·諾依曼結(jié)構(gòu):英特爾公司的8086。英特爾公司的其他中央處理器。ARM的ARM7。MIPS公司的MIPS處理器。

02哈佛體系

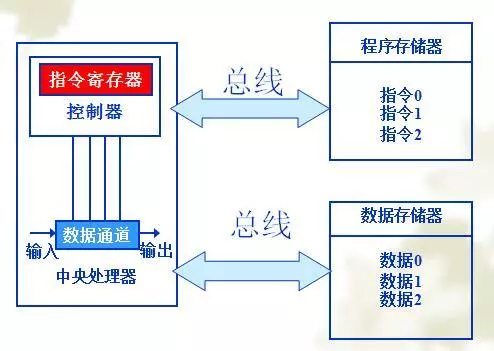

哈佛體系結(jié)構(gòu)圖

結(jié)構(gòu)特點(diǎn):

A、程序存儲(chǔ)器與數(shù)據(jù)存儲(chǔ)器分開(kāi)。

B、提供了較大的存儲(chǔ)器帶寬,各自有自己的總線(xiàn)。

C、適合于數(shù)字信號(hào)處理。

D、大多數(shù)DSP都是哈佛結(jié)構(gòu)。

E、ARM9是哈佛結(jié)構(gòu),取指和取數(shù)在同一周期進(jìn)行,提高速度,改進(jìn)哈佛體系結(jié)構(gòu)分成三個(gè)存儲(chǔ)區(qū):程序、數(shù)據(jù)、程序和數(shù)據(jù)共用。

哈佛結(jié)構(gòu)是一種存儲(chǔ)器并行體系結(jié)構(gòu),主要特點(diǎn)是將程序和數(shù)據(jù)存儲(chǔ)在不同的存儲(chǔ)空間中,即程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器是兩個(gè)獨(dú)立的存儲(chǔ)器,每個(gè)存儲(chǔ)器獨(dú)立編址、獨(dú)立訪(fǎng)問(wèn)。程序指令存儲(chǔ)和數(shù)據(jù)存儲(chǔ)分開(kāi),可以使指令和數(shù)據(jù)有不同的數(shù)據(jù)寬度。

哈佛結(jié)構(gòu)能基本上解決取指和取數(shù)的沖突問(wèn)題。而對(duì)另一個(gè)操作數(shù)的訪(fǎng)問(wèn),就只能采用Enhanced哈佛結(jié)構(gòu)了,例如像TI那樣,數(shù)據(jù)區(qū)再split,并多一組總線(xiàn)。或向AD那樣,采用指令cache,指令區(qū)可存放一部分?jǐn)?shù)據(jù)。。

哈佛結(jié)構(gòu):

1、ARM(除arm7)

2、大部分DSP

哈佛體系架構(gòu)有個(gè)致命的弱點(diǎn)在動(dòng)態(tài)加載程序上面,想象我們從外存中讀取一段程序然后加載到RAM,這個(gè)程序是在數(shù)據(jù)內(nèi)存當(dāng)中的,我們需要一種機(jī)制將數(shù)據(jù)內(nèi)存再傳輸?shù)匠绦騼?nèi)存當(dāng)中去,這反而增加了設(shè)備復(fù)雜度。

對(duì)于多任務(wù)操作系統(tǒng)來(lái)說(shuō),管理程序內(nèi)存是一件非常重要的事情,而且僅僅是保護(hù)模式下的頁(yè)面映射等等機(jī)制就已經(jīng)足夠復(fù)雜了,如果還要求將程序和數(shù)據(jù)分開(kāi)管理,復(fù)雜度就太高了。這種時(shí)候馮諾依曼體系結(jié)構(gòu)就有非常大的優(yōu)勢(shì)了。

03arm和哈佛、馮·諾依曼的關(guān)系

哈佛架構(gòu)是針對(duì)cpu從cache中取指而言,指令和數(shù)據(jù)在主存中并未分開(kāi),但在加載到cache中的時(shí)候被分離為指令和數(shù)據(jù)兩份存儲(chǔ)空間,cpu可以同時(shí)從cache取到指令和數(shù)據(jù)。

所以arm系統(tǒng)CPU(除arm7)對(duì)外表現(xiàn)為馮。諾伊曼架構(gòu),對(duì)內(nèi)則表現(xiàn)為哈佛架構(gòu)。

04實(shí)際芯片制造

實(shí)際上,絕大多數(shù)現(xiàn)代計(jì)算機(jī)使用的是所謂的“ModifiedHarvard Architecture”,指令和數(shù)據(jù)共享同一個(gè)address space,但緩存是分開(kāi)的。可以說(shuō)是兩種架構(gòu)的一種折中吧。

在現(xiàn)實(shí)世界中很少有非常純粹的概念,特別是在實(shí)際的應(yīng)用里。教科書(shū)里的大多是理想化的模型,便于掌握某個(gè)概念的重點(diǎn)和本質(zhì),但實(shí)際中很難達(dá)到這種理想化的狀態(tài)。

哈佛結(jié)構(gòu)和馮諾依曼結(jié)構(gòu)主要區(qū)別在是否區(qū)分指令與數(shù)據(jù)。在教科書(shū)里這是兩種截然不同的做法。

但實(shí)際上在內(nèi)存里,指令和數(shù)據(jù)是在一起的。而在CPU內(nèi)的緩存中,還是會(huì)區(qū)分指令緩存和數(shù)據(jù)緩存,最終執(zhí)行的時(shí)候,指令和數(shù)據(jù)是從兩個(gè)不同的地方出來(lái)的。你可以理解為在CPU外部,采用的是馮諾依曼模型,而在CPU內(nèi)部用的是哈佛結(jié)構(gòu)。

大部分的DSP都沒(méi)有緩存,因而直接就是哈佛結(jié)構(gòu)。

哈佛結(jié)構(gòu)設(shè)計(jì)復(fù)雜,但效率高。馮諾依曼結(jié)構(gòu)則比較簡(jiǎn)單,但也比較慢。CPU廠(chǎng)商為了提高處理速度,在CPU內(nèi)增加了高速緩存。也基于同樣的目的,區(qū)分了指令緩存和數(shù)據(jù)緩存。有時(shí)為了解決現(xiàn)實(shí)問(wèn)題,究竟是什么主義真的沒(méi)那么重要。因而個(gè)人認(rèn)為爭(zhēng)論到底是哪種結(jié)構(gòu)意義不大。

編輯:lyn

-

cpu

+關(guān)注

關(guān)注

68文章

10904瀏覽量

213023 -

ARM架構(gòu)

+關(guān)注

關(guān)注

15文章

177瀏覽量

36443 -

X86架構(gòu)

+關(guān)注

關(guān)注

8文章

45瀏覽量

23713

原文標(biāo)題:STM32屬于哈佛結(jié)構(gòu)還是馮諾依曼結(jié)構(gòu)?

文章出處:【微信號(hào):gh_c472c2199c88,微信公眾號(hào):嵌入式微處理器】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

鐵電存儲(chǔ)器的結(jié)構(gòu)特點(diǎn)

CPU時(shí)鐘周期與主頻的關(guān)系和區(qū)別

CPU時(shí)鐘周期、機(jī)器周期和指令周期的關(guān)系

ARM處理器的結(jié)構(gòu)和特點(diǎn)

自動(dòng)駕駛?cè)笾髁餍酒軜?gòu)分析

CPU與哈佛結(jié)構(gòu)和馮諾依曼結(jié)構(gòu)之間的關(guān)系及各自特點(diǎn)

CPU與哈佛結(jié)構(gòu)和馮諾依曼結(jié)構(gòu)之間的關(guān)系及各自特點(diǎn)

評(píng)論