前言

本文針對秋招面試高頻問題: AXI總線進行總結學習;

1.簡介

AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

AXI(Advanced eXtensible Interface)是一種總線協議,該協議是ARM公司提出的AMBA3.0中最重要的部分,是一種面向高性能、高帶寬、低延遲的片內總線。AMBA4.0將其修改升級為AXI4.0。AMBA4 包括AXI4、AXI4-lite、ACE4、AXI4-stream。

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數據突發傳輸;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元。

AXI4-Stream:(For high-speed streaming data.)面向高速流數據傳輸;去掉了地址項,允許無限制的數據突發傳輸規模。

1.1 AXI協議特點

AMBA AXI協議支持支持高性能、高頻率系統設計;

適合高帶寬低延時設計

無需復雜的橋就能實現高頻操作

能滿足大部分器件的接口要求

適合高初始延時的存儲控制器

提供互聯架構的靈活性與獨立性

向下兼容已有的AHB和APB接口關鍵特點

分離的地址/控制、數據相位

使用字節選通,支持非對齊的數據傳輸

基于burst傳輸,只需傳輸首地址

讀、寫數據通道分離,能提供低功耗DMA

支持多種尋址方式

支持亂序傳輸

易于添加寄存器級來進行時序收斂

支持outstanding AXI可以連續發送多個突發傳輸的首地址而無需等待之前的突發傳輸完成,這有助于流水處理transaction

1.2 AXI讀寫架構

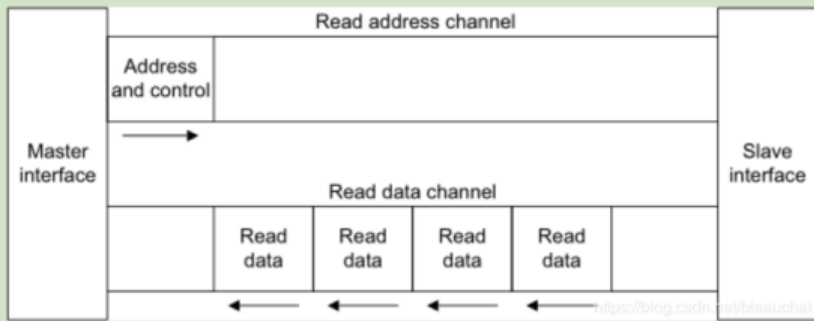

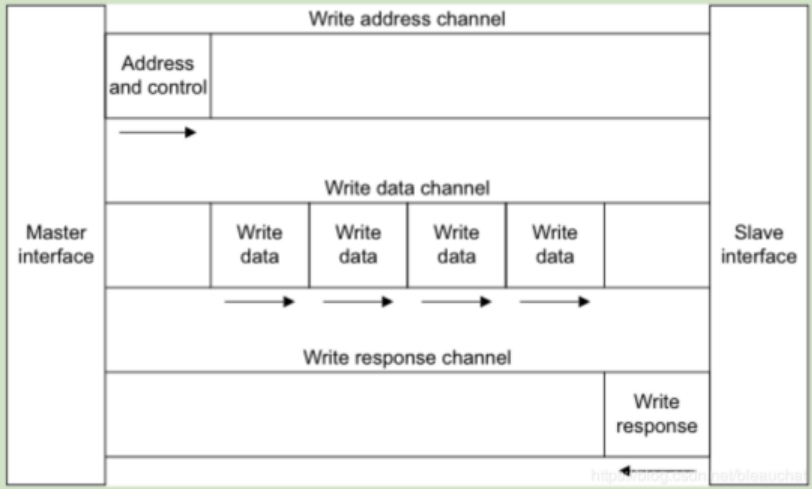

AXI協議是基于burst的傳輸,并且定義了以下5個獨立的傳輸通道:讀地址通道、讀數據通道、寫地址通道、寫數據通道、寫響應通道。 地址通道攜帶控制消息,用于描述被傳輸的數據屬性;數據傳輸使用寫通道來實現master到slave的傳輸,slave使用寫響應通道來完成一次寫傳輸;讀通道用來實現數據從slave到master的傳輸。

讀架構

寫架構

AXI使用基于VALID/READY的握手機制數據傳輸協議;傳輸源端使用VALID表明地址/控制信號、數據是有效的;目的端使用READY表明自己能夠接受信息 ;讀/寫地址通道:讀、寫傳輸每個都有自己的地址通道,對應的地址通道承載著對應傳輸的地址控制信息;

讀數據通道:讀數據通道承載著讀數據和讀響應信號包括數據總線(8/16/32/64/128/256/512/1024 bit)和指示讀傳輸完成的讀響應信號;

寫數據通道:寫數據通道的數據信息被認為是緩沖了的,master無需等待slave對上次寫傳輸的確認即可發起一次新的寫傳輸。寫通道包括數據總線(8/16/32/64/128/256/512/1024 bit)和字節線(用于指示8 bit 數據信號的有效性);

寫響應通道:slave使用寫響應通道對寫傳輸進行響應。所有的寫傳輸需要寫響應通道的完成信號;

通道名稱通道功能數據流向

read address讀地址通道主機-》從機

read data讀數據通道(包括數據通道和讀響應通道)從機-》主機

write address寫地址通道主機-》從機

write data寫數據通道(包括數據通道和每8bit一個byte的寫數據有效信號)主機-》從機

write response寫響應通道從機-》主機

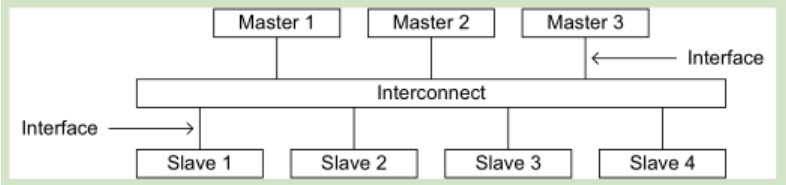

1.3 接口和互聯

AXI協議提供單一的接口定義,用在下述三種接口之間:master/interconnect、slave/interconnect、master/slave。可以使用以下幾種典型的系統拓撲架構:

共享地址與數據總線

共享地址總線,多數據總線

multilayer多層,多地址總線,多數據總線

在大多數系統中,地址通道的帶寬要求沒有數據通道高,因此可以使用共享地址總線,多數據總線結構來對系統性能和互聯復雜度進行平衡;

寄存器片(Register Slices):每個AXI通道使用單一方向傳輸信息,并且各個通道直接沒有任何固定關系。因此可以可以在任何通道任何點插入寄存器片,當然這會導致額外的周期延遲。

使用寄存器片可以實現周期延遲(cycles of latency)和最大操作頻率的折中;

使用寄存器片可以分割低速外設的長路徑;

2.信號描述

信號名來源描述

ACLKsystem clock全局時鐘信號

ARESTnsystem reset全局復位信號,低有效

全局信號

信號名來源描述

AWIDmaster寫地址ID(用于區分該地址屬于哪個寫地址組)

AWADDRmaster寫地址

AWLENmaster突發長度

AWSIZEmaster突發尺寸(每次突發傳輸的最長byte數)

AWBURSTmaster突發方式(FIXED,INCR,WRAP)

AWCACHEmaster存儲類型(標記系統需要的傳輸類型)

AWPROTmaster保護模式

AWQOSmasterQoS標識符

AWREGIONmasterregion標識符(當slave有多種邏輯接口時標識使用的邏輯接口)

AWUSERmaster用戶自定義信號

AWVALIDmaster寫地址有效信號(有效時表示AWADDR上地址有效)

AWREADYmaster寫從機就緒信號(有效時表示從機準備好接收地址)

寫地址通道信號

信號名來源描述

WDATAmaster寫數據

WSTRBmaster數據段有效(標記寫數據中哪幾個8位字段有效)

WLASTmasterlast信號(有效時表示當前為突發傳輸最后一個數據)

WUSERmaster用戶自定義信號

WVALIDmaster寫有效信號(有效時表示WDATA上數據有效)

WREADYslave寫ready信號(有效時表示從機準備好接收數據)

寫數據通道信號

信號名來源描述

BIDslave響應ID

BRESPslave寫響應

BUSERslave用戶自定義信號

BVALIDslave寫響應信號有效

BREADYmaster寫響應ready(主機準備好接受寫響應信號)

寫響應通道信號

信號名來源描述

ARIDmaster讀地址ID

ARADDRmaster讀地址

ARLENmaster突發長度

ARSIZEmaster突發尺寸(每次突發傳輸的byte數)

ARBURSTmaster突發類型(FIXED,INCR,WRAP)

ARCACHEmaster存儲類型

ARPROTmaster保護類型

ARQOSmasterQoS標識符

ARREGIONmaster區域標識符

ARUSERmaster用戶自定義

ARVALIDmaster讀地址有效(有效時表示ARADDR上地址有效)

ARREADYslave寫有效信號(有效時表示從機準備好接收讀地址)

讀地址通道信號

信號名來源描述

RIDslave讀ID標簽

RDATAslave讀數據

RRESPslave讀響應

RLASTslave有效時表示為突發傳輸的最后一個

RUSERslave用戶自定義

RVALIDslave讀數據有效信號

RREADYmaster主機就緒信號(有效時表示)

讀數據通道信號

信號名來源描述

CSYSREQClock controller該信號有效時,系統退出低功耗模式

CSYSACKPeripheral device退出低功耗模式應答信號

CACTIVEPeripheral device外設申請時鐘信號

低功耗接口信號

3.信號接口要求

3.1讀寫傳輸

3.1.1 握手過程

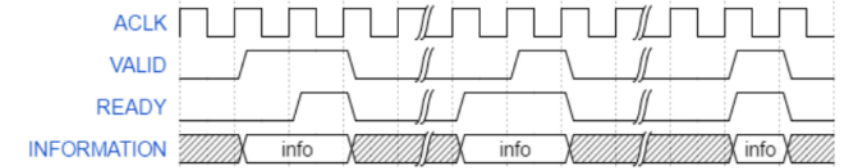

5個傳輸通道均使用VALID/READY信號對傳輸過程的地址、數據、控制信號進行握手。使用雙向握手機制,傳輸僅僅發生在VALID、READY同時有效的時候。VALID信號表示地址/數據/應答信號總線上的信號是有效的,由傳輸發起方控制

READY信號表示傳輸接收方已經準備好接收,由傳輸接收方控制下圖是幾種握手機制:

VALID和READY的先后關系具有三種情況:

VALID先有效,等待READY有效后完成傳輸(VALID一旦有效后在傳輸完成前不可取消)

READY先有效,等待VALID有效后完成傳輸(READY可以在VALID有效前撤銷)

VALID和READY同時有效,立刻完成傳輸此外,需要注意的是允許READY信號等待VALID信號再有效,即使從機準備好,也可以不提供READY信號,等到主機發送VALID信號再提供READY信號。對應的VALID信號不允許等待READY信號,即不允許VALID等待READY信號拉高后再拉高,否則容易產生死鎖現象。

命令通道握手(讀地址,寫地址,寫響應)

僅當地址等信息有效時,才拉高VALID,該VALID必須保持直到傳輸完成(READY置位)

READY默認狀態不關心,僅當準備好接收時拉高READY數據通道握手(寫數據和讀數據)

突發讀寫模式下,僅數據信息有效時才拉高VALID,該VALID必須保持直到傳輸完成。當突發傳輸最后一個數據發送時拉高LAST信號

READY默認狀態不關心,僅當準備好接收時拉高READY通道信號要求:

通道握手信號:每個通道有自己的xVALID/xREADY握手信號對。

寫地址通道:當主機驅動有效的地址和控制信號時,主機可以斷言AWVALID,一旦斷言,需要保持AWVALID的斷言狀態,直到時鐘上升沿采樣到從機的AWREADY。AWREADY默認值可高可低,推薦為高(如果為低,一次傳輸至少需要兩個周期,一個用來斷言AWVALID,一個用來斷言AWREADY);當AWREADY為高時,從機必須能夠接受提供給它的有效地址。

寫數據通道:在寫突發傳輸過程中,主機只能在它提供有效的寫數據時斷言WVALID,一旦斷言,需要保持斷言狀態,知道時鐘上升沿采樣到從機的WREADY。WREADY默認值可以為高,這要求從機總能夠在單個周期內接受寫數據。主機在驅動最后一次寫突發傳輸是需要斷言WLAST信號。

寫響應通道:從機只能它在驅動有效的寫響應時斷言BVALID,一旦斷言需要保持,直到時鐘上升沿采樣到主機的BREADY信號。當主機總能在一個周期內接受寫響應信號時,可以將BREADY的默認值設為高。

讀地址通道:當主機驅動有效的地址和控制信號時,主機可以斷言ARVALID,一旦斷言,需要保持ARVALID的斷言狀態,直到時鐘上升沿采樣到從機的ARREADY。ARREADY默認值可高可低,推薦為高(如果為低,一次傳輸至少需要兩個周期,一個用來斷言ARVALID,一個用來斷言ARREADY);當ARREADY為高時,從機必須能夠接受提供給它的有效地址。

讀數據通道:只有當從機驅動有效的讀數據時從機才可以斷言RVALID,一旦斷言需要保持直到時鐘上升沿采樣到主機的BREADY。BREADY默認值可以為高,此時需要主機任何時候一旦開始讀傳輸就能立馬接受讀數據。當最后一次突發讀傳輸時,從機需要斷言RLAST。

3.1.2 通道順序

傳輸中,通道傳輸的先后有以下規定

寫響應通道傳輸必須在寫操作完成以后進行

讀數據通道傳輸必須在讀地址通道傳輸后進行

必須遵循一系列的狀態依賴關系

通道握手信號的依耐關系

為防止死鎖,通道握手信號需要遵循一定的依耐關系。VALID信號不能依耐READY信號。

AXI接口可以等到檢測到VALID才斷言對應的READY,也可以檢測到VALID之前就斷言READY。下面有幾個圖表明依耐關系,單箭頭指向的信號能在箭頭起點信號之前或之后斷言;雙箭頭指向的信號必須在箭頭起點信號斷言之后斷言。

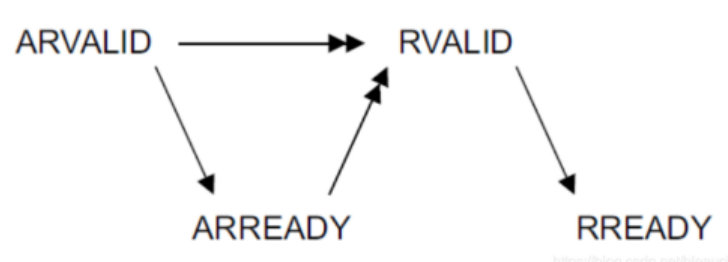

讀傳輸握手依耐關系

上圖為讀操作的依賴關系,ARREADY可以等待ARVALID信號,RVALID必須等待ARVALID和ARREADY同時有效后(一次地址傳輸發生)才能能有效;

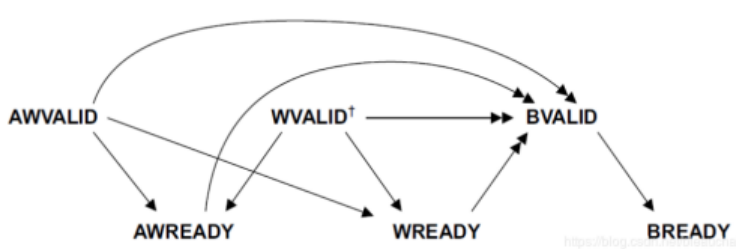

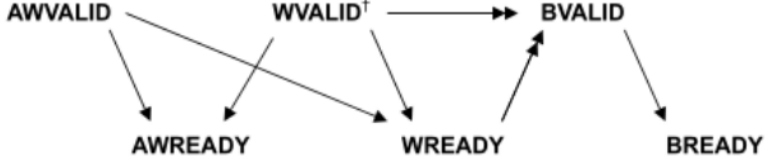

寫傳輸握手依耐關系

從機寫響應握手依耐關系

在AXI3中,寫操作中唯一的強依賴關系是寫響應通道BVALID,僅當WVALID和WREADY信號同時有效(數據傳輸完成)且WLAST信號有效(突發傳輸的最后一個數據傳輸完成)后才會被置位;

在AXI4中,定義了額外的依賴關系,即BVALID必須依賴AWVALID、AWREADY、WVALID和WREADY信號;

3.2時鐘復位

時鐘: 每個AXI組件使用一個時鐘信號ACLK,所有輸入信號在ACLK上升沿采樣,所有輸出信號必須在ACLK上升沿后發生。

復位: AXI使用一個低電平有效的復位信號ARESETn,復位信號可以異步斷言,但必須和時鐘上升沿同步去斷言。

復位期間對接口有如下要求:

主機接口必須驅動ARVALID,AWVALID,WVALID為低電平;

從機接口必須驅動RVALID,BVALID為低電平;

所有其他信號可以被驅動到任意值。在復位后,主機可以在時鐘上升沿驅動ARVALID,AWVALID,WVALID為高電平。

4.傳輸結構

4.1.地址通道數據結構

AXI總線是基于突發傳輸的總線,若主機要開始一次突發傳輸,需要傳輸一次地址和相關控制信號,之后從機自動計算地址(主機只給出突發傳輸的第一個字節的地址,從機必須計算突發傳輸后續的地址),但一次突發傳輸的地址范圍不能跨越4KB(防止突發跨越兩個從機的邊界,也限制了從機所需支持的地址自增數)。

(1)。突發傳輸信息

突發長度(AxLEN)

突發長度為每次突發傳輸的傳輸次數,范圍限制1~16(AXI4增量模式1~256)。每次傳輸的突發長度為AxLEN[3:0] + 1(AXI增量模式AxLEN[7:0] + 1)

AXI3只支持1~16次的突發傳輸(Burst_length=AxLEN[3:0]+1);

AXI4擴展突發長度支持INCR突發類型為1~256次傳輸,對于其他的傳輸類型依然保持1~16次突發傳輸(Burst_Length=AxLEN[7:0]+1)。

對于回卷模式突發傳輸,突發長度僅能是2,4,8或16。

ARLEN[7:0]:讀地址通道的突發長度接口

AWLEN[7:0]:寫地址通道的突發長度接口burst傳輸具有如下規則:

wraping burst ,burst長度必須是2,4,8,16

burst不能跨4KB邊界

不支持提前終止burst傳輸(可以通過關閉所有數據字段的方式使一段傳輸數據無效,但傳輸行為必須完成)

所有的組件都不能提前終止一次突發傳輸。然而,主機可以通過解斷言所有的寫的strobes來使非所有的寫字節來減少寫傳輸的數量。讀burst中,主機可以忽略后續的讀數據來減少讀個數。也就是說,不管怎樣,都必須完成所有的burst傳輸。

提醒:對于FIFO,忽略后續讀數據可能導致數據丟失,必須保證突發傳輸長度和要求的數據傳輸大小匹配。

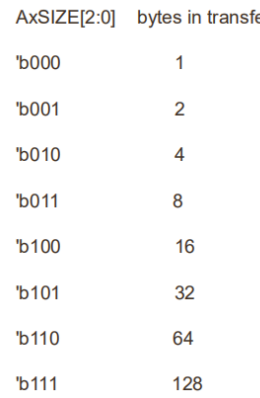

突發尺寸(AxSIZE)

突發尺寸為每次傳輸的byte數量,與突發傳輸的地址預測相關性很強。每次的突發尺寸不能超過數據通道的寬度;若突發尺寸小于數據通道寬度,需要指定哪些位數是有效的。突發尺寸為2^AxSIZE[2:0]

ARSIZE[2:0]:讀地址通道突發尺寸

AWSIZE[2:0]:寫地址通道突發尺寸突發類型(AxBURST)

AXI支持三種突發類型:

FIXED(AxBURST[1:0]=0b00):固定突發模式,每次突發傳輸的地址相同,用于FIFO訪問;

INCR(AxBURST[1:0]=0b01):增量突發模式,突發傳輸地址遞增,遞增量與突發尺寸相關(傳輸過程中,地址遞增。增加量取決AxSIZE的值。)

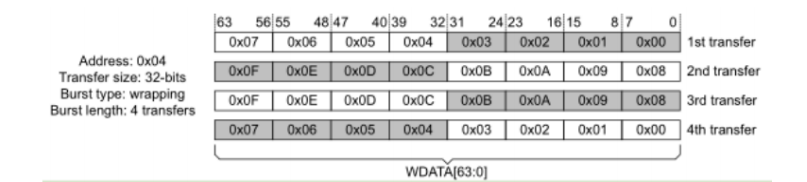

WRAP(AxBURST[1:0]=0b10):回卷突發模式,和增量突發類似,但會在特定高地址的邊界處回到低地址處(傳輸地址不會超出起始地址所在的塊,一旦遞增超出,則回到該塊的起始地址),突發傳輸地址可溢出性遞增,突發長度僅支持2,4,8,16。傳輸首地址和每次傳輸的大小對齊。最低的地址整個傳輸的數據大小對齊。地址空間被劃分為長度[突發尺寸*突發長度]的塊,即回環邊界等于(AxSIZE*AxLEN)。

(2)。存儲類型(AxCACHE)

AXI4可支持不同的存儲類型,AxCACHE[3:0]用于描述不同的存儲類型,如下圖所示

ARCACHE[3:0]AWCACHE[3:0]Memory type

00000000Device Non-bufferable

00010001Device Bufferable

00100010Normal Non-cacheable Non-bufferable

00110011Normal Non-cacheable Bufferable

10100110Write-through No-allocate

1110 (0110)0110Write-through Read-allocate

10101110 (1010)Write-through Write-allocate

11101110Write-through Read and Write-allocate

10110111Write-back No-allocate

1111(0111) 0111Write-back Read-allocate

10111111 (1011)Write-back Write-allocate

11111111Write-back Read and Write-allocate

4.2.數據通道數據結構

(1)。數據選通(WSTRB)

WSTRB的每一位對應數據中的8位(1字節),用于標志數據中的對應字節是否有效。即當WSTRB[n] = 1時,標志數據中WDATA[(8n)+7: (8n)]部分有效。

WSTRB[n:0]對應于對應的寫字節,WSTRB[n]對應WDATA[8n+7:8n]。WVALID為低時,WSTRB可以為任意值, WVALID為高時,WSTRB為高的字節線必須指示有效的數據。

(2)。數據(xDATA)

窄帶傳輸(Narrow transfers)

當主機產生比它數據總線xDATA要窄的傳輸時,為窄帶傳輸,每次使用的數據位數不同,由地址和控制信號決定哪個字節被傳輸:

固定地址的突發下,使用同一段數據信號線

在遞增地址和包裝地址的突發下,使用不同段信號線INCR和WRAP,不同的字節線決定每次burst傳輸的數據,FIXED,每次傳輸使用相同的字節線。

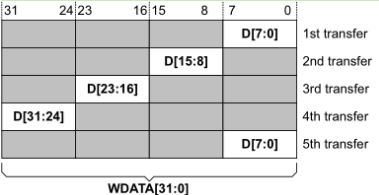

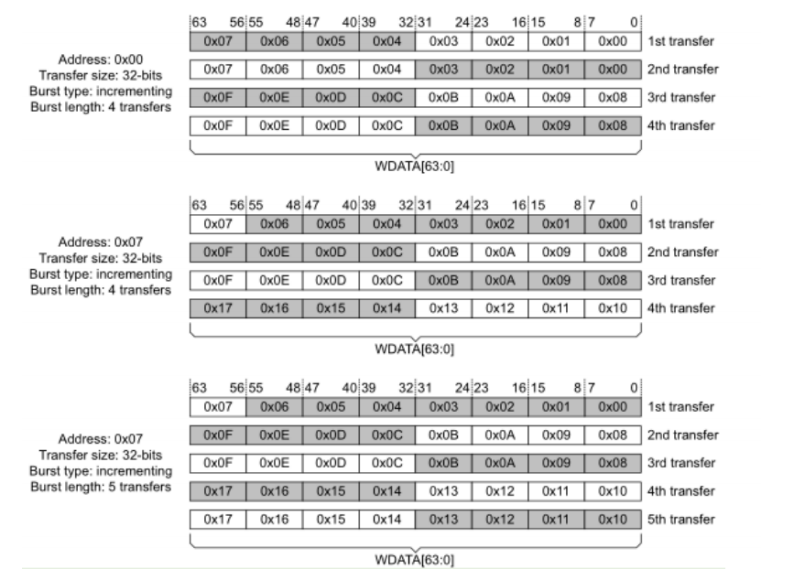

下圖給出了5次突發傳輸,起始地址為0,每次傳輸為8bit,數據總線為32bit,突發類型為INCR。

窄傳輸示例

上圖為地址遞增突發下,在32位數據信號下使用8bit傳輸的窄帶傳輸使用的位數圖。第一次傳輸使用0~7位,第二次使用8~15位,依次遞增;在第五次傳輸時回到開頭使用0~7位。

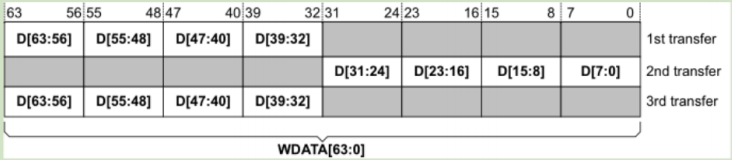

下圖給出3次突發,起始地址為4,每次傳輸32bit,數據總線為64bit。

窄傳輸示例

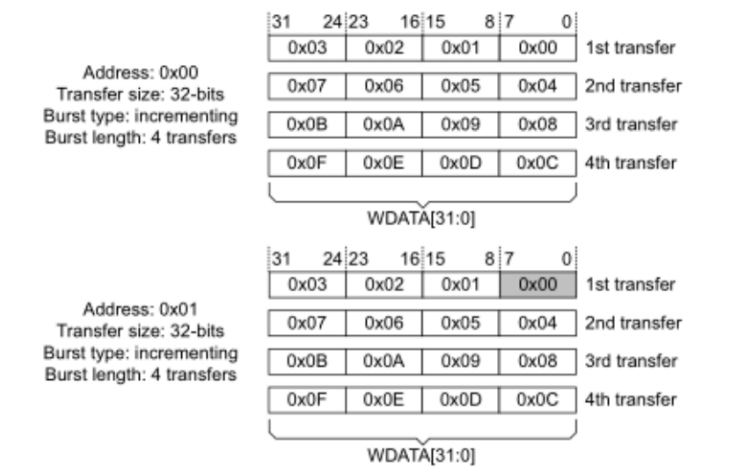

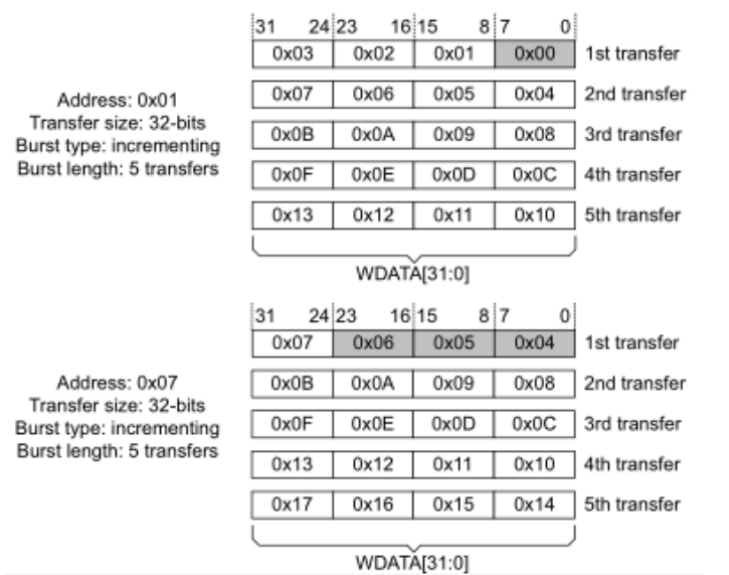

不對齊傳輸(Unaligned transfers)

AXI支持非對齊傳輸。在大于一個字節的傳輸中,第一個自己的傳輸可能是非對齊的。如32-bit數據包起始地址在0x1002,非32bit對齊。主機可以:使用低位地址線來表示非對齊的起始地址;

提供對齊的起始地址,使用字節線來表示非對齊的起始地址。當傳輸位寬超過1byte,起始地址不為數據總線硬件帶寬(byte單位)整數倍時,為不對齊傳輸。不對齊傳輸的時候需要配合數據選通在第一次傳輸時將某幾個byte置為無效,使第二次突發傳輸的起始地址(從機自動計算)為突發尺寸的整數倍。

對齊非對齊傳輸示例1-32bit總線

對齊非對齊傳輸示例2-64bit總線

對齊的回環傳輸示例

讀寫響應結構

讀傳輸的響應信息是附加在讀數據通道上的,寫傳輸的響應在寫響應通道。

RRESP[1:0],讀傳輸

BRESP[1:0],寫傳輸

OKAY(‘b00):正常訪問成功

EXOKAY(’b01):Exclusive 訪問成功

SLVERR(‘b10):從機錯誤。表明訪問已經成功到了從機,但從機希望返回一個錯誤的情況給主機。

DECERR(’b11):譯碼錯誤。一般由互聯組件給出,表明沒有對應的從機地址。

5. AXI-Stream

AXI-Stream,是一種連續流接口,不需要地址線(類似FIFO,一直讀或一直寫就行)。對于這類IP,ARM必須有一個轉換裝置才能對內存映射方式控制,例如AXI-DMA模塊來實現內存映射到流式接口的轉換。

AXI-Stream適用的場合有很多:視頻流處理;通信協議轉換;數字信號處理;無線通信等。其本質都是針對數值流構建的數據通路,從信源(例如ARM內存、DMA、無線接收前端等)到信宿(例如HDMI顯示器、音頻輸出等)構建起連續的數據流。這種接口適合做實時信號處理。

用戶其實不需要對AXI時序了解太多,因為Xilinx已經將和AXI時序有關的細節都封裝起來,官方IP和向導生成的自定義IP,用戶只需要關注自己的邏輯實現即可

AXI4-Stream協議是一種用來連接需要交換數據的兩個部件的標準接口,它可以用于連接一個產生數據的主機和一個接受數據的從機。當然它也可以用于連接多個主機和從機。該協議支持多種數據流使用相同共享總線集合,允許構建類似于路由、寬窄總線、窄寬總線等更為普遍的互聯。

AXI4-Stream接口比較重要的信號線:

ACLK:時鐘線,所有信號都在ACLK上升沿被采樣;

ARESETn:復位線,低電平有效;

TVALID:主機數據同步線,為高表示主機準備好發送數據;

TREADY:從機數據同步線,為高表示從機準備好接收數據;這兩根線完成了主機與從機的握手信號,一旦二者都變高有效,數據傳輸開始。

TDATA:數據線,主機發送,從機接收。

TKEEP:主機數據有效指示,為高代表對應的字節為有效字節,否則表示發送的為空字節。

TLAST:主機最后一個字指示,下一clk數據將無效,TVALID將變低。

TID,TDEST,TUSER均為多機通信時的信號,不予考慮。

利用AXI總線做轉換,可以把PS里DDR4的內容以Stream形式發出去,例如以固定速度送往DA,完成信號發生器的設計;

ZYNQ的PS部分是ARM CortexA9系列,支持AXI4,AXI-Lite總線。PL部分也有相應AXI總線接口,這樣就能完成PS到PL的互聯。僅僅這樣還不夠,需要PL部分實現流式轉換,即AXI-Stream接口實現。

Xilinx提供的從AXI到AXI-Stream轉換的IP核有:AXI-DMA,AXI-Datamover,AXI-FIFO-MM2S以及AXI-VDMA等。

AXI-DMA:實現從PS內存到PL高速傳輸高速通道AXI-HP到AXI-Stream的轉換;

AXI-FIFO-MM2S:實現從PS內存到PL通用傳輸通道AXI-GP到AXI-Stream的轉換;

AXI-Datamover:實現從PS內存到PL高速傳輸高速通道AXI-HP到AXI-Stream的轉換,只不過這次是完全由PL控制的,PS是完全被動的;

AXI-VDMA:實現從PS內存到PL高速傳輸高速通道AXI-HP到AXI-Stream的轉換,只不過是專門針對視頻、圖像等二維數據的。

AXI總線和接口的區別:

總線是一種標準化接口,由數據線、地址線、控制線等構成,具有一定的強制性。接口是其物理實現,即在硬件上的分配。在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI-Lite或AXI4轉接。PS與PL之間的物理接口有9個,包括4個AXI-GP接口和4個AXI-HP接口、1個AXI-ACP接口,均為內存映射型AXI接口。

編輯:lyn

-

總線接口

+關注

關注

0文章

83瀏覽量

30782 -

AXI

+關注

關注

1文章

128瀏覽量

16712

原文標題:AXI總線知多少?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

I2C總線數據包結構詳解

AMBA AXI4接口協議概述

【CAN總線知識】深度解析CAN-FD與CAN協議的差別

CAN底層報文抓到了,卻不知怎么解析?以及如何看到信號運行狀態?

EEPROM讀寫程序詳解

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

有關PL端利用AXI總線控制PS端DDR進行讀寫(從機wready信號一直不拉高)

SoC設計中總線協議AXI4與AXI3的主要區別詳解

PCIe-AXI-Cont用戶手冊

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

對AXI總線知識詳解解析

對AXI總線知識詳解解析

評論