引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。這些網絡被設計成具有低偏移和低占空比失真、低功耗和改進的抖動容限。它們也被設計成支持非常高頻率的信號。了解全局時鐘的信號路徑可以擴展對各種全局時鐘資源的理解。全局時鐘資源和網絡由以下路徑和組件組成:

時鐘樹和網絡:GCLK

時鐘區域

全局時鐘緩沖器

1. 時鐘樹和網絡:GCLK

7系列FPGA時鐘樹設計用于低偏差和低功耗操作,任何未使用時鐘的分支都會被斷開。時鐘樹還可用于驅動邏輯資源,如復位或時鐘啟用,這主要用于高扇出/負載網絡。在7系列FPGA結構中,全局時鐘線的引腳訪問不限于邏輯資源時鐘引腳。全局時鐘線可以驅動CLB中除CLK引腳以外的引腳(例如:控制引腳SR和CE)。需要非常快速的信號連接和大負載/扇出的應用程序可以從該架構中獲益。

2. 時鐘域

7系列器件通過使用時鐘區域改善時鐘分布。每個時鐘區域最多可以有12個全局時鐘域。這12個全局時鐘可以由單片器件或SLR中的32個全局時鐘緩沖器的任意組合驅動。時鐘區域的尺寸固定為50個CLB高(50個IOB),跨越die的左側或右側。在7系列器件中,時鐘主干線將器件分成左側或右側。通過固定時鐘區域的尺寸,較大的7系列器件可以有更多的時鐘區域。7系列FPGA提供1到24個時鐘區域。

3. 全局時鐘緩沖器

在7系列器件中有多達32個全局時鐘緩沖器。CCIO輸入可以直接連接到器件同一半的任何全局時鐘緩沖器。每個差分時鐘管腳對可以連接到PCB上的差分時鐘或單端時鐘。當用作差分時鐘輸入時,直接連接來自差分輸入管腳對的P側。當用作單端時鐘輸入時,必須使用管腳對的P側,因為直接連接只存在于該管腳上。有關管腳命名約定,請參閱UG475:7系列FPGA封裝和引腳輸出規范。如果單端時鐘連接到差分管腳對的P側,則N端不能用作另一個單端時鐘管腳。但是,它可以用作用戶I/O。器件上半部分的CMT只能驅動器件上半部分的BUFG,下半部分的CMT只能驅動下半部分的BUFG。類似地,只有器件的同一半中的BUFG可以用作對器件同一半中的CMT反饋。當CMT列擴展到同時包含GT和I/O列的區域時,千兆收發器(GTs)只能直接連接到MMCMs/PLL。Virtex-7T和Virtex-7XT器件有這些完整的列。Spartan-7、Artix-7、Kintex-7和Zynq-7000器件中的GT和CMT只能使用BUFHs(首選)或BUFGs進行連接。全局時鐘緩沖器允許各種時鐘/信號源訪問全局時鐘樹和網絡。輸入到全局時鐘緩沖器的可能來源包括:

時鐘輸入

在器件同一半區域的時鐘管理塊(CMT)驅動BUFG

相鄰全局時鐘緩沖器輸出(BUFGs)

通用互連

區域時鐘緩沖器(BUFRs)

7系列FPGA時鐘輸入可以通過時鐘主干列中的垂直時鐘網絡間接地驅動全局時鐘緩沖器。32個BUFG被分成兩組,每組16個BUFGs,分別位于器件的頂部和底部。直接連接到BUFGs的任何資源(例如,GTX收發器)都有一個頂部/底部限制。例如,頂部的每個MMCM只能驅動設備頂部的16個BUFGs。同樣,底部的MMCMs驅動底部的16個BUFGs。

所有全局時鐘緩沖器可以驅動7系列設備中的所有時鐘區域。然而,在一個時鐘區域內只能驅動12個不同的時鐘。時鐘緩沖器被設計成具有兩個時鐘輸入的同步或異步glitch-free2:1多路復用器。BUFG級聯有一個專用路徑(路由資源),允許兩個以上的時鐘輸入選擇。7系列FPGA控制引腳提供廣泛的功能和強大的輸入切換。在7系列FPGA時鐘結構中,BUFGCTRL多路復用器和所有派生器可以級聯到器件上半部分和下半部分16個BUFGMUX組內的相鄰時鐘緩沖器,有效地在上半部分創建一個16個BUFGMUX(BUFGCTRL多路復用器)環,在下半部分形成另一個16個環。圖1顯示了級聯BUFG的簡化圖。

圖1、級聯BUFGs以下小節詳細介紹了7系列FPGA時鐘緩沖器的各種配置、原語和使用模型。

3.1 全局時鐘緩沖器原句

表1中的原句是全局時鐘緩沖器的不同配置。ISE或Vivado設計工具管理所有這些原語的配置,約束指南描述了LOC約束。

表1、全局時鐘緩沖器原句

BUFGCTRL

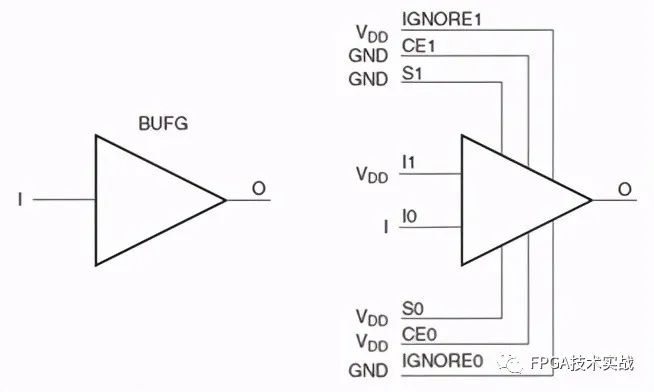

BUFGCTRL原句框圖如圖2所示,它可以實現兩路異步時鐘切換。所有其他全局緩沖語句都可以由BUFGCTRL的某種配置得到。BUFGCTRL有四個選擇端口:S0、S1、CE0和CE1,另外還有兩個附件的控制線,IGNORE0和IGNORE1。這六個信號用于控制輸入I0和I1。

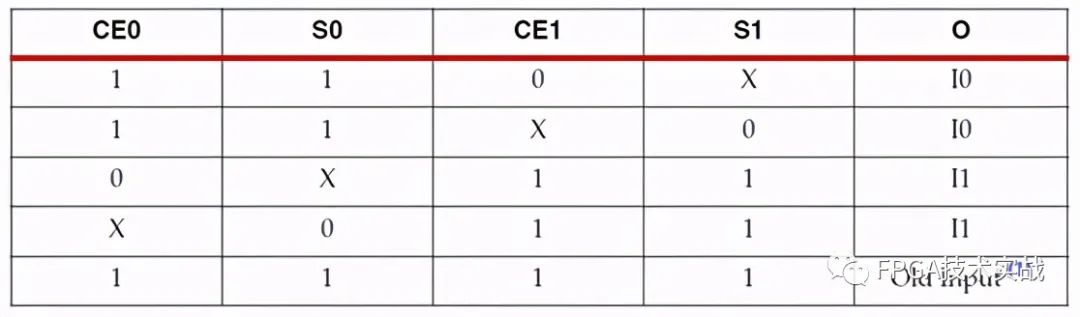

圖2、 BFUGCTRL原句BUFGCTRL用于在兩路時鐘輸入之間切換,而不會產生毛刺。當當前選擇的時鐘在S0和S1改變后從高電平轉換到低電平時,輸出保持在低電平,直到另一個(待選擇的)時鐘從高電平轉換到低電平。然后新的時鐘開始驅動輸出,BUFGCTRL的默認配置是下降沿敏感型,在輸入切換之前保持在低位。BUFGCTRL還可以對上升沿敏感,并在輸入切換之前使用INIT_OUT屬性保持在高極性。在某些應用中,上述條件是不可取的。斷言IGNORE引腳將繞過BUFGCTRL來檢測在兩個時鐘輸入之間切換的條件。換句話說,斷言IGNORE會導致MUX在選擇管腳更改時切換輸入。當選擇引腳改變時,IGNORE0使輸出立即從I0輸入切換,而當選擇引腳改變時,IGNORE1使輸出立即從I1輸入切換。選擇一個輸入時鐘需要一個“選擇”對(S0和CE0,或S1和CE1)被斷言為高。如果S或CE沒有被斷言為高,則所需的輸入將不會被激活選定。在正常運行時,S和CE對(所有四條選擇線)都不應同時斷言高。通常,“選擇”對中只有一個管腳用作選擇線,而另一個管腳系在高處。真值表如表2所示。

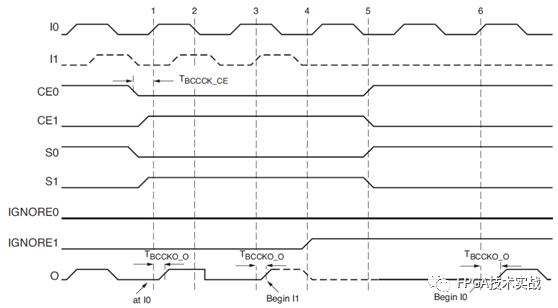

表2、時鐘資源真值表雖然S和CE都用于選擇所需的輸出,但建議只有S用于無故障切換。這是因為當使用CE切換時鐘時,時鐘選擇的變化可能比使用S快。CE引腳的建立/保持時間會導致時鐘輸出出現毛刺。另一方面,使用S引腳可以在兩個時鐘輸入之間切換,而不考慮設置/保持時間。因此,使用S來切換時鐘不會導致毛刺。請參見BUFGMUX_ CTRL。圖3中的時序圖說明了使用BUFGCTRL原語的各種時鐘切換條件。

圖3、BUFGCTRL原語的時序圖在事件1之前,輸出O使用輸入I0;BUFGCTRL的其他功能包括:

I0和I1輸入的預選在配置之后但在設備運行之前進行。

配置后的初始輸出可選擇為高或低。

僅使用CE0和CE1的時鐘選擇(S0和S1綁定高)可以更改時鐘選擇,而無需等待先前選擇的時鐘從高到低的轉換。

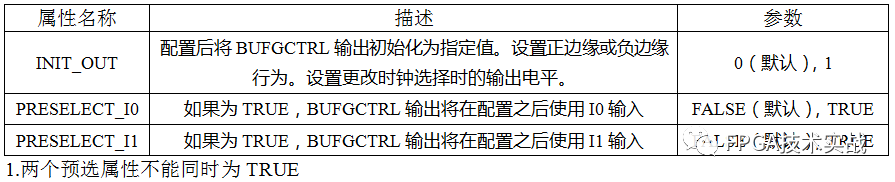

表3概括了BUFGCTRL原句的屬性。

表3 BUFGCTRL屬性

BUFG

BUFG是一個時鐘緩沖器,具有一個時鐘輸入和一個時鐘輸出。這個原語基于BUFGCTRL,有些管腳連接到邏輯高或低。圖2-5說明了BUFG和BUFGCTRL的關系。可以手動放置約束的位置。

圖4、BUFG和BUFGCTRLBUFG時序圖如圖5所示。圖中顯示了BUFG引入的時鐘延遲TBCCKO_O

圖5、 BUFG時序圖

BUFGCE和BUFGCE_1

與BUFG不同,BUFGCE是一個具有一個時鐘輸入、一個時鐘輸出和一條時鐘使能線的時鐘緩沖器。這個原語基于BUFGCTRL,有些管腳連接到邏輯高或低。圖6說明了BUFGCE和BUFGCTRL的關系。LOC約束可用于手動放置BUFGCE和BUFGCE_ 1位置。

圖6、 BUFGCE和BUFGCTRLBUFGCE的切換條件類似于BUFGCTRL。如果CE輸入在進入上升時鐘邊緣之前為低電平,則隨后的時鐘脈沖不會通過時鐘緩沖器,并且輸出保持低電平。在進入時鐘高脈沖期間,CE的任何電平變化在時鐘轉換為低之前都沒有影響。當時鐘被禁用時,輸出保持低。但是,當時鐘被禁用時,它將完成時鐘高脈沖。由于時鐘使能線路使用BUFGCTRL的CE引腳,因此選擇信號必須滿足建立時間要求。違反此建立時間可能會導致毛刺。圖7說明了BUFGCE的時序圖。

圖7、 BUFGCE的時序圖BUFGCE_1與BUFGCE類似,只是其開關條件不同。如果CE輸入在進入下降時鐘邊緣之前是低的,則隨后的時鐘脈沖不通過時鐘緩沖器,并且輸出保持高。在進入時鐘低脈沖期間,CE的任何電平變化在時鐘變高之前都沒有影響。當時鐘被禁用時,輸出保持高電平。但是,當時鐘被禁用時,它將完成時鐘低脈沖。

圖8、BUFGCE_1的時序圖

BUFGMUX和BUFGMUX_1

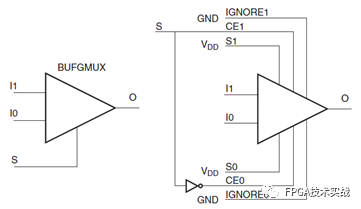

BUFGMUX是一個具有兩個時鐘輸入、一個時鐘輸出和一條選擇線的時鐘緩沖器。這個原語基于BUFGCTRL,有些管腳連接到邏輯高位或高位低。圖9說明了BUFGMUX和BUFGCTRL的關系。LOC約束可用于手動放置BUFGMUX和BUFGCTRL位置。

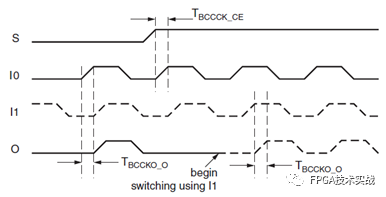

圖9、 BUFGMUX和BUFGCTRL由于BUFGMUX使用CE管腳作為選擇管腳,因此在使用選擇管腳時,必須滿足建立時間要求。違反此建立時間可能會導致毛刺。BUFGMUX的開關條件與上的CE引腳相同BUFGCTRL.圖圖10顯示了BUFGMUX的時序圖。

圖10、BUFGMUX時序圖

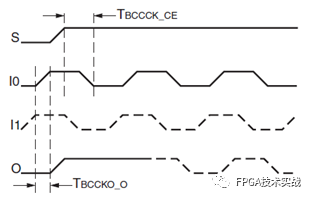

BUFGMUX_1對上升沿敏感,在輸入開關之前保持在高電平。圖11顯示了BUFGMUX_ 1的時序圖。LOC約束可用于手動放置BUFGMUX和BUFGMUX_1位置。

圖10、BUFGMUX_1時序圖

表3、 BUFGMUX屬性

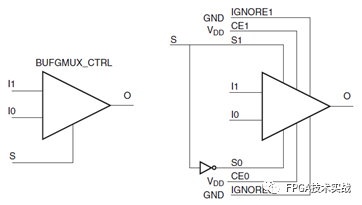

BUFGMUX_CTRL

BUFGMUX_CTRL替換了BUFGMUX_VIRTEX4遺留版本基元.BUFGMUX_CTRL是一個具有兩個時鐘輸入、一個時鐘輸出和一條選擇線的時鐘緩沖區。這個原語基于BUFGCTRL,有些管腳連接到邏輯高或低。圖12顯示了BUFGMUX_CTRL和BUFGCTRL的關系。

圖12、BUFGMUX_CTRL和BUFGCTRLCTRL和MUX選擇管腳。S可以隨時切換而不會引起故障。S上的建立/保持時間用于確定在切換到新時鐘之前,輸出是否將通過先前選擇的時鐘的額外脈沖。如果S如圖2-14所示在設置時間TBCCCK_S之前和I0從高變低之前發生變化,則輸出將不會傳遞額外的I0脈沖。如果S在S的保持時間后發生變化,則輸出將傳遞一個額外的脈沖。如果S違反建立/保持要求,輸出可能會傳遞額外的脈沖,但不會出現故障。在任何情況下,輸出將在慢時鐘的三個時鐘周期內更改為新時鐘。S0和S1的建立/保持要求與時鐘下降沿有關,而不是與CE0和CE1的上升沿有關。

BUFGMUX_CTRL的切換條件與BUFGCTRL.圖13顯示了BUFGMUX_CTRL的時序圖。

圖13、BUFGMUX_CTRL時序圖BUFGMUX_CTRL原語的其他功能包括:

配置后預選I0和I1輸入。

初始輸出可在配置后選擇為高或低

原文標題:Xilinx 7系列FPGA架構之時鐘資源(三)

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605999 -

Xilinx

+關注

關注

71文章

2171瀏覽量

122134 -

時鐘

+關注

關注

11文章

1746瀏覽量

131799

原文標題:Xilinx 7系列FPGA架構之時鐘資源(三)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA架構中的全局時鐘資源介紹

FPGA架構中的全局時鐘資源介紹

評論