原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處(www.alinx.com)。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

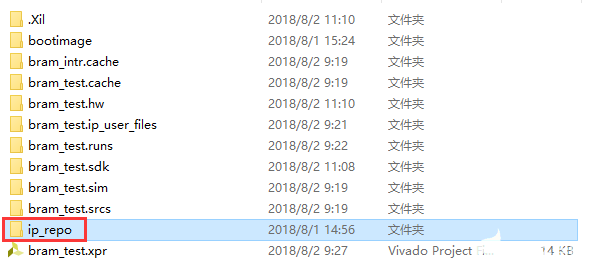

實驗Vivado工程目錄為“bram_test /vivado”。

實驗vitis工程目錄為“bram_test /vitis”。

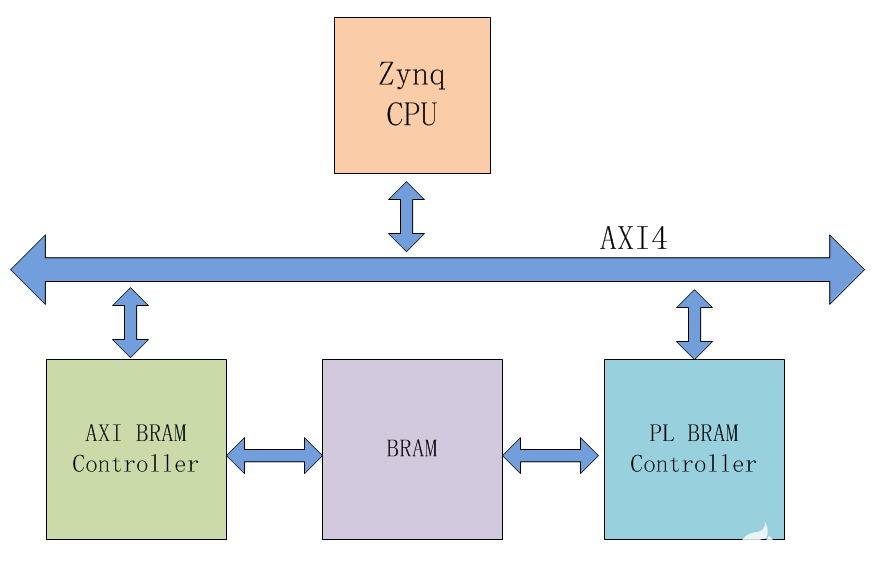

有時CPU需要與PL進行小批量的數據交換,可以通過BRAM模塊,也就是Block RAM實現此要求。本章通過Zynq的GP Master接口讀寫PL端的BRAM,實現與PL的交互。在本實驗中加入了自定義的FPGA程序,并利用AXI4總線進行配置,通知其何時讀寫BRAM。

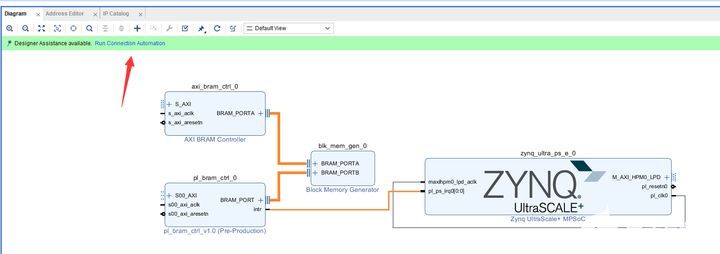

以下為本實驗原理圖,CPU通過AXI BRAM Controller讀取BRAM數據,CPU僅配置自定義的PL BRAM Controller的寄存器,不通過它讀寫數據。

FPGA工程師工作內容

以下為FPGA工程師負責內容。

1. 硬件環境搭建

以“ps_hello”為基礎,另存為一份工程,并配置打開ZYNQ的中斷

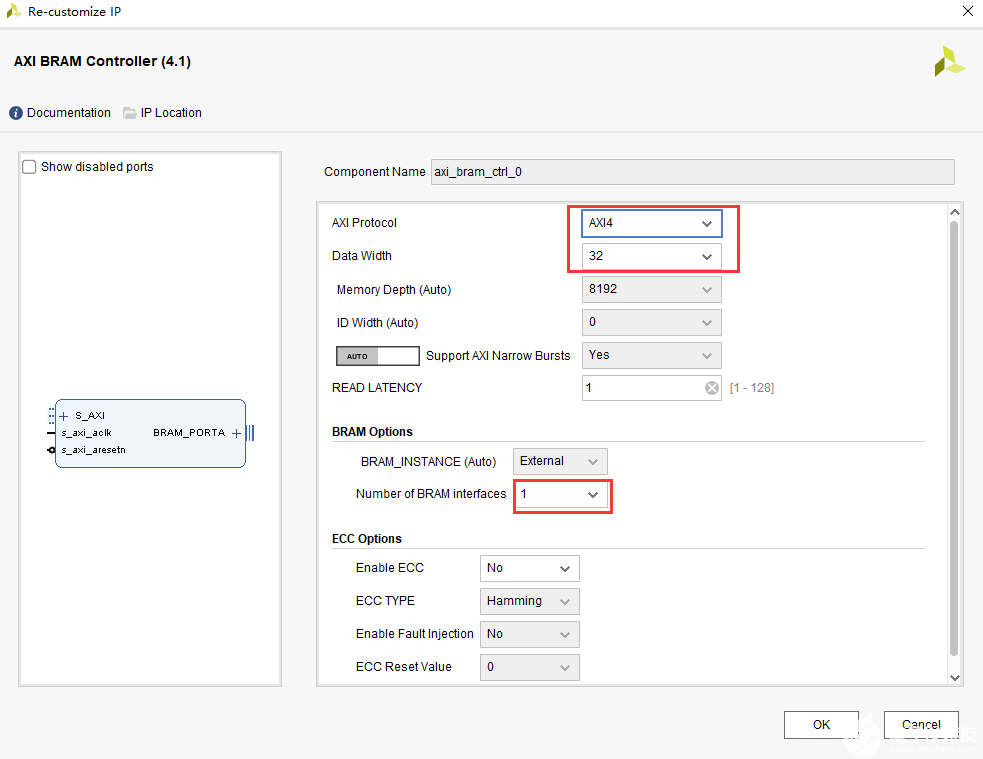

1)首先添加AXI BRAM Controller模塊,用于PS端控制BRAM,雙擊打開配置,連接AXI總線,可用于讀寫BRAM模塊,AXI模式設置為AXI4,數據寬度設置為32位,memory depth不在這里設置,需要在Address Editor里設置。BRAM端口數量設置為1個,用于連接雙口RAM的PORTA。不使能ECC功能。

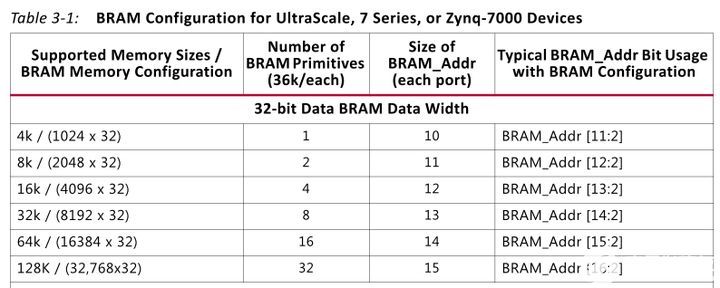

由于AXI4總線為字節詢址,BRAM數據寬度設置也是32位,同樣都是32位數據寬度,因此在映射到BRAM地址時,需要按4字節詢址,即去掉最后兩位,下圖為BRAM控制器與BRAM的映射關系。

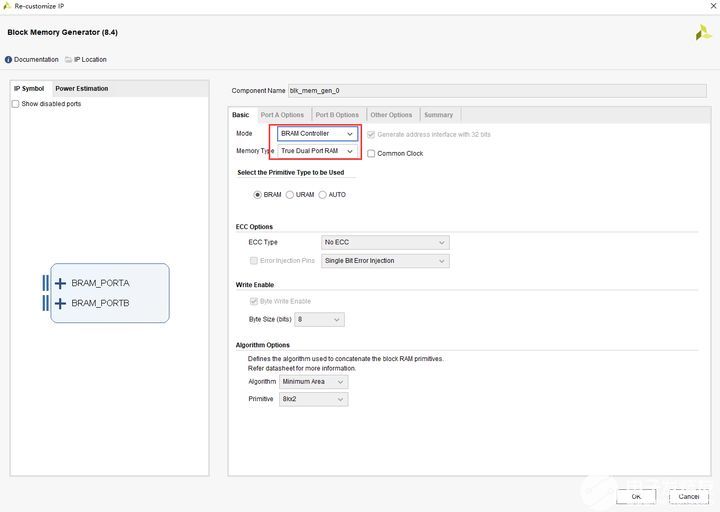

2)添加BRAM模塊,BRAM設置如下,有兩種模式選擇,standalon模式,此模式可以自由配置RAM的數據寬度和深度。BRAM Controller模式,此模式下地址線和數據端口默認為32位,本實驗因為用到了BRAM控制器,因此選擇BRAM Controller模式。Memory類型選擇雙口RAM,一端連BRAM控制器,一端連PL RAM控制器。

3) 添加自定義的PL RAM控制器pl_ram_ctrl,功能很簡單,start信號有效后開始讀取BRAM的數據,可通過ILA邏輯分析儀觀察讀取的數據,PL RAM控制器讀BRAM結束后,開始向BRAM寫數據,寫完數據使能intr信號,即中斷信號,CPU即可讀取BRAM的數據。將PL控制器信號與BRAM的PORTB連接。自定義IP在ip_repo文件夾中。

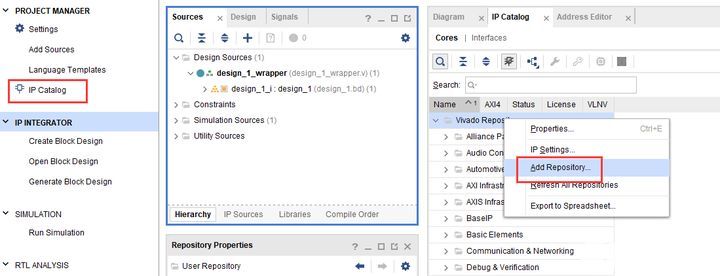

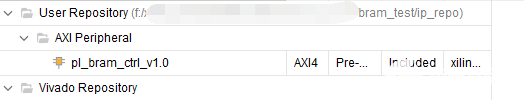

如果想添加自定義IP到IP庫中,點擊IP Catalog,在Vivado Repository右鍵點擊Add Repository

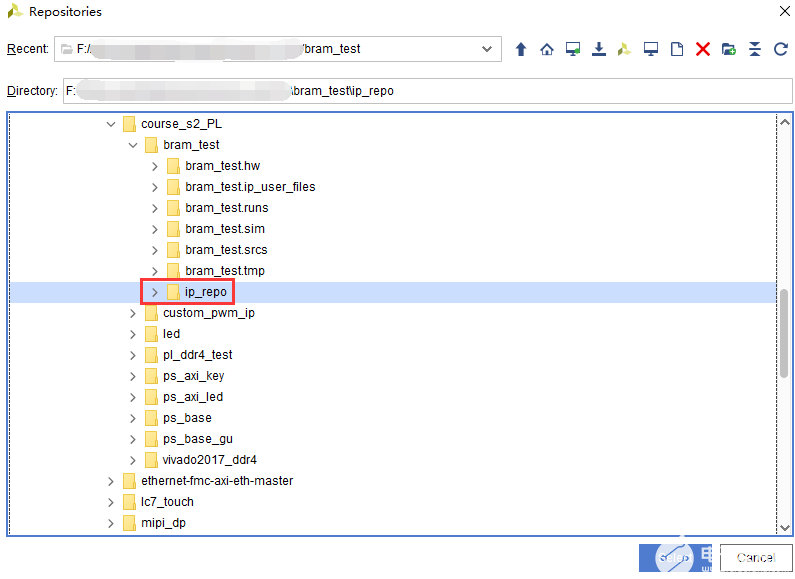

找到自定義IP所在文件夾,點擊Select

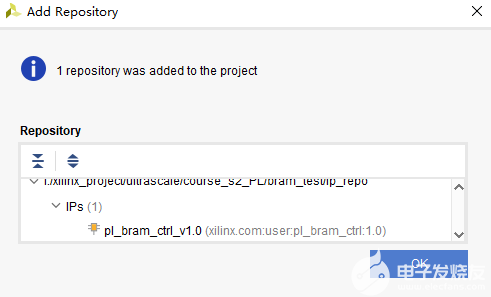

跳出窗口,選擇IP,點擊OK

即可看到,出現了剛添加的IP

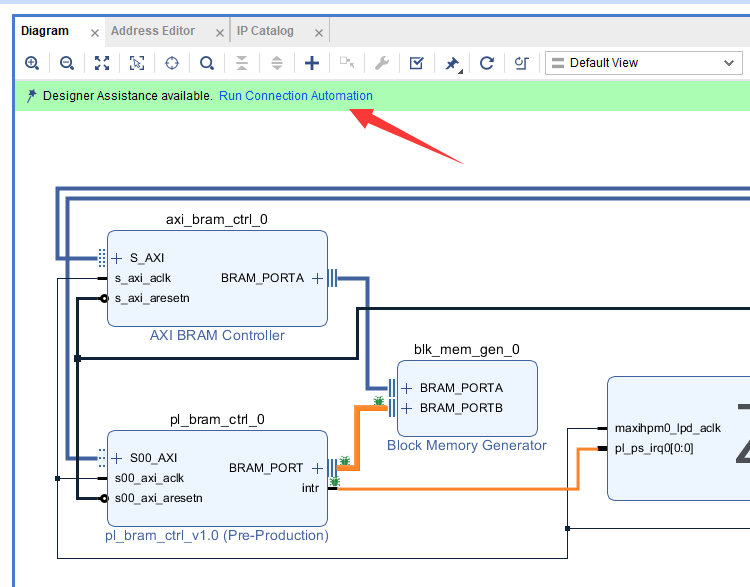

4)連接AXI BRAM Controller的BRAM_PORTA到BRAM的PORTA,連接pl_bram_ctrl的BRAM_PORT到BRAM的PORTB。連接pl_bram_ctrl模塊的中斷信號intr到ZYNQ的中斷口。并點擊自動連接

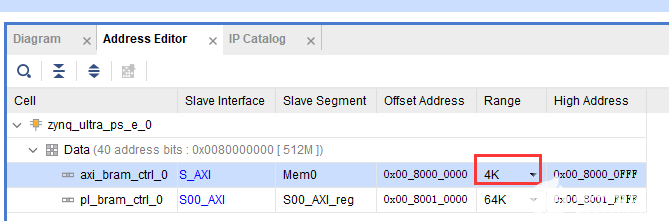

5)在Address Editor里選擇BRAM詢址大小,如設置4K空間,即可詢址BRAM空間為1K深度。

Block Design添加邏輯分析儀方法

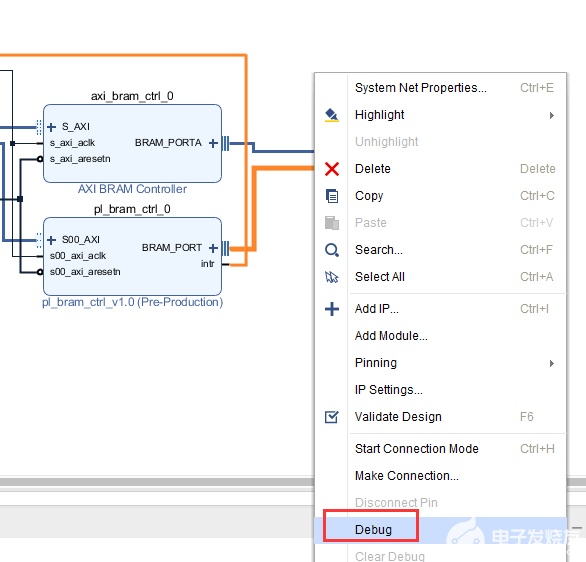

1)再介紹一種添加邏輯分析儀的方法,選中BRAM_PORT總線和intr中斷,右鍵選擇Debug

2)可以看到總線上多了小昆蟲,點擊Run Connection Automation,自動連接

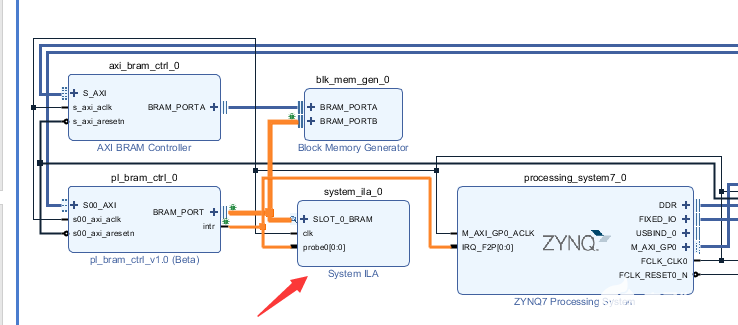

自動添加了一個ILA模塊,并且有一個總線接口,一個信號接口

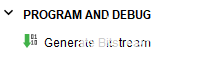

3)保存設計,之后點擊Generate Bitsream生成bit文件,并導出Hardware信息。

軟件工程師工作內容

以下為軟件工程師負責內容。

2. Vitis程序開發

1)程序設計流程為:輸入起始地址和長度CPU通過BRAM控制器寫入BRAM數據通知PL控制器讀取BRAM數據PL內部讀完后向相同位置寫入數據,初始數據由CPU告知寫完后使能write_end信號,觸發GPIO中斷中斷讀取BRAM數據,打印顯示

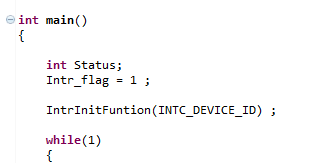

2)進入Vitis后,在Vitis下新建項目,已經準備好程序。程序也比較簡單,首先中斷設置

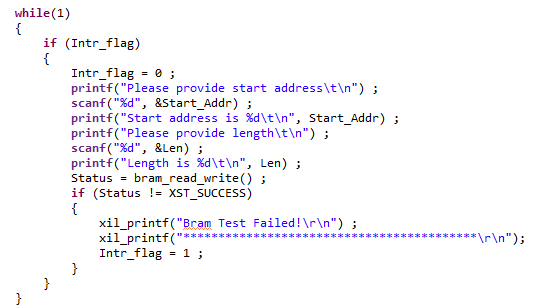

3)While語句中需要輸入起始地址和長度,之后調用bram_write函數

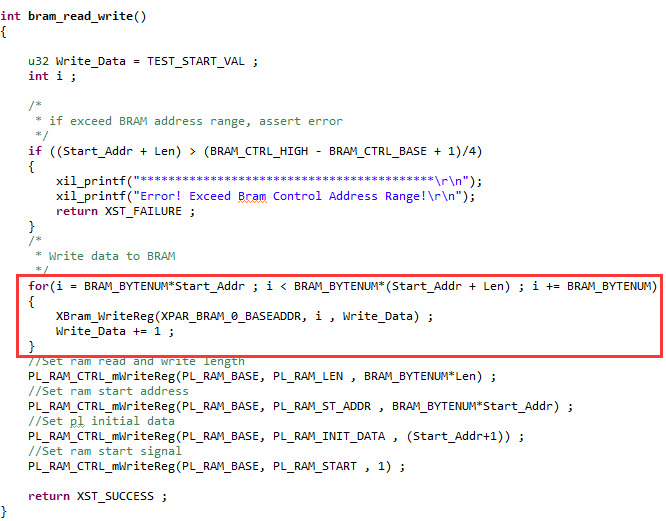

4)在bram_read_write();函數里先通過BRAM控制器寫入數據,數據初值為TEST_START_VAL,之后配置PL RAM控制器參數,有長度,起始地址,初始數據,以及開始信號。并在函數中判斷測試長度是否超出BRAM控制器地址范圍,如果超出,會報錯,需要重新輸入地址和長度。

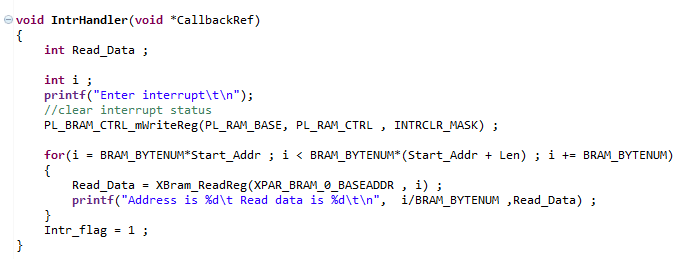

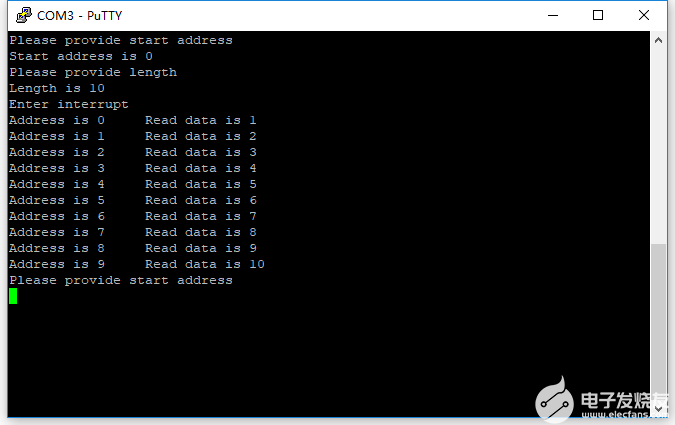

5)中斷服務程序中,BRAM控制器讀取BRAM的數據,并打印

3. 實驗現象

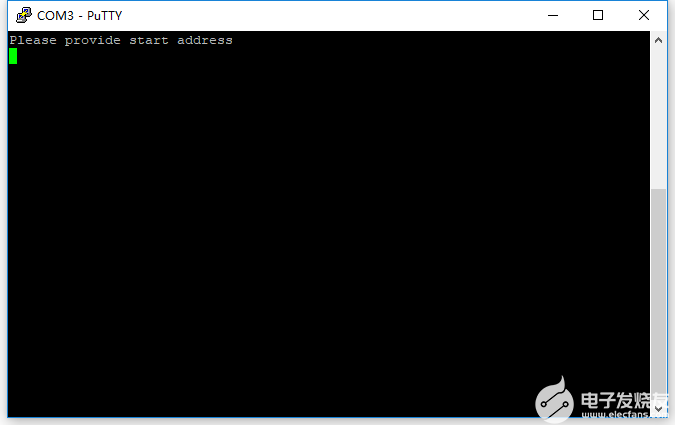

1)打開串口

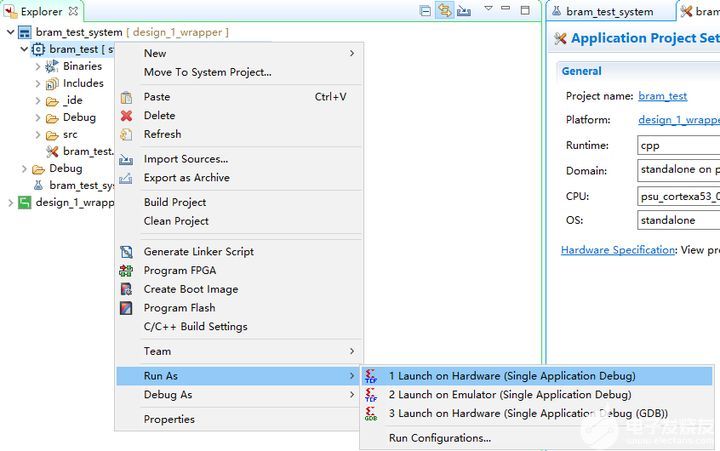

2)通過Run Configurations下載程序

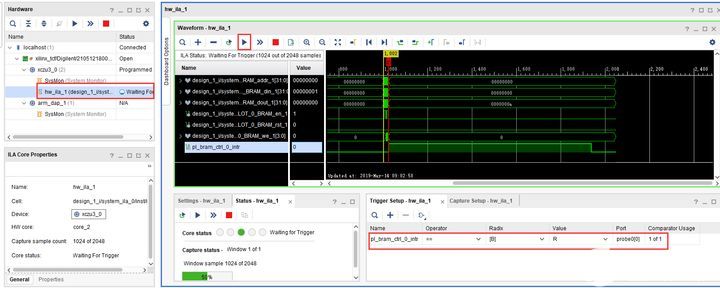

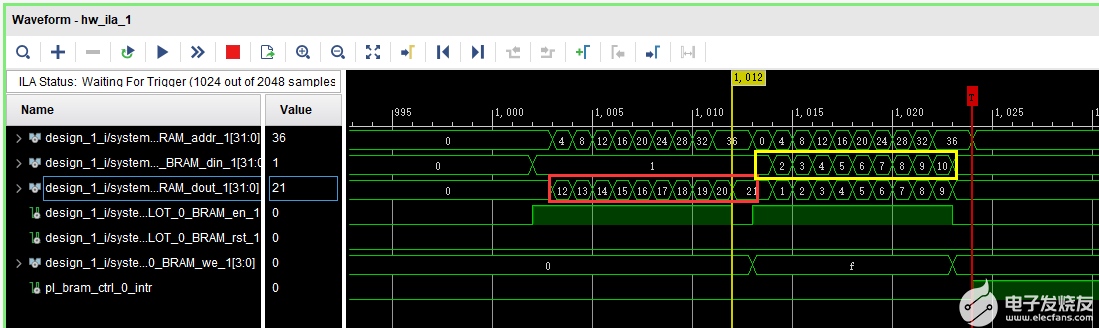

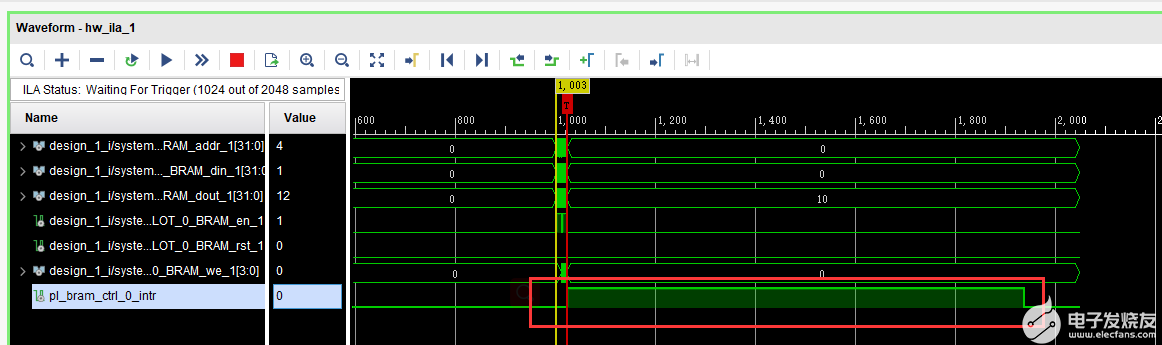

3)打開Vivado的Hardware Manager(與PL端聯合調試),設置將intr中斷信號作為觸發信號,選擇上升沿觸發,點擊開始按鈕,可以看到hw_ila_1變成了Waiting for trigger狀態

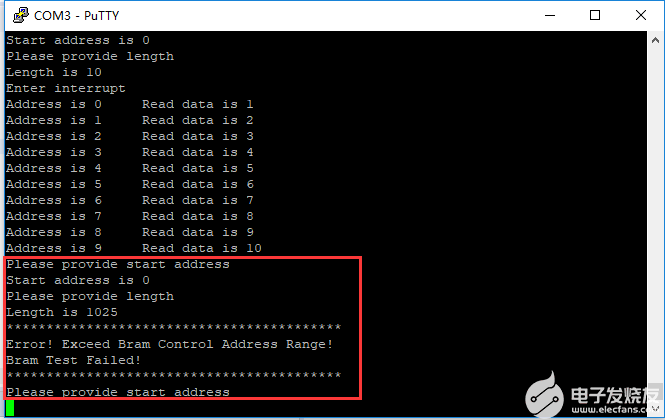

4)在串口軟件中,輸入起始地址,由于BRAM詢址為1K,那么可以設置為0~1023,長度設置為1~1024,注意起始地址+長度不要超過1024,因為超出了詢址空間。

5)輸入的數據為十進制數,輸入結束按回車

6)打開ILA邏輯分析儀,可以看到已經觸發,首先是PL控制器從BRAM讀數據,之后是寫數據,可以看到紅色為PL讀出的BRAM數據,正是CPU寫入的數據,從12開始,共10個數據,PL寫入的數據為黃色部分從1開始,共10個數據,正與上圖CPU讀BRAM的數據相符。

同樣也能看到中斷信號的狀態

7)如果超出范圍,打印錯誤信息,需要重新輸入有效信息

4. 本章小結

以上就是PS與PL通過BRAM實現低帶寬數據交互的實驗,兩者通過GP口進行數據互連,可以實現小批量的數據交互。

知識點為邏輯分析儀的使用,中斷的使用,自定義IP等。

-

FPGA

+關注

關注

1630文章

21797瀏覽量

606013 -

cpu

+關注

關注

68文章

10904瀏覽量

213020 -

Zynq

+關注

關注

10文章

610瀏覽量

47296 -

MPSoC

+關注

關注

0文章

199瀏覽量

24322 -

BRAM

+關注

關注

0文章

41瀏覽量

11016

發布評論請先 登錄

相關推薦

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

閑話Zynq UltraScale+ MPSoC(連載1)

閑話Zynq UltraScale+ MPSoC(連載5)

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

Zynq UltraScale+ MPSoC的發售消息

米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Zynq UltraScale+ MPSoC中的隔離方法

Zynq UltraScale+ MPSoC的隔離設計示例

Zynq UltraScale+ MPSoC驗證數據手冊

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM實現PS與PL交互

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM實現PS與PL交互

評論