本文轉(zhuǎn)載自:VagueCheung的博客

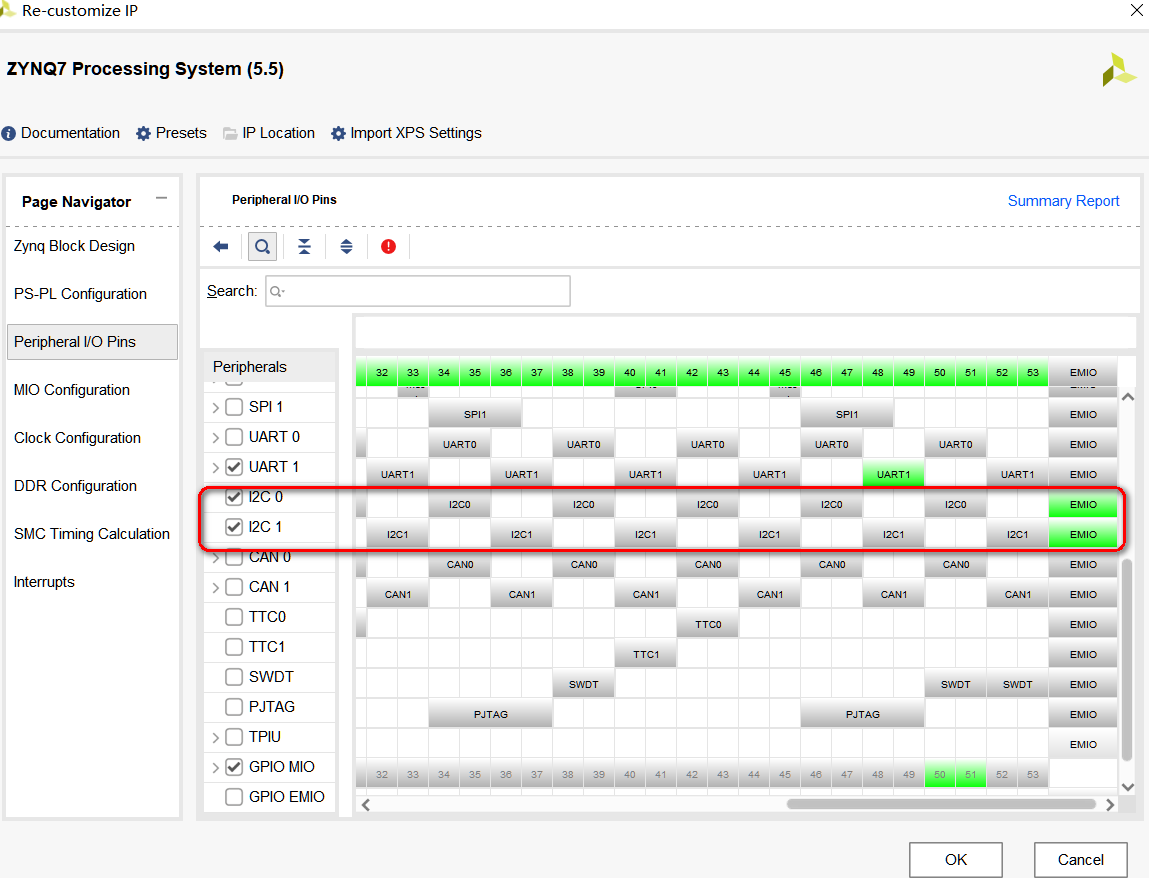

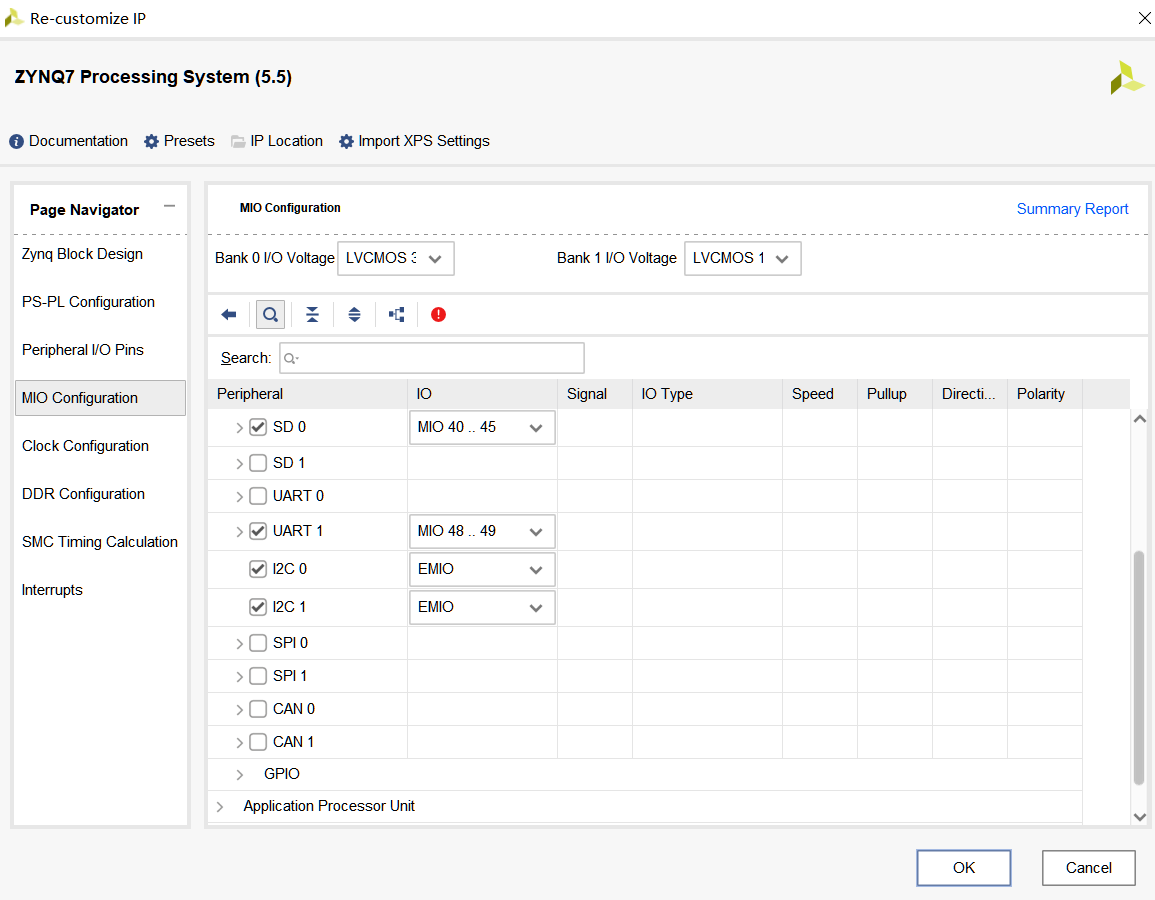

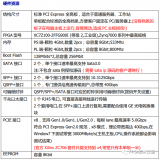

ZYNQ7000系列FPGA的PS自帶兩個(gè)IIC接口,接口PIN IO可擴(kuò)展為EMIO形式即將IO約束到PL端符合電平標(biāo)準(zhǔn)的IO(BANK12、BANK13、BANK34、BANK35);

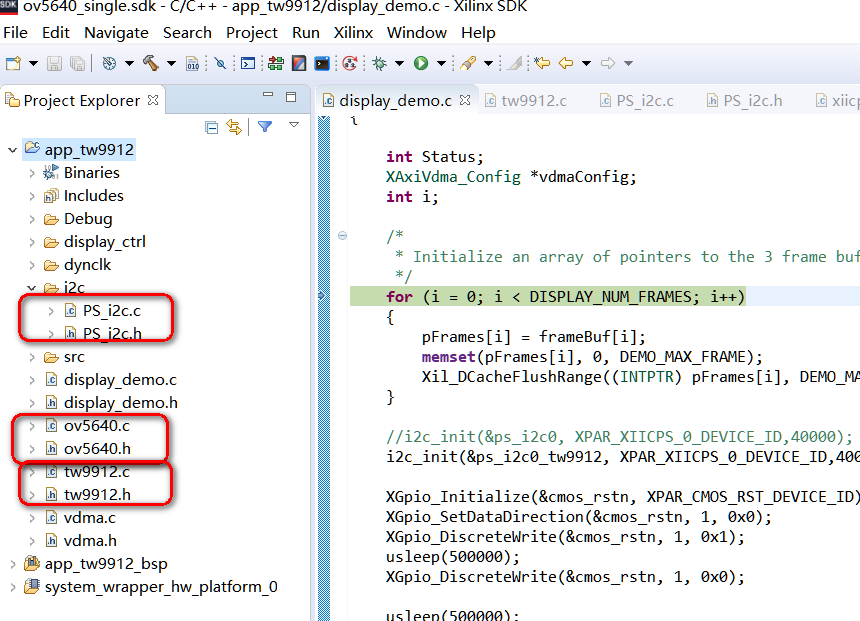

SDK中需要對IIC接口進(jìn)行初始化在黑金和米聯(lián)的例程里為了方便用戶使用,對IIC和外設(shè)設(shè)備分別創(chuàng)建了相應(yīng)的文件方便用戶開發(fā)。

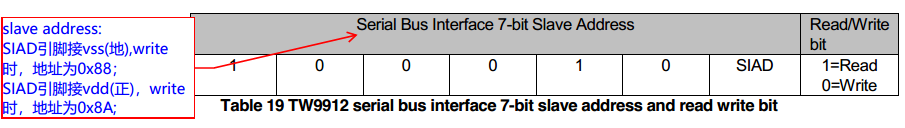

特別注意每個(gè)外設(shè)設(shè)備都會有自己的slave address;而xilinx官方給出的IIC驅(qū)動中給出的從設(shè)備的地址是7bit模式(IIC總線上的器件一般為8位地址位,去掉低位一位廣播位,最多可掛載127個(gè)設(shè)備),在IIC進(jìn)行寫操作時(shí)注意要將設(shè)備原有的salve address轉(zhuǎn)化成7bit模式;否則從設(shè)備將無法給予應(yīng)答。

例如tw9912

在SDK中IIC進(jìn)行寫操作時(shí)。從設(shè)備地址slave address就應(yīng)設(shè)置為0x44/0x45;

IIC總線數(shù)據(jù)傳輸速率(波特率)快速模式下可達(dá)到400kbit/s;

審核編輯 黃昊宇

-

IIC接口

+關(guān)注

關(guān)注

0文章

23瀏覽量

11735 -

Zynq-7000

+關(guān)注

關(guān)注

3文章

144瀏覽量

36905

發(fā)布評論請先 登錄

相關(guān)推薦

當(dāng)ADC3663的LVDS輸出給到ZYNQ-7000的LVDS接收這兩者之間可以直連嗎?

ZYNQ核心板學(xué)習(xí)筆記

zynq7000 BSP無法在u-boot加載運(yùn)行怎么解決?

正點(diǎn)原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富!

zynq7000 BSP無法在u-boot加載運(yùn)行,為什么?

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

芯海通用 MCU 應(yīng)用筆記 :CS32F103 系列 MCU IAP 升級指南

CSU18MX86應(yīng)用筆記

簡談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

Xilinx ZYNQ 動手實(shí)操演練

Zynq-7000為何不是FPGA?

Zynq-7000 PS端IIC接口使用筆記

Zynq-7000 PS端IIC接口使用筆記

評論