關于risc-v啟動部分思考

1.本文說明

1.1 risc-v的誕生的時代背景

1.2 發展現狀

2.risc-v 的芯片boot過程

2.1 risc-v的啟動模式

2.2 risc-v的啟動順序

3.什么是SBI?

4.什么是opensbi

5.openSBI call接口的實現

6.總結

1.本文說明

risc-v的架構有著非常鮮明的特點,如果看過arm,aarch64,mips等架構的一些架構手冊的基礎知識,再看risc-v的芯片的架構設計,就會覺得非常有意思,可以找到一些影子,但是又比這些架構設計簡潔的多。當我看完aarch64的芯片手冊,再看risc-v的boot時,設計思想竟然可以做一些對比,同樣去看risc-v和mips的寄存器,也可看到高度的一致性。

對于x86的架構我未曾深入了解,但是在risc-v上應該也可以找到一些設計元素。總體說來,risc-v的架構設計集合了各種架構的設計的優點。我突然覺得這種堆疊即模塊的設計思想,在當前iot物聯網發展的如火如荼的時代又要被賦予最新的使命了。我十分看好risc-v的設計思想,也期待著與軟件界的Linux一樣,發展的繁榮昌盛。

1.1 risc-v的誕生的時代背景

risc-v至誕生之日起,就賦予了良好的設計模式,吸收了大量的arm、x86、以及mips中良好的設計基因,將過時指令設計的與架構設計中的坑都避免了。這幾十年的芯片的發展過程中,不少的芯片架構都曾因為設計問題消失在歷史長河中,有著曾經一度輝煌的sparc,還有當時被十分看好的mips。如今市場上最熱門的就屬x86和arm了,一個主打移動市場,一個主打pc市場,兩個在芯片架構的市場上發展的如火如荼。

然而,兩個巨頭都牢牢的把控著核心技術的門檻,用arm必須去買ip授權,以及x86的交叉授權模式等等。這些都讓很多崇尚開源的人看不下去了。那么設計芯片的指令集很難么?設計芯片的指令并非難事,這要很多人使用才行,因為芯片上需要搭載操作系統,需要去運行各種各樣的軟件,比如瀏覽器、數據庫、辦公系統、專業軟件等等。這些適配工作投入的精力和難度恐怕是需要集結各國最強的研發實力才能發展完善的。而risc-v就有這個魔力,竟然可以一呼百應,大概是大家受到arm與因特爾的壓迫已經很久了,大家都想自己造芯片玩玩。

arm與x86架構由于時間累計的問題,都積累了大量的指令集,x86當時誕生時不過80條指令,而今也有著上千條指令集了,各種復雜的指令集,多媒體指令集等等,使得寫底層軟件的人苦不堪言。喬布斯有句名言:至繁歸于至簡。歷史遺留的問題既然不能克服和解決,那就干脆抽取精華,設計出一個優秀的架構出來,于是risc-v在這種時代背景下開始了其新的使命。

1.2 發展現狀

新事物的崛起,必會引來眾多人的圍觀,技術的風所到之處,均是機會的影子。

而今risc-v已經成為眾多大學生積極學習的課程,各大公司也已經啟動了預研和探索的腳步。

RISC-V雖仍是星星之火,卻已現出燎原之態。

2.risc-v 的芯片boot過程

2.1 risc-v的啟動模式

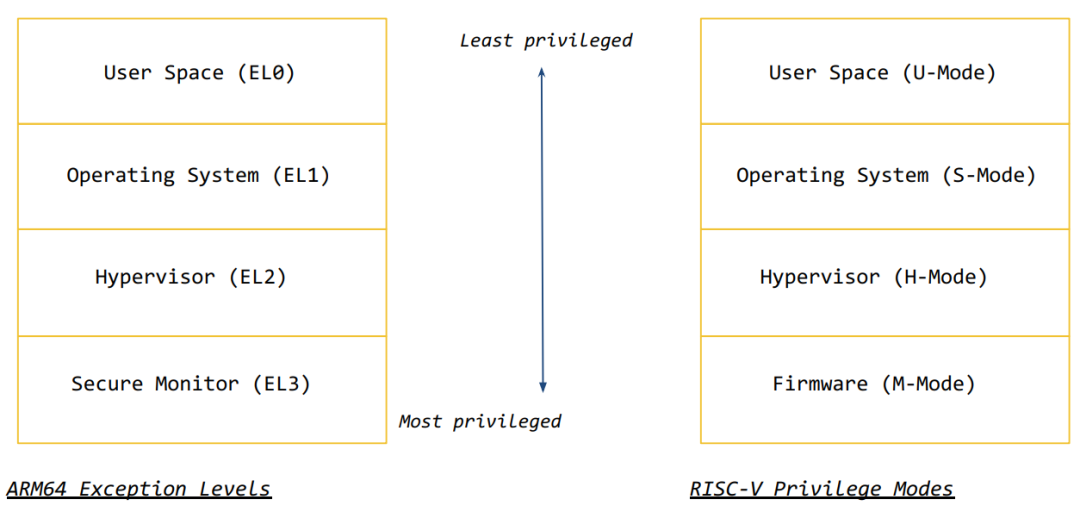

在理解risc-v的boot流程之前,首先需要知道的是risc-v設計的三種模式:

M-mode(Machine Mode)

S-mode(Supervisor Mode)

U-mode(User Mode)

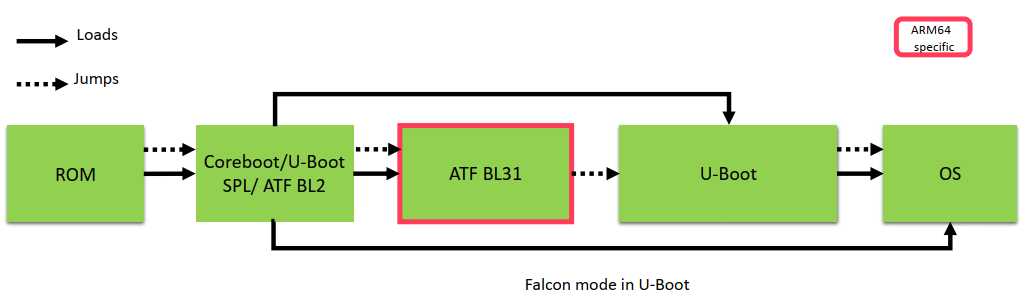

對于arm64來說,系統上電后啟動會處于EL3 secure world ,所以對于arm64來說,一般都會使用ARM Trusted firmware (TF-A) 在normal world EL2 與 secure EL3 進行切換。

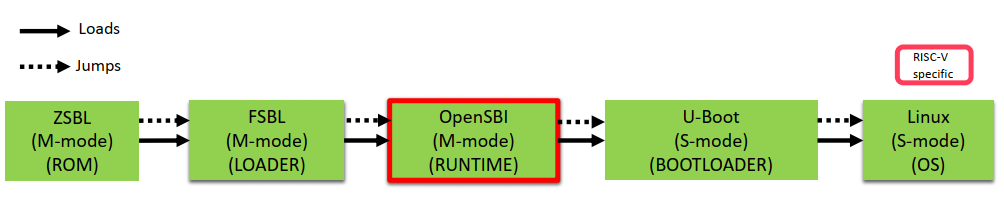

而對于risc-v來說,系統上電啟動后會在M-Mode,而risc-v目前是沒有Hypervisor這一層的概念的,所以目前采用的是opensbi。

2.2 risc-v的啟動順序

對于標準的risc-v啟動順序,可查看FU540的芯片手冊,其中有如下的順序描述:

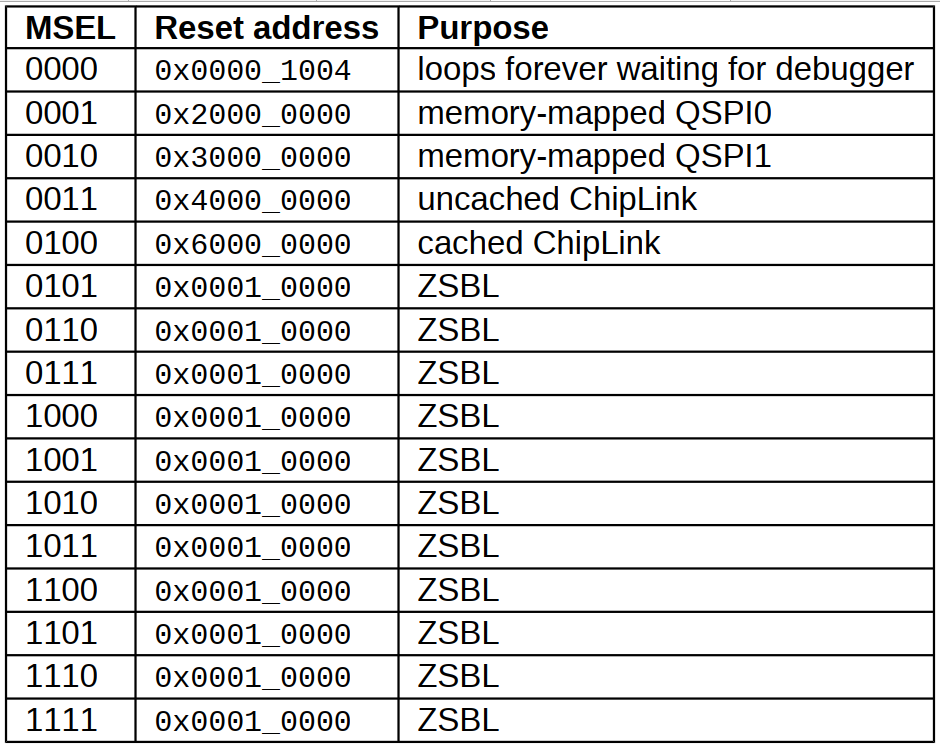

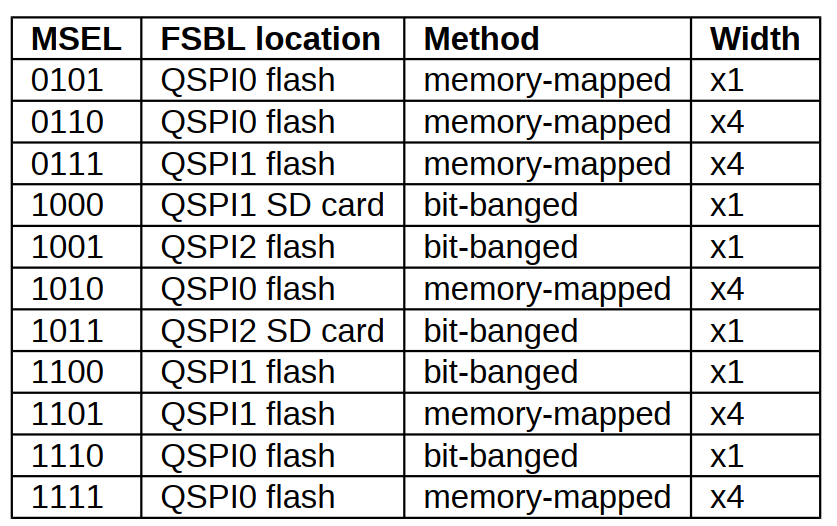

MSEL(Mode Select):啟動模式,一般為選擇撥碼開關等方式進行選擇。

ZSBL (Zeroth Stage Boot Loader):片上ROM程序。

FSBL(First Stage Boot Loader ):啟動PLLs和初始化DDR內存。

BBL(Berkeley Boot Loader ):提供加載,并且管理著二進制接口(SBI)。

下面詳細分析一下FU540的啟動流程。

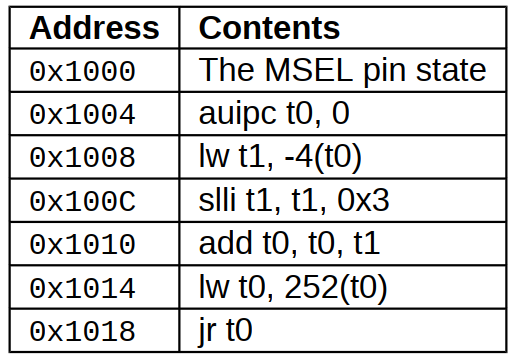

復位向量表

當芯片上電后,當芯片有33.3MHz外部晶振時鐘時,所有的核會跳轉到地址0x1004地址處去執行程序。

程序會根據MSEL選擇,選擇如下的跳轉地址:

Zeroth Stage Boot Loader (ZSBL)

零級引導程序加載會從GUID分區中下載更加復雜的FSBI,一般都是QSPI的flash或者sd卡中下載FSBI,然后將該程序放到地址0x08000000處,至于從哪個介質查找FSBI,可以看到如下的選項:

The First Stage Boot Loader (FSBL)

該執行的地址位于L2 LIM,也就是地址0x08000000。該程序的目的是DDR初始化后,將系統在DDR中執行起來。

切換頻率到1GHz。

配置ddr pll,外設時鐘和控制器等等。

拷貝設備樹和SBI固件到DDR中。

跳轉到0x80000000開始執行程序。

Berkeley Boot Loader (BBL)

Berkeley引導加載程序(BBL)從位于0x8000_0000的DDR執行。它負責提供管理器二進制接口(SBI)以及模擬所需的任何RISC-V不是由芯片本身實現的指令。該接口可以為Linux等其他的os提供調用接口。

3.什么是SBI?

SBI的全稱是RISC-V Supervisor Binary Interface 。它提供了risc-v標準的S-mode OS與SupervisorExecution Environment (SEE) 接口。

一般來說,操作系統都不會直接管理硬件資源,會通過SBI去調用到M-mode。

4.什么是opensbi

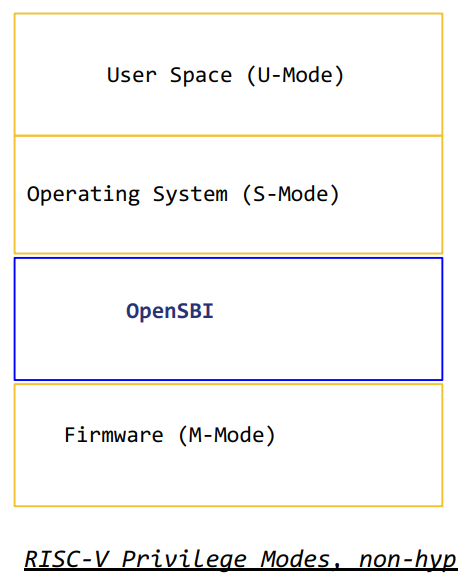

簡單的說,opensbi就是一個開源的RISC-V虛擬化二進制接口的通用的規范。

使用的是BSD-2的開源協議,也就是任何人都可以隨意修改和使用,也提供了通用的規范化的接口實現。

這里就需要理解一下為什么需要規范化了。

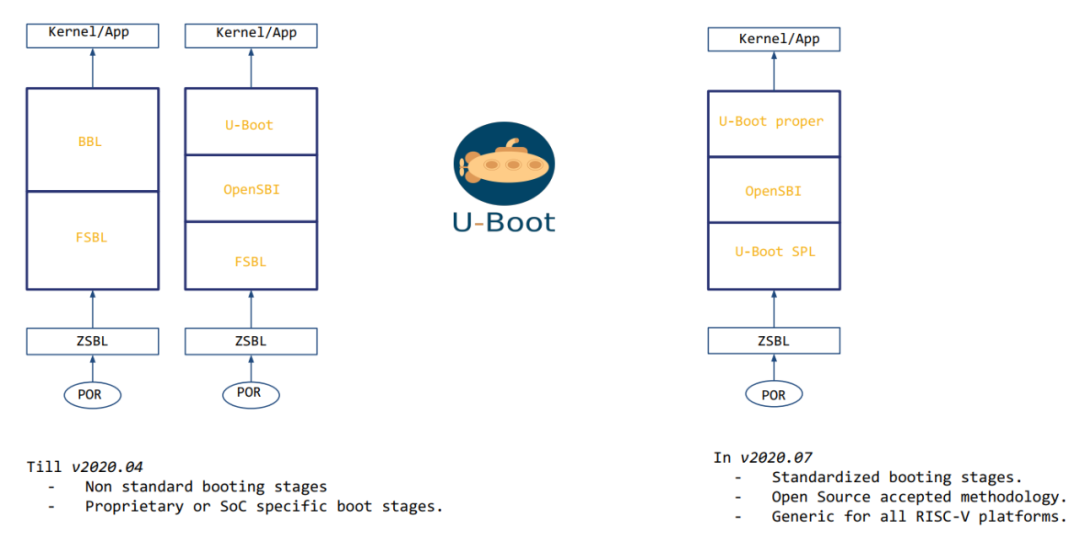

以往芯片廠家都會按照自己的啟動規則定義一些啟動的流程,比如有些需要SPL+UBOOT,有些可以是直接從SPI或SD卡中boot,這些啟動的規則很多,每當使用一款芯片,都需要去理解其啟動的流程,十分的復雜。于是就出現了一些規則和定義。

又比如Linux定義了設備規則等等:

而risc-v雖然目前芯片種類少,但是也需要制定一些啟動規則,于是有了下面的規則:

當有了opensbi后,再回頭看啟動流程,與aarch64之間進行一個對比:

aarch64借助atf框架,從EL3跳轉到EL1,并啟動u-boot。

對于riscv,上圖是一個標準的加載啟動流程,其中Opensbi提供了M模式的運行時庫。

5.openSBI call接口的實現

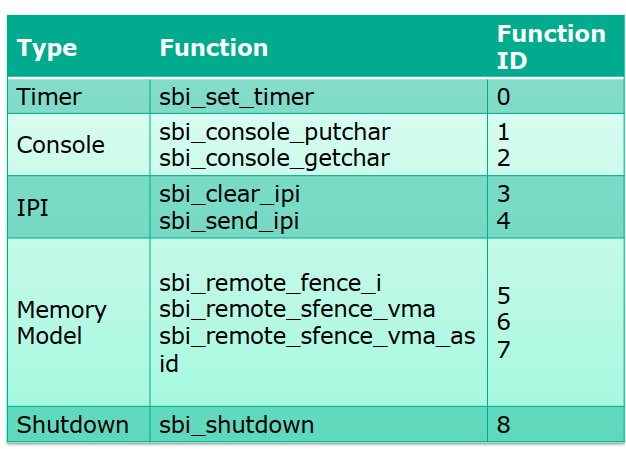

opensbi不僅僅具有加載和引導功能,也能夠供S-Mode的OS使用,比如提供串口控制臺或者中斷的分發等等。調用方式可以通過ecall來實現。類似于syscall的實現規則。當前階段實現了下面的接口:

詳細可以看下面的官方文檔描述。

https://github.com/riscv/riscv-sbi-doc/blob/master/riscv-sbi.adoc

6.總結

riscv的啟動規范可以按照opensbi的接口實現來自行定義,芯片廠家也可以通過適配opensbi的接口來實現平臺通用化的移植,這樣將會大大簡化上層設計的復雜度。同時規范化的啟動流程對于使用者來說更加的友好。相信在這種規范化的模式下,riscv的設計將會越來越完善。

責任編輯:xj

原文標題:關于risc-v啟動部分思考

文章出處:【微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

-

嵌入式

+關注

關注

5093文章

19178瀏覽量

307709 -

RISC-V

+關注

關注

45文章

2324瀏覽量

46599

原文標題:關于risc-v啟動部分思考

文章出處:【微信號:Embeded_IoT,微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于RISC-V芯片的應用學習總結

關于RISC-V學習路線圖推薦

RISC-V,即將進入應用的爆發期

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

risc-v的發展歷史

rIsc-v的缺的是什么?

RISC-V的MCU關于USB高速通信設計的難點

RISC-V有哪些優點和缺點

RISC-V有哪些優缺點?是堅持ARM方向還是投入risc-V的懷抱?

解鎖RISC-V技術力量丨曹英杰:RISC-V與大模型探索

關于risc-v啟動部分的思考

關于risc-v啟動部分的思考

評論