在電氣和電子工程中,開關是一種能夠“接合”或“斷開”電路的組件,從而中斷電流或將電流從一個導體轉到另一個導體。正如工程師們所知,開關有許多不同的類型,包括撥動開關、搖臂開關、按鈕開關、微動開關和限位開關、磁性開關和磁簧開關以及繼電器等。所有開關都有一個共同點:就是有抖動。這就是它們的工作方式。

通常情況下,這種抖動對電路幾乎沒有影響,但如果是數字電路,只要速度足夠快,就能檢測到多次抖動并對之作出響應,并因此造成嚴重后果。工程師的任務就是要避免或減輕這種抖動的影響,或者給開關“去抖動”。雖然業界長期以來一直都在采取硬件去抖動,但直到最近才轉向基于軟件的去抖動方式。然而,在某些情況下,硬件去抖動是更好的選擇。

本文解釋了什么是抖動,并討論了去抖動的軟件和硬件方法。然后用實例證明硬件去抖動是更好的選擇,并闡述如何實現該方法。最后以來自 NKK Switches、ON Semiconductor、Texas Instruments、Maxim Integrated 和 LogiSwitch 等公司的產品為例,展示了幾個具體的開關器件和硬件去抖動組件。

什么是開關抖動?

當開關或繼電器翻轉或撥動,或者每次設備改變狀態時,人們通常視之為瞬間單一反應,但實際上可能涉及 100 個以上的接合或斷開動作,這些動作持續幾千分之一秒,最后接觸才會穩定下來。

例如像 NKK 的 M2011SS1W01 這樣的單刀單擲 (SPST) 常開 (NO) 面板安裝撥動開關。假設該開關的一側(可視為輸入端)連接到地(0 伏),而另一側(在本例中為輸出端)通過上拉電阻 (R1) 連接到 5 伏電源(顯示為 +ve)(圖 1)。

觀察到開關抖動在開關啟動(閉合)和停用(打開)時都可能發生。有時抖動可能會全程跨越兩個電源軌,即不是邏輯 0 就是邏輯 1 狀態。在這種情況下,這些都是“干凈”的抖動。相比之下,如果信號只達到一個中間電壓,這些被稱為“臟”抖動。

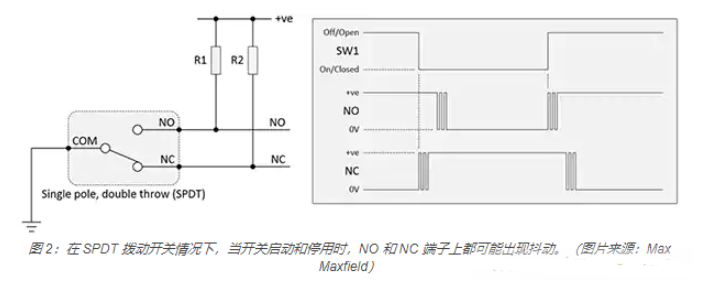

對于像 NKK 的 M2012SS1W01-BC 這樣的單刀雙擲 (SPDT) 面板安裝撥動開關,在常開 (NO) 和常閉 (NC) 端子上都可能發生抖動(圖 2)。在這種情況下,為了簡單起見,只顯示了“干凈”的抖動。

在許多情況下,這種信號抖動持續是沒有影響的。當一個開關連接到一個電子設備上時,如果這個設備的速度足夠快,可以檢測到多次抖動并做出響應,那么就會引起問題。需要做的是,在電子設備對開關發出的信號進行響應前就對其進行去抖動。

軟件與硬件去抖動比較

在 20 世紀 60 年代和 70 年代,開關去抖動采用了各種硬件技術,從與 SPST 開關一起使用的簡單電阻電容 (RC) 延遲電路到更復雜的置位/復位 (SR) 鎖存器功能。

最近,由于許多系統都采用了微處理器單元 (MPU) 或微控制器單元 (MCU),因此使用軟件技術來消除來自任何開關的信號已經變得很普遍。然而,軟件去抖動并不總是最好的方法。有一些采用小型、低性能、存儲空間有限的處理器的應用,其代碼空間和/或時鐘周期有限,就無法實現去抖動例程。在這些情況下,硬件實現可能是一個更好的解決方案。

另外,很多軟件開發人員對開關的物理特性并不熟悉,比如開關的去抖動特性除了在不同的激活方式下會有不同的變化外,還可能受到溫度、濕度等環境條件的影響。

軟件開發人員缺乏開關專業技術,加上現有關于開關抖動的文獻往往是混亂和矛盾的,進一步加劇了這一問題的嚴重性。例如,我們通常讀到開關在激活或停用后 1 毫秒 (ms) 就會停止抖動。然而,知名嵌入式系統專家 Jack Ganssle 對各種類型的開關進行了實證測試,將每個開關激活 300 次,并記錄下了觸點打開和關閉的最小和最大抖動量。據其報告記錄,平均抖動持續時間為 1.6 ms,最大抖動持續時間為 6.2 ms。一些工業和軍事“最佳實踐”建議在初始激活后等待 20 ms,然后再假設開關已經停止抖動;另一些人則主張在最終檢測到抖動后等待 20 毫秒再觸發任何動作。

此外,還有很多簡單的無處理器的系統也需要消除開關抖動。舉幾個這類系統的例子:驅動七段式顯示器對來自繼電器的脈沖進行計數的二進制計數器;用作門或閘電機控制裝置的555 單次定時器的觸發輸入;以及采用鍵控輸入的基于寄存器的有限狀態機 (FSM)。還有電子微調電位器 (Pot),其值是用開關輸入(加、減,有時是存儲)修改的,這時開關抖動就會有問題。

所有這些例子都清楚地表明,掌握一些如何進行硬件去抖動的知識對任何設計人員或開發人員都是有用的。

用 RC 網絡對 SPST 開關進行硬件去抖動

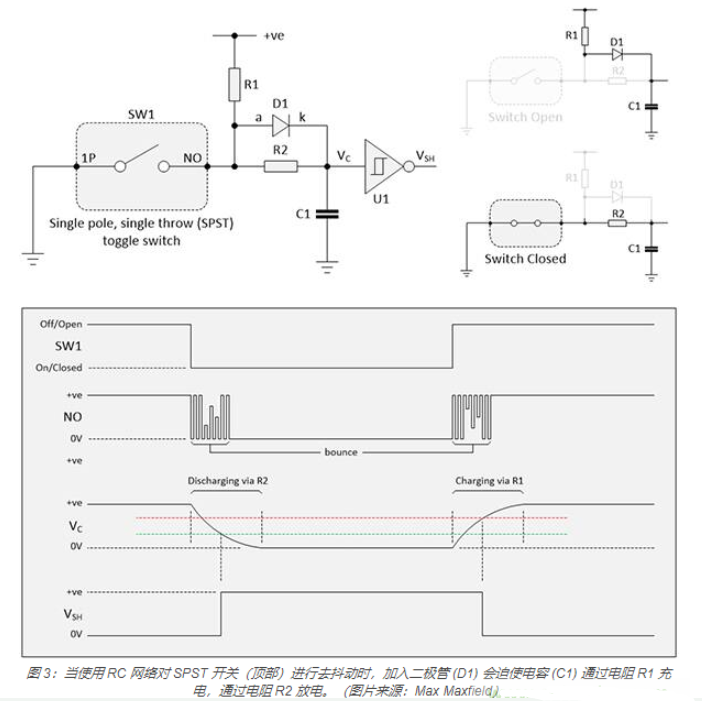

一個最簡單的基于硬件的開關去抖動方案就是將電阻電容 (RC) 網絡與 SPST 開關結合起來使用。這種電路有很多變型。其中一個較通用的實現方案是采用兩個電阻和一個二極管(圖 3)。

當開關啟動(閉合)時,電容 C1 通過電阻 R2 放電。如果這個電路中省略了二極管 D1,那么當開關停用(打開)時,C1 將通過電阻 (R1 + R2) 充電。但是,D1 的存在意味著 C1 只能通過 R1 充電。

在某些情況下,人們只關注開關的激活(即觸發動作發生),在這種情況下,D1 可以省略。但是,如果要在開關被激活和停用時觸發動作,并且要考慮將延遲降到最低,建議增加 D1。

觀察電容器電壓 VC 所表現出的指數充放電曲線。將此信號直接送入下游數字邏輯功能的輸入端并不是一個好主意,因為下游數字邏輯功能不會喜歡看到一個在“好”的邏輯 0 和邏輯 1 值之間的未定義區域徘徊的信號。相反,該信號應被送入帶有施密特觸發器輸入的緩沖器的輸入端。此外,通常要使用反相緩沖器,如 Texas Instruments 的 CD74HC14M96 的一個通道,因為反相功能的切換速度比非反相功能快。

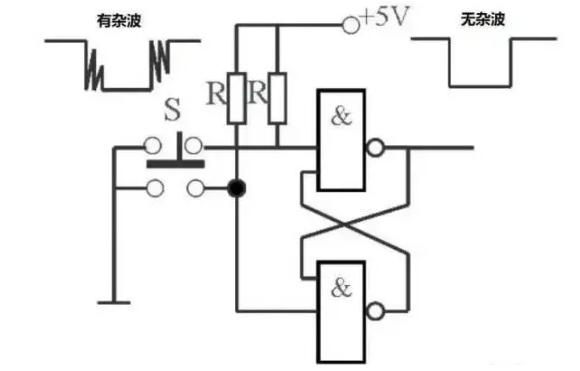

用 SR 鎖存器對 SPDT 開關進行去抖動

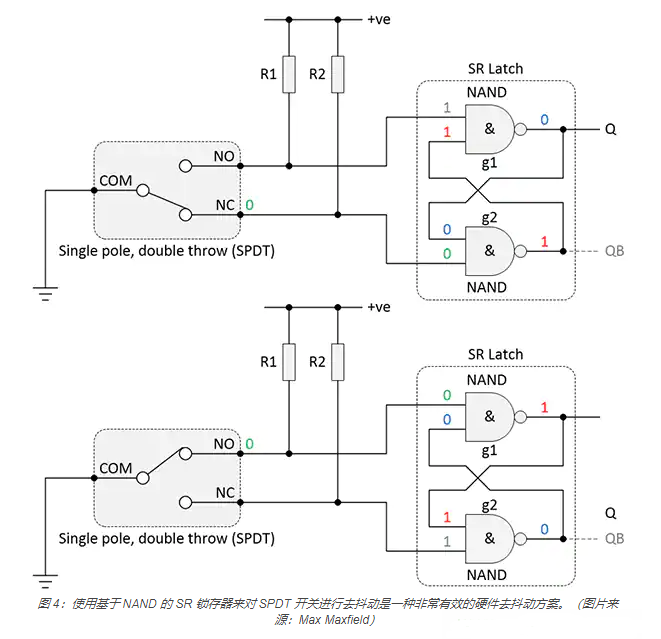

在 SPDT 開關情況下,常見的硬件去抖動方案是采用 SR 鎖存器。自從 20 世紀 60 年代 IBM 等公司將這種技術應用于大型計算機的開關面板后,這種方法就被認為是簡單硬件去抖動解決方案中的精華。這種鎖存器可以使用兩個背對背的雙輸入 NAND 門形成;例如,采用 Texas Instruments 的 SN74HC00DR 四路雙輸入 NAND IC 的兩個通道(圖 4)。

當開關的 NC 端子接地時,如圖 4 上半部分所示,這將迫使門 g2 的輸出變為邏輯 1。反過來,門 g1 輸入端的兩個邏輯 1 又迫使其輸出端變為邏輯 0。相比之下,當開關的 NO 端子接地時,如圖 4 下半部分所示,這就迫使門 g1 的輸出變為邏輯 1。反過來,門 g2 輸入端的兩個邏輯 1 又迫使其輸出端變為邏輯 0。

這個電路之所以工作得這么好,是因為當它的兩個輸入都處于不活動的邏輯 1 狀態時,SR 鎖存器會記住它以前的值。請記住,如圖 2 所示,當一個 SPDT 開關被撥動時,在該時刻,無論其哪一個端子接地,都會發生抖動。由于這些抖動信號在其原值(邏輯 0)和新值(邏輯 1)之間,所以對 SR 鎖存器的當前狀態沒有影響。只有在這個端子停止抖動后,其相對的端子才開始抖動,此時 SR 鎖存器才會改變其狀態。

用專用設備對 SPST 開關進行去抖動

前面的解決方案有一個問題,就是很多設計者喜歡使用 SPST 開關,因為它們的成本普遍低于 SPDT。市場上有很多有名的專用 SPST 去抖動器件,如 ON Semiconductor 的 MC14490DWG 和 Maxim Integrated 的 MAX6818EAP+T。

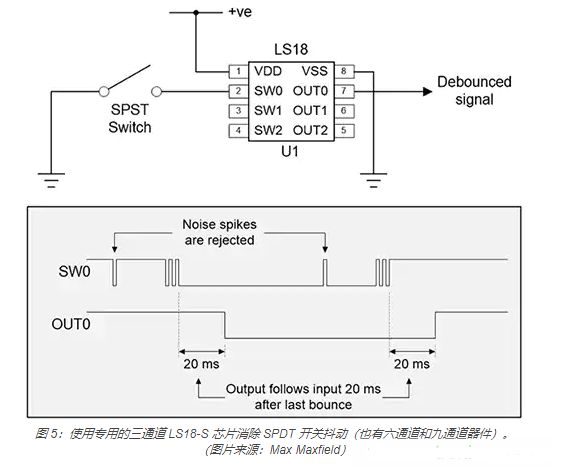

另一家制造商 LogiSwitch 也提供了一套三通道、六通道和九通道的去抖動解決方案,同時采用通孔和表面貼裝 (SMD) 封裝。例如,考慮使用 LogiSwitch LS18-S 器件的電路(圖 5)。

與 LogiSwitch 產品家族所有成員一樣,LS18-S 支持 2.5 至 5.5 伏的工作電壓范圍(供電電壓值不影響器件的響應時間)。此外,與其他一些專用 IC 解決方案不同,LogiSwitch 去抖動器件不需要任何額外的元件,如外部時鐘、RC 時序網絡或輸入或輸出上的上拉電阻。

LS18-S 采用 LogiSwitch 專有的自適應 NoBounce(無抖動)技術,實現了高水平抗噪能力。在啟動或終止一個周期時禁止小于 20 ms 持續時間的噪聲尖峰,然后在開關激活和釋放的最后一次抖動后,無論抖動持續時間長短,輸出都會延遲 20 毫秒。

結語

開關有很多不同的類型,包括撥動開關、搖臂開關和按鈕開關,這些開關都可能會抖動。如果開關抖動不得到緩解,就會導致微處理器和其他電子電路將一次開關激活視為多個事件。

人們常常利用微控制器中運行的軟件對開關發出的抖動信號進行消抖。如上所述,雖然這是一種低成本的解決方案,但它可能并不是所有情況下的最佳選擇。這些情況包括:系統基于性能和存儲空間有限的微控制器,軟件開發人員缺乏開關相關問題專業知識,或者系統實現沒有微控制器。

作為替代選擇,我們可以使用各種方法在硬件中進行去抖動,具體方法包括電阻電容網絡、SR 鎖存器以及專用集成電路。

(來源:Digi-Key,作者:Clive "Max" Maxfield)

編輯:hfy

-

微控制器

+關注

關注

48文章

7651瀏覽量

152116 -

繼電器

+關注

關注

132文章

5361瀏覽量

149565 -

鎖存器

+關注

關注

8文章

908瀏覽量

41645 -

Digi-Key

+關注

關注

4文章

135瀏覽量

52714

發布評論請先 登錄

相關推薦

RAID 5 硬件與軟件 RAID 的區別

如何實現軟件的emulate功能 emulation和虛擬化的區別是什么

raid 硬件與軟件的區別

SRC4392怎么實現硬件控制?

抖動定義和測量

兩種常見的硬件消抖實現方式

CDR電路設計與抖動管理

抖動的概念和類型 量化時域抖動、隨機抖動和頻域抖動的方法

如何實現軟件與硬件的開關抖動設計

如何實現軟件與硬件的開關抖動設計

評論