在計算世界中,不可思議的事情之一是在數(shù)據(jù)中心中迅速采用人工智能(AI)和云計算。這些和其他因素正在推動異構(gòu)計算-使用CPU,GPU,FPGA,ASIC加速器,網(wǎng)絡(luò)接口控制器(NIC)和其他處理元件,所有這些元件都連接到越來越大的內(nèi)存池。

但是,高性能計算(HPC)需要更新以有效連接這些處理元素并共享日益昂貴的內(nèi)存的能力。參加旨在應(yīng)對異構(gòu)計算帶來的挑戰(zhàn)的Compute Express Link(CXL)計劃。它旨在提供高速緩存一致性以及在沒有不必要的成本的情況下添加新的內(nèi)存層的能力。

CXL聯(lián)盟吸引了廣泛的支持,有近100個成員公司和14個公司的董事會,其中包括幾乎所有主要供應(yīng)商,包括AMD,Arm,IBM,Intel和Xilinx。

就像Intel發(fā)起USB,PCI和PCI Express一樣,當(dāng)Intel向最初由9家公司組成的工作組貢獻(xiàn)了該技術(shù)的第一個迭代時,CXL聯(lián)盟便開始起步。2019年9月,成立了董事會,擁有96家成員公司。

在致力于成為正式成員之前,任何公司都可以訪問CXL網(wǎng)站,免費獲得點擊許可,并下載該規(guī)范當(dāng)前版本的評估版。參與人員能夠指導(dǎo)工作的進(jìn)展,工程師現(xiàn)在可以在開發(fā)階段接受有關(guān)2.0規(guī)范的培訓(xùn)課程。

CXL建立在PCIe互連標(biāo)準(zhǔn)的基礎(chǔ)上,CXL 2.0(將于2020年12月推出)將補充PCIe 5.0標(biāo)準(zhǔn)的使用,其每通道32 Gbps的信號速度,預(yù)計將在2021年發(fā)布。隨后的PCIe 6.0規(guī)格有望提高一倍。具有三個協(xié)議套件的CXL利用PCIe內(nèi)具有備用協(xié)議的功能。

第一個CXL.io取代了PCIe并處理標(biāo)準(zhǔn)設(shè)置功能。將CXL卡插入PCIe插槽后,CXL.io會識別出正在使用CXL,然后關(guān)閉PCIe并啟動CXL.io協(xié)議。它允許系統(tǒng)使用同一組電線和標(biāo)準(zhǔn)PCIe插槽,并根據(jù)需要混合CXL和PCIe資源,這是節(jié)省資源和系統(tǒng)成本的重要手段。

第二個和第三個協(xié)議CXL.cache和CXL.memory支持維護(hù)緩存一致性,減少延遲以及使用新的內(nèi)存類型的能力,以及其他優(yōu)勢。

圖1CXL事務(wù)層在單個鏈路上包含三個動態(tài)多路復(fù)用子協(xié)議。資料來源:英特爾

從許多方面來看,CXL都是關(guān)于驅(qū)動異構(gòu)計算的,異構(gòu)計算正是其中的許多創(chuàng)新之源。在當(dāng)今的異構(gòu)計算世界中,內(nèi)存連接到CPU,其他存儲庫連接到加速器設(shè)備:GPU,自定義邏輯,F(xiàn)PGA,NIC等。這些內(nèi)存池位于兩個不同的域中,不同類別的設(shè)備通過不同的機(jī)制與內(nèi)存通信。保持高速緩存一致性是一項挑戰(zhàn)。

連接CPU和連接加速器的內(nèi)存池具有PCI對等訪問。借助CXL及其以內(nèi)存為中心的體系結(jié)構(gòu),它可以將內(nèi)存體系結(jié)構(gòu)和內(nèi)存語義引入到傳統(tǒng)上在I / O總線上的功能。

使用PCIe的替代協(xié)議

CXL利用PCIe中的替代協(xié)議選項。當(dāng)我們使用CXL時,PCIe會關(guān)閉,CXL會接管工作,并為我們提供內(nèi)存類的延遲,而不是I / O類的延遲。

在數(shù)據(jù)中心中,CXL主要在互連體系結(jié)構(gòu)的節(jié)點級層上運行,以實現(xiàn)芯片到芯片的互連。對于機(jī)架和行級別,開放系統(tǒng)Gen-Z互連可以通過直接連接,交換或結(jié)構(gòu)拓?fù)涮峁?shù)據(jù)和設(shè)備的存儲器語義訪問。

CXL和Gen-Z非常互補,前者用于節(jié)點,后者用于節(jié)點之外。從CXL的角度來看,Gen-Z可以幫助我們變得更加流暢,當(dāng)同時部署兩者時,我們將看到很多協(xié)同作用。實際上,我們認(rèn)為互補性將隨著時間的流逝而發(fā)展。

CXL與Gen-Z有著很好的關(guān)系,包括正式協(xié)議。目的是使Gen-Z非常有效地連接到CXL。如果工程師希望結(jié)構(gòu)能夠可靠地工作,則任何結(jié)構(gòu)都需要與CPU保持一致的接口。因此,讓Gen-Z在CXL上方的機(jī)架級和行級進(jìn)行更多操作是很有意義的。

非對稱復(fù)雜性是關(guān)鍵

CXL中的一項功能是能夠非對稱地“偏置”系統(tǒng)中的計算資源。為了保持高速緩存一致性,操作通常會保持“ CPU偏差”,因為這是確保高速緩存一致性最經(jīng)常發(fā)生的地方,是在CPU的“本地代理”處。加速器大多數(shù)時候都使用特定類別的數(shù)據(jù),它們將使用稍微更簡單的“設(shè)備偏差”。

通過這種非對稱方法,CXL提供了緩存一致性的好處,而不會陷入CPU上本地代理的復(fù)雜性中。總而言之,非對稱復(fù)雜性是CXL的關(guān)鍵功能,它減輕了緩存一致性接口設(shè)計的負(fù)擔(dān)。

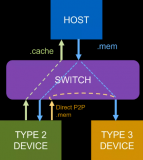

圖2CXL中的非對稱復(fù)雜性減輕了緩存一致性接口設(shè)計的負(fù)擔(dān)。資料來源:英特爾

降低CXL的復(fù)雜性將使來自不同供應(yīng)商的處理器能夠輕松建立一致的緩存,這在業(yè)界尚屬首次。CXL的一項關(guān)鍵價值主張是,利用CPU中的復(fù)雜性而不是在加速器中復(fù)制復(fù)雜性來分解復(fù)雜性的概念。

在CXL中,我們從CPU開始,向北和向南都有可緩存的內(nèi)存,既有它自己的內(nèi)存,也有加速器內(nèi)存。加速器也具有完全相同的功能。可以訪問CPU內(nèi)存的PCI設(shè)備現(xiàn)在可以訪問CXL下的加速器內(nèi)存。我們對內(nèi)存的兩個部分都具有這種對稱能力。這兩個池將成為兩臺機(jī)器均可訪問的一致性內(nèi)存池的一部分。

負(fù)擔(dān)得起地增加存儲容量

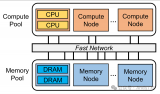

數(shù)據(jù)中心系統(tǒng)不可避免地需要增加存儲容量和帶寬。一種解決方案是在DRAM和固態(tài)驅(qū)動器(SSD)之間添加一類持久性存儲器,在許多情況下,它們足以存儲整個數(shù)據(jù)庫。這種單獨的存儲層(比DRAM便宜)可以用于各種存儲創(chuàng)新中。

CXL定義了三種類型的設(shè)備:類型1包括具有自己的緩存但沒有附加內(nèi)存的加速器。類型2類的設(shè)備包括已附加內(nèi)存的加速器。在這兩種情況下,都可以保證高速緩存的一致性。

第三類設(shè)備包括支持內(nèi)存緩沖區(qū)和內(nèi)存擴(kuò)展設(shè)備的控制器。系統(tǒng)可以添加更多的DRAM和/或持久性內(nèi)存,但將其移出DDR接口。從邏輯上講,出現(xiàn)的內(nèi)存緩沖區(qū)與其在主內(nèi)存總線上的內(nèi)存緩沖區(qū)沒有什么不同。

啟用分類內(nèi)存

CXL是一種高速互連,并且該聯(lián)盟已致力于顯著減少等待時間,以實現(xiàn)分類內(nèi)存。用高效,低延遲的訪問機(jī)制創(chuàng)建共享內(nèi)存池與聯(lián)盟實現(xiàn)異構(gòu)資源共享的總體目標(biāo)是一致的。

CXL中對Type 3設(shè)備的支持為分離內(nèi)存控制器提供了機(jī)會。隨著數(shù)據(jù)中心處理各種用例,第3類設(shè)備可以更輕松地提供對持久性介質(zhì)或尚未投入生產(chǎn)的新內(nèi)存類型的訪問。

事實證明,僅僅增加更多的直接連接DRAM太昂貴了。不僅DRAM成本的增長步伐很慢,而且PCB上更多路由層和控制器上更多引腳的復(fù)雜性也很昂貴。

與其增加板上的內(nèi)存,不如增加CXL鏈路的數(shù)量是一種更簡單的方法,它不依賴于并行高速總線。并行DDR接口需要200個以上的引腳,而CXL可以使每個封裝的引腳數(shù)更少,并減少PCB層數(shù)。使用CXL串行接口,可以在更理想的位置存儲更長的內(nèi)存,從而改變了存儲設(shè)備上的氣流。

供應(yīng)商可以使用特定于媒體的控制器來構(gòu)建CXL內(nèi)存擴(kuò)展器設(shè)備。一個系統(tǒng)可以支持多種不同的存儲器類型,包括DDR3,DDR4或DDR5,以及持久性存儲器,低功耗DRAM等,每種類型都具有特定于媒體的控制器,該控制器支持非對稱或不確定的定時和錯誤處理。較慢的內(nèi)存層可以與主層完全隔離,而對直接連接的DRAM雙列直插式內(nèi)存模塊(DIMM)的干擾最小。

圖3代表性的CXL用法簡化了編程模型并提高了性能。資料來源:英特爾

使用CXL,開發(fā)人員可以撥入最適合其應(yīng)用程序的內(nèi)存帶寬,使用持久性內(nèi)存選項,并根據(jù)應(yīng)用程序的需要進(jìn)行混合匹配。該聯(lián)盟的目標(biāo)是召集許多不同的行業(yè)參與者,以確保一個健壯的,不斷發(fā)展的生態(tài)系統(tǒng)。我們確實需要通過互操作性來進(jìn)行工作,但是盡管我們在PCIe方面擁有良好的記錄,但是我們還需要通過電源,機(jī)械和管理接口來構(gòu)建健壯的CXL生態(tài)系統(tǒng)。

Jeff Hockert是英特爾技術(shù)領(lǐng)導(dǎo)力營銷團(tuán)隊的高級營銷經(jīng)理。

編輯:hfy

-

控制器

+關(guān)注

關(guān)注

112文章

16445瀏覽量

179438 -

PCIe

+關(guān)注

關(guān)注

15文章

1260瀏覽量

83185 -

異構(gòu)計算

+關(guān)注

關(guān)注

2文章

102瀏覽量

16338

發(fā)布評論請先 登錄

相關(guān)推薦

內(nèi)存擴(kuò)展CXL加速發(fā)展,繁榮AI存儲

SMART Modular世邁科技CXL內(nèi)存擴(kuò)充卡獲CXL聯(lián)盟認(rèn)證

瀾起科技CXL?內(nèi)存擴(kuò)展控制器芯片通過CXL 2.0合規(guī)性測試

異構(gòu)計算的概念、核心、優(yōu)勢、挑戰(zhàn)及考慮因素

【一文看懂】什么是異構(gòu)計算?

淺談國產(chǎn)異構(gòu)雙核RISC-V+FPGA處理器AG32VF407的優(yōu)勢和應(yīng)用場景

三星電子計劃2024年下半年推出CXL存儲

打造異構(gòu)計算新標(biāo)桿!國數(shù)集聯(lián)發(fā)布首款CXL混合資源池參考設(shè)計

新思科技CXL 3.1驗證解決方案

AvaotaA1全志T527開發(fā)板AMP異構(gòu)計算簡介

異構(gòu)計算:解鎖算力潛能的新途徑

SMART Modular 世邁科技推出高性能服務(wù)器專用全新CXL? 內(nèi)存擴(kuò)充卡系列

業(yè)界首創(chuàng)512GB CXL AIC內(nèi)存擴(kuò)展卡,江波龍革新AI與高性能計算領(lǐng)域內(nèi)存技術(shù)

高通NPU和異構(gòu)計算提升生成式AI性能?

利用CXL技術(shù)重構(gòu)基于RDMA的內(nèi)存解耦合

采用CXL計劃應(yīng)對異構(gòu)計算中的內(nèi)存解決方案

采用CXL計劃應(yīng)對異構(gòu)計算中的內(nèi)存解決方案

評論