讓我們來看看等長對我們信號質量的影響。

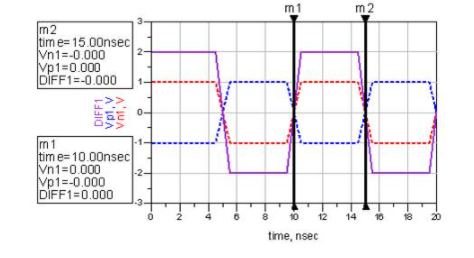

眾所周知,SERDES信號都是由差分傳輸的,也就是說,兩根信號線同時傳輸兩個大小相等,方向相反的信號,接收端接收到的信號由兩線相減得來。當兩根線完全等長的時候,我們看到的波形應該是這樣子的:

兩次經過零軸的時間差為5ns,剛好是信號的一個UI。

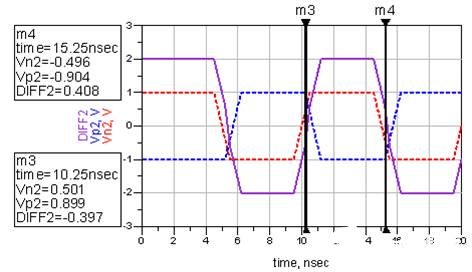

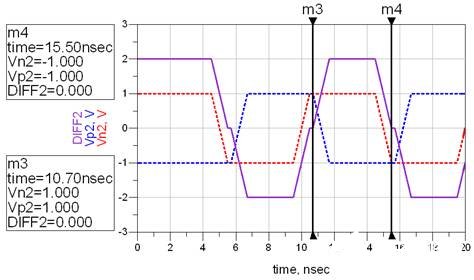

當兩線不等長的時候,我們看到的波形是這個樣子的:

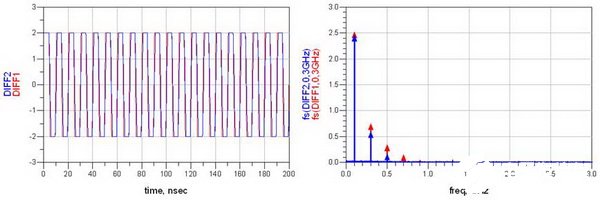

上升沿明顯變緩有木有。再將兩個對比看看:

圖中,藍色的是N與P不等長的信號,可以看到,當兩線不等長的時候,差分信號的能量明顯變弱了,那多的能量去哪里了呢?

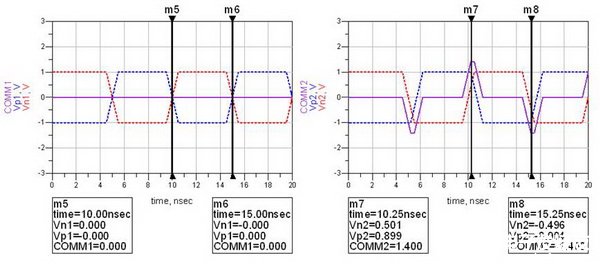

差分對之中除了差模能量之外還有共模能量,差模是N與P之間相減,共模是N與P之間相加。能量總是守恒的,多的能量變成了共模能量繼續存在,圖片:

如果兩線的長度相差再大一些,我們接收端接收到的信號將會變成這樣:

可以看到,兩次經過零軸的時間由之前的5ns變成了4.8ns。或者說,N與P的長度差,引起了0.04UI的抖動。這時候,串行的Clock recovery該花點心思才能將其時鐘解出來了。而且在進行時鐘與數據對位的時候,是對在0V這個階梯的左邊還是對在右邊呢?這又會引起時序問題的出現。

編輯:hfy

-

波形

+關注

關注

3文章

379瀏覽量

31660 -

SerDes

+關注

關注

6文章

201瀏覽量

35048 -

等長

+關注

關注

0文章

4瀏覽量

7564

發布評論請先 登錄

相關推薦

一個等時不等長的DDR

Altium Designer如何繞等長線

用allegro使二條時鐘線等長的設計置

一種頻率估計的倍頻等長信號加權融合算法

Allegro中關于繞等長的自動功能

三個步驟,PCB設計信號等長分析

PCB設計中繞等長線的方法和技巧

等長對我們信號質量有什么影響?

等長對我們信號質量有什么影響?

評論