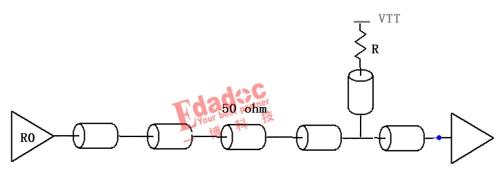

有木有發(fā)現(xiàn)匹配最好的串聯(lián)端接電阻的阻值不是50ohm,而是30ohm,如下圖。這是為什么呢?

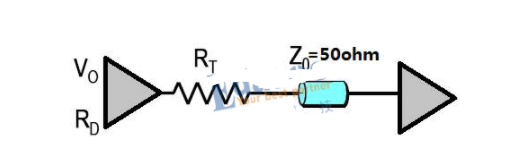

對(duì)高速數(shù)字電路設(shè)計(jì)有一定了解的人就知道,其實(shí)驅(qū)動(dòng)器本身有內(nèi)阻,做串聯(lián)端接匹配時(shí),串聯(lián)電阻的阻值和驅(qū)動(dòng)內(nèi)阻加起來(lái)大致等于傳輸線阻抗就可以了,即R_(D )+R_T≈Z_0 。

這個(gè)時(shí)候,有童鞋可能就要跳起來(lái)了,MR‘S,你說(shuō)的倒是容易,我也知道驅(qū)動(dòng)內(nèi)阻RD 加串聯(lián)電阻等于傳輸線阻抗這個(gè)公式,大家都知道,so easy啊,問(wèn)題在于,傳輸線阻抗可以很輕松的在datasheet找到,可是驅(qū)動(dòng)器內(nèi)阻上哪兒去找, datasheet上又沒(méi)有?

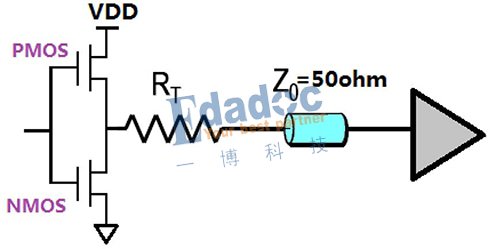

下圖是一個(gè)簡(jiǎn)單的驅(qū)動(dòng)電路。

當(dāng)驅(qū)動(dòng)器持續(xù)輸出高電平時(shí),PMOS管導(dǎo)通,NMOS關(guān)閉,電流流經(jīng)PMOS輸出,這個(gè)時(shí)候電流感受到的驅(qū)動(dòng)內(nèi)阻RD是PMOS管的導(dǎo)通電阻RP;反之,當(dāng)電流持續(xù)輸出低電平時(shí),電流感受到的驅(qū)動(dòng)內(nèi)阻RD就是NMOS管的導(dǎo)通電阻RN 。一般情況下,PMOS管的導(dǎo)通電阻RP 比NMOS管的導(dǎo)通電阻RN 要大,這是它們的工藝所決定的,從上一篇(2)中,我們可以知道,輸出高電平時(shí),其RC時(shí)間常數(shù)會(huì)大,上升沿更緩。有時(shí)候,我們看到信號(hào)的上升沿比下降沿要更緩一些,就是這個(gè)原因啦。

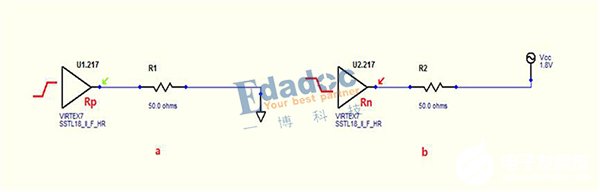

下面,我們來(lái)看一下怎樣得到驅(qū)動(dòng)內(nèi)阻的阻值?先使用仿真工具搭建兩個(gè)簡(jiǎn)單的電路,如下:

以Xilinx V7芯片DDR2驅(qū)動(dòng)為例,在圖a的驅(qū)動(dòng)端中加入上升沿驅(qū)動(dòng)(PMOS導(dǎo)通),通過(guò)50ohm電阻下拉到地,通過(guò)電阻分壓的原理,即V_meas=50/(50+R_P )×V_CC,可以求的RP的值。

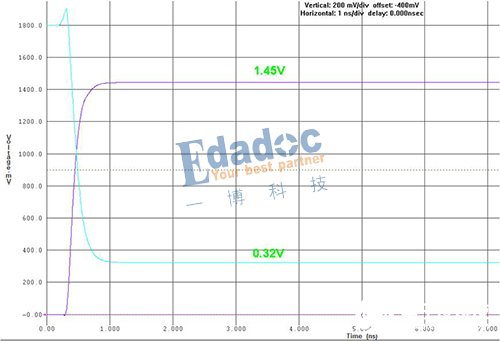

在圖b中驅(qū)動(dòng)端加入下降沿驅(qū)動(dòng)(NMOS導(dǎo)通),通過(guò)50ohm電阻上拉到VCC,通過(guò)電阻分壓的原理,即V_meas=R_N/(50+R_N )×V_CC,可以求得RN的值。下圖是仿真得到的波形:

通過(guò)計(jì)算可以得到,RP=12.1 ohm,RN=10.8 ohm,兩個(gè)阻抗值相差不大,選取任何一個(gè)值來(lái)計(jì)算端接電阻,都可以。通過(guò)這樣簡(jiǎn)單的仿真,我們就可以獲得驅(qū)動(dòng)器的驅(qū)動(dòng)內(nèi)阻啦。

有時(shí)候,我們還會(huì)遇到這兩個(gè)值差別比較大的情況,比如RP=20ohm,RN=10ohm,那這個(gè)時(shí)候我們要怎么選擇呢?如果選擇RP來(lái)計(jì)算匹配電阻,則匹配電阻RT=30 ohm,高電平匹配很好,低電平時(shí),匹配電阻就偏小,信號(hào)傳輸?shù)絺鬏斁€端時(shí)會(huì)出現(xiàn)正反射,過(guò)沖較大;如果選擇RN來(lái)計(jì)算匹配電阻,則RT=40ohm,低電平匹配很好,高電平時(shí),匹配電阻就偏大,信號(hào)傳輸?shù)絺鬏斁€時(shí)出現(xiàn)負(fù)反射,上升沿會(huì)出現(xiàn)臺(tái)階,另外,上升沿還有因?yàn)镽T的增大而變緩。所以,這兩種選擇有利有弊,遇到這種情況時(shí),就需要設(shè)計(jì)者酌(zi)情(qiu)考(duo)量(fu)啦。

編輯:hfy

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

53文章

8271瀏覽量

147061 -

傳輸線

+關(guān)注

關(guān)注

0文章

377瀏覽量

24130 -

PMOS

+關(guān)注

關(guān)注

4文章

246瀏覽量

29709 -

匹配電阻

+關(guān)注

關(guān)注

0文章

20瀏覽量

11518

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

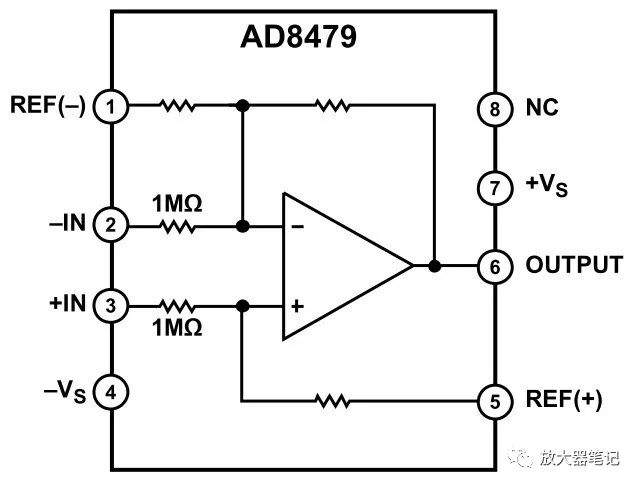

AD8479內(nèi)部電阻的阻值如何確定

為什么串阻阻值通常是22到33歐姆,看完后不信你不懂!

如何確定排阻引腳

探究電阻布局對(duì)端接效果的影響

射頻功率衰減器電阻值的確定

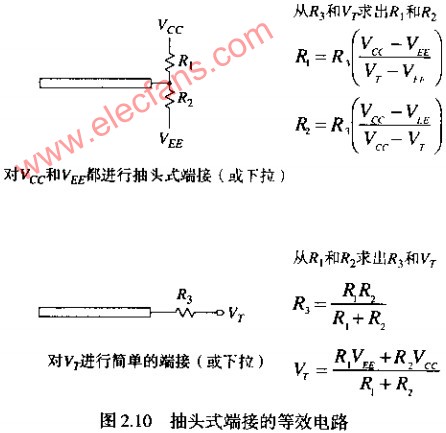

抽頭式下拉端接

端接方式對(duì)改善高速電路串擾的分析研究

端接串阻的阻值如何確定

端接串阻的阻值如何確定

評(píng)論