該應用筆記介紹了測量和最大化 120 dB、24 位和 96 kHz 模數轉換器集成電路性能的技術。它介紹了 ADC 架構、輸入緩沖器設計及其噪聲要求、噪聲計算和噪聲分析。它還描述了外部支持電路設計和一些示例結果。

A/D 轉換器架構

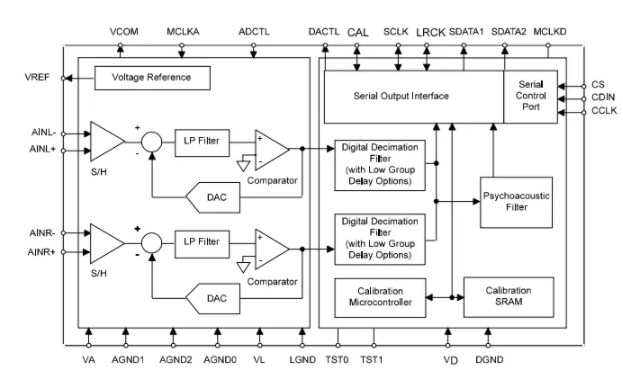

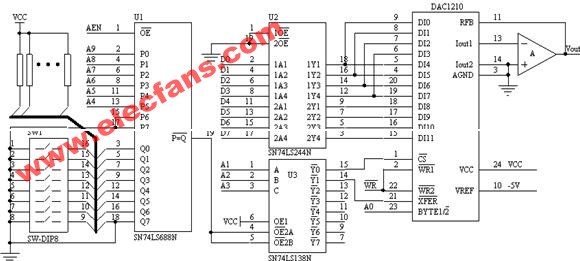

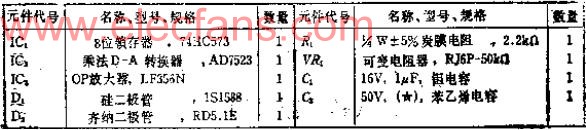

本次討論中使用的 A/D 轉換器由一個模擬 delta sigma 調制器芯片和一個數字濾波器芯片組成,封裝在單個 28 引腳 SOIC 塑料封裝中。圖 1 顯示了該設備的框圖。delta-sigma 調制器設計的亮點包括使用三電平調制器,校準后可產生出色的線性度,調制器輸出數據的新穎編碼方案,可消除數據信號邊沿數量和極性的數據相關變化,以及全差分設計,產生低失真和良好的共模抑制。抽取濾波器包括多個字長輸出選項,以及可選的心理聲學噪聲整形。還包括實時使用的低群延遲。

A/D 轉換器框圖

輸入緩沖器設計

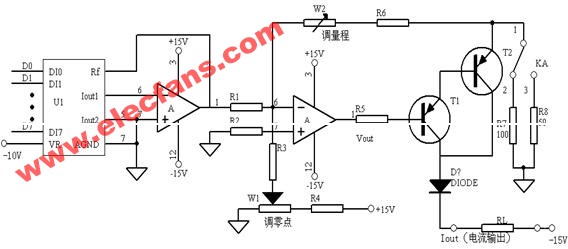

A/D 轉換器的輸入緩沖電路必須滿足幾個嚴格的要求。這些包括:可忽略的噪聲貢獻、DC 電平從通常以零伏為中心的輸入信號轉移到以 A/D 轉換器的共模電壓為中心的輸出信號、將緩沖放大器與開關電容器電流瞬變隔離,同時保持低輸出阻抗,以免引起失真,并提供適合調制器采樣率的抗混疊濾波。

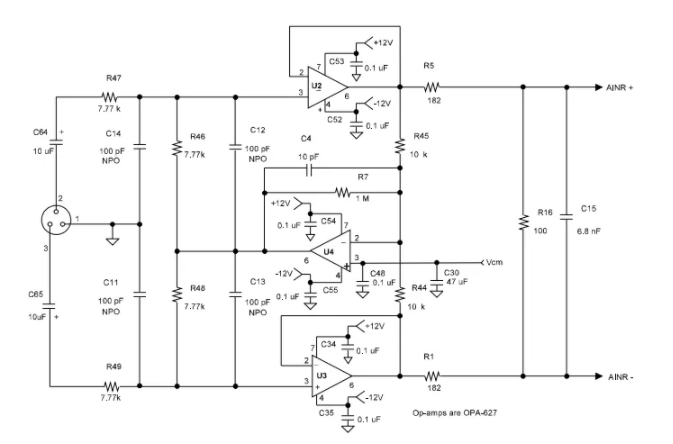

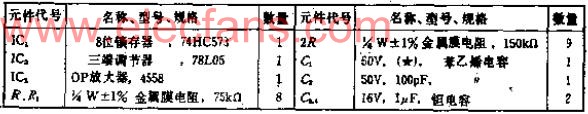

輸入緩沖器電路圖

圖 2 顯示了為此應用選擇的伺服平衡差分輸入緩沖電路。該電路通過輸入端子上任一極性的差分或單端信號提供所需的差分輸出。輸入緩沖器的增益結構旨在衰減產生 0 dBFS 數字輸出所需的 25.5 dBu (1.414 Vrms)。緩沖器輸入結構中的 6 dB 衰減之后是 A/S 轉換器輸入處的電阻網絡,它提供額外的 13.3 dB 衰減

外部支持電路設計

A/D 轉換器的這種性能可能會因外部環境設計不當而降低。本節介紹 A/D 轉換器周圍的直接環境,包括接地層推薦、去耦電容器選擇、正確的時鐘發生器連接和過壓保護。

測試設置說明

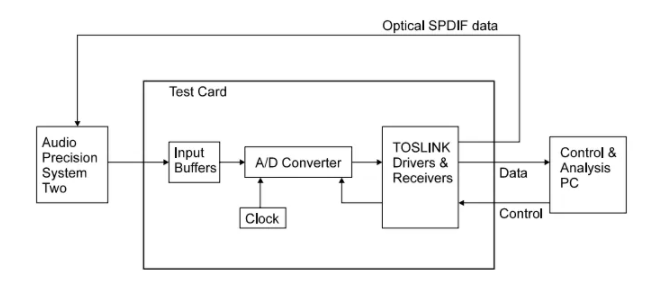

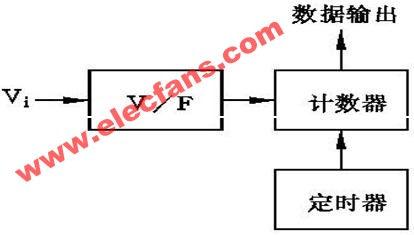

測試設置信號流

圖 3 顯示了測試設置的主要組件。這種設置的目標是提供盡可能有利的環境,使 A/D 轉換器能夠發揮其最佳性能。Audio Precision System 2 用作模擬測試信號發生器,并在 48 kHz 采樣率下確認一些測量結果。PC 用于通過其控制端口控制 A/D 轉換器,還用于收集 96 kHz 的 A/D 轉換器輸出數據。在 PC 上運行的定制軟件允許控制 A/D 轉換器和輸出數據的 FET 分析。

編輯:hfy

-

過壓保護

+關注

關注

3文章

267瀏覽量

32778 -

時鐘發生器

+關注

關注

1文章

202瀏覽量

67404 -

電阻網絡

+關注

關注

0文章

18瀏覽量

10375 -

AD轉換器

+關注

關注

4文章

250瀏覽量

41522 -

去耦電容器

+關注

關注

0文章

28瀏覽量

9018

發布評論請先 登錄

相關推薦

電流/電壓轉換電路設計方案

基于PWM實現D/A轉換電路設計

電子書:DC-DC 轉換器的應用與設計方案

基于UC3842芯片的升壓轉換電路設計方案

基于高分辨率A/D轉換器和DL技術實現時鐘穩定電路的設計

A/D 轉換器外部支持電路設計方案

A/D 轉換器外部支持電路設計方案

評論