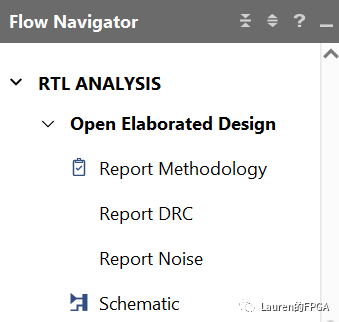

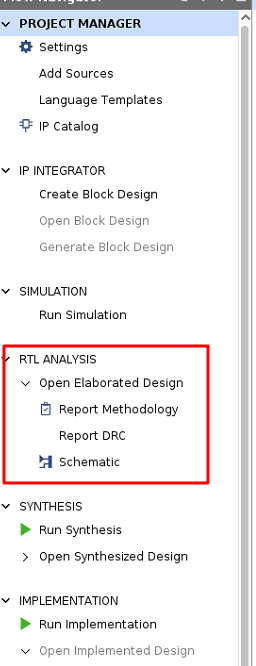

在Vivado FlowNavigator中有一個Elaborated Design,如下圖所示,屬于RTL Analysis這一步對應的設計。可能很多工程師都沒有使用到,而實際上對于代碼優化,它是很有幫助的。

通常情況下,我們總是習慣了打開綜合后的設計,執行諸如

report_timing

report_timing_summary

report_design_analysis

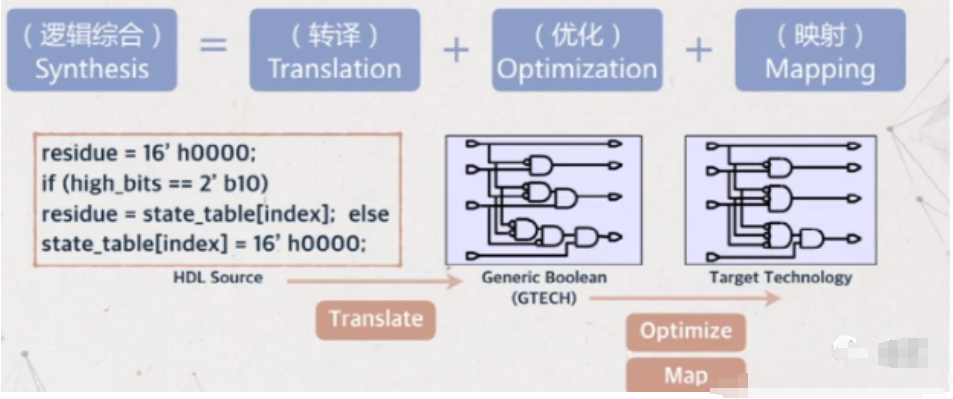

等命令分析時序,卻忽視了RTL代碼層面的優化。通過這些命令找到關鍵路徑之后,一個重要的步驟是檢查這些路徑上的邏輯單元是否很好地映射到FPGA器件中。如果沒有,就要嘗試通過修改RTL代碼、使用綜合屬性(Synthesis Attribute)、設置綜合選項、使用BlockLevel綜合技術或者使用不同的綜合策略優化RTL代碼,使得在綜合之后時序能夠達到一個較好的結果。這對于邏輯級數較高的路徑尤為重要。因為高邏輯級數的路徑會對后期布局布線帶來很大的壓力,同時成為設計整體性能提升的瓶頸,更明顯的是改善高邏輯級數路徑的常用且有效的方法是插入流水寄存器以降低邏輯級數,這一工作在設計初期完成最為快捷,越是在設計后期越難以做這一工作。

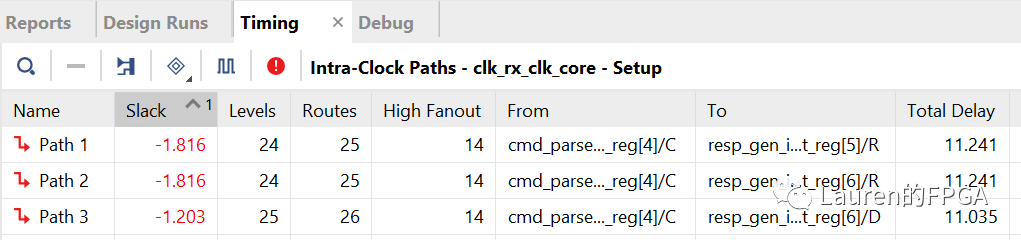

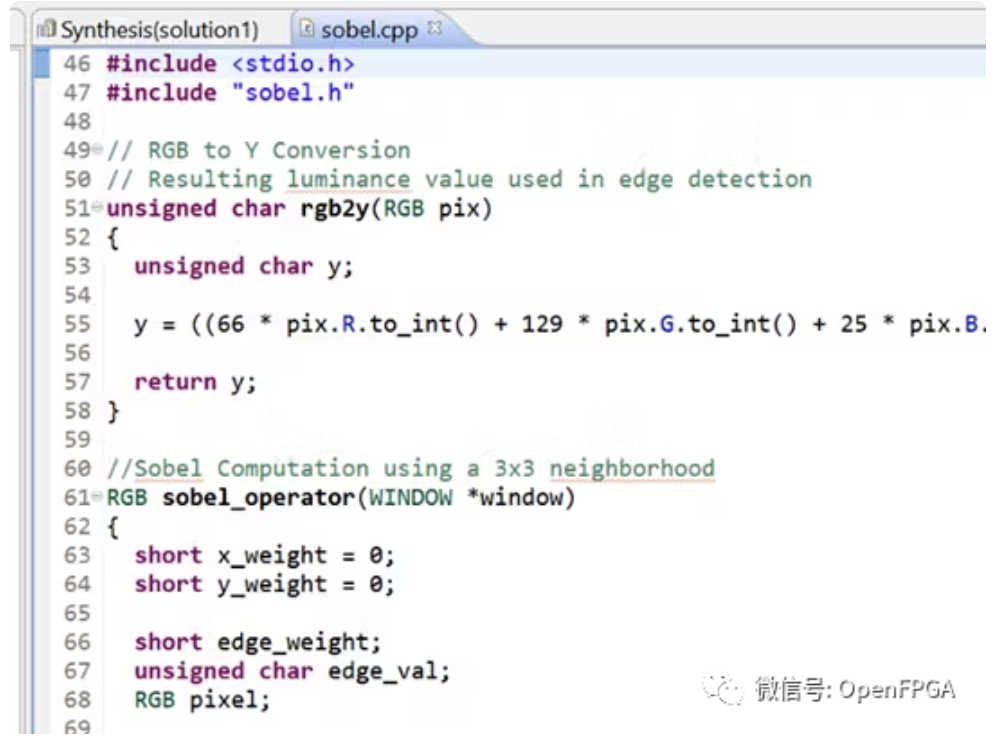

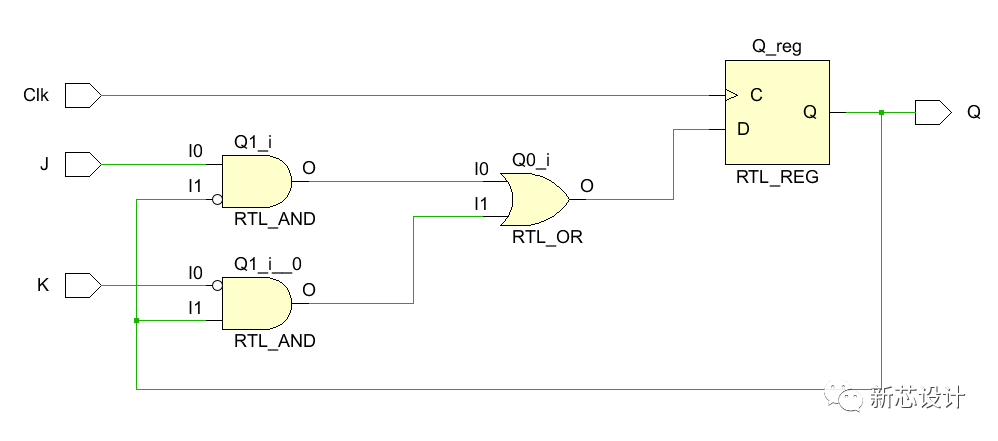

在Vivado Project模式下,同時打開Synthesized Design和ElaboratedDesign。在Synthesized Design下對設計進行分析,找到設計的關鍵路徑,生成相應的時序報告,如下圖所示。選中圖中的時序路徑,按下F4,會生成該路徑對應的Schematic視圖,同時還可以看到路徑上的邏輯單元(cell)和單元之間的連線(net)都已被選中。此時切換到Elaborated Design,按下F4,可看到這條路徑在Elaborated Design下的Schematic視圖。這時候就可以檢查這條路徑的RTL邏輯單元,尤其是注意執行了哪些操作、數據位寬是否合理。

責任編輯人:CC

-

RTL

+關注

關注

1文章

385瀏覽量

59948 -

design

+關注

關注

0文章

158瀏覽量

45778

原文標題:借助Elaborated Design優化RTL代碼

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RTL級設計的基本要素和步驟是什么

怎么利用Synphony HLS為ASIC和FPGA架構生成最優化RTL代碼?

來自vivado hls的RTL可以由Design Compiler進行綜合嗎?

怎么解決Conformal做RTL和netlist的形式驗證時綜合優化的電路也會報不相等?

RTL功耗優化

Vivado中的Elaborate是做什么的?

簡述Vivado中的Elaborate的作用

Cadence 推出 Joules RTL Design Studio,將 RTL 生產力和結果質量提升到新的高度

用Elaborated Design優化RTL的代碼

用Elaborated Design優化RTL的代碼

評論