高速電路設計中的信號衰減是讓人頭疼的一件事,作為電路設計工程師在布線時應該降低信號衰減。本文主要介紹高速電路設計中降低信號衰減方法,希望對你有所幫助。

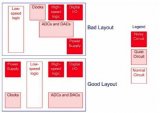

一、降低電抗路徑

在高速電路設計中,將接地層分為數字部分和模擬部分,但應將這兩個部分連接在靠近電源的地方,以便提供一條短的電抗路徑。同時,將電路接地通孔柵欄放置在高速電源平面周圍會產生良好的抑制效果,因為它會產生兩個異相輻射器。

二、保證電源完整性

高速電路設計時加一個高速地,這樣防止模擬電路和數字電路對高速電路部分產生干擾和輻射。如果層數允許,將高速電源平面放置在兩個接地平面之間,這將使板上的高速電源平面和接地平面分離。

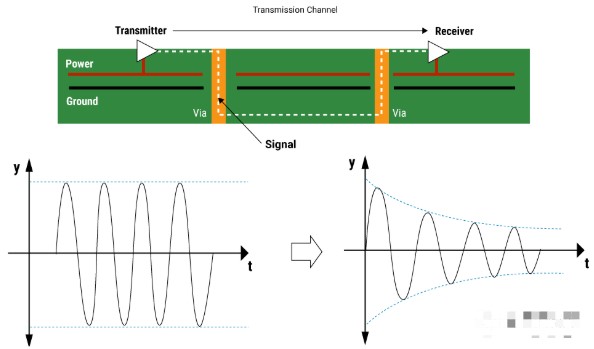

三、確保阻抗一致性

在高速電路設計中,由于高速信號會在較短的走線上產生傳輸線效應,因此較好使高速走線盡可能短。在電路板上使用阻抗控制,以確保走線在整個電路板上具有一致的阻抗。

四、注意過孔

高速電路設計時,以盡量降低使用過孔數量。因為每個通孔都會給走線增加阻抗,而設計通孔以使其具有與走線匹配的特定阻抗非常困難。應該對任何通孔進行反鉆,以防止信號共振,并且應格外小心,以確保差分對上的反鉆是對稱的。如果必須要在高速走線上使用過孔,選擇是并行使用兩個過孔以防止阻抗變化。這樣有兩個好處,1、它降低了走線上的附加阻抗;2、并聯的兩個通孔的總阻抗降低,從而增加了通孔對信號的低諧振頻率。

五、使用表面貼裝元件

高速信號設計時,使用表面貼裝元件。因為使用通孔組件,則元件引腳上的剩余部分會產生另一個信號反射源,從而引起信號衰減。

編輯:hfy

-

pcb

+關注

關注

4326文章

23160瀏覽量

399935 -

高速電路設計

+關注

關注

2文章

20瀏覽量

8181

發布評論請先 登錄

相關推薦

PCB高速信號電路設計的三大布線技巧詳解

高速電路設計中的信號完整性問題是什么?怎么解決這些問題?

高速電路設計中的信號完整性問題是什么?怎么解決?

講解高速PCB的布線、布局和電路設計

高速pcb電路設計中降低信號衰減方法

高速pcb電路設計中降低信號衰減方法

評論