本篇主要介紹常用的單端邏輯電平,包括TTL、CMOS、SSTL、HSTL、POD12等。

1、TTL電平

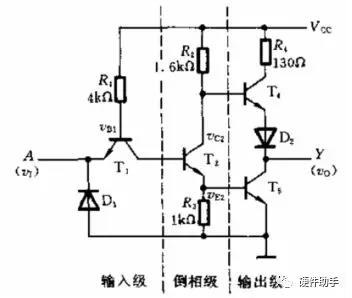

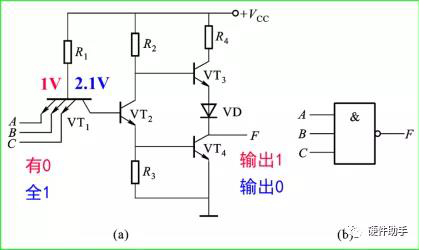

下面以一個三輸入的TTL與非門介紹TTL電平的原理。

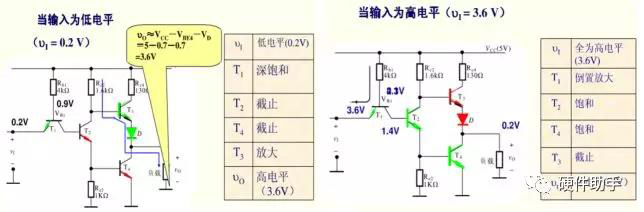

當輸入全1時,uI=3.6V,VT1處于倒置工作狀態(集電結正偏,發射結反偏),uB1=0.7V×3=2.1V(后級電路決定的),VT2和VT4飽和,輸出為低電平uO=0.3V。

當輸入有0時,uI=0.3V,VT1發射結導通,uB1=0.3V+0.7V=1V,VT2和VT4均截止,VT3和VD導通。輸出高電平uO=VCC-UBE3-UD≈5V-0.7V-0.7V=3.6V。

TTL電平一般過沖都會比較嚴重,可以在始端串22歐或33歐電阻(因為TTL電路的輸出阻抗大約為17Ω左右,從阻抗匹配的角度解釋);TTL電平輸入腳懸空時內部認為是高電平。

常見的TTL電平有5V TTL,3.3V LVTTL,2.5V LVTTL,1.8V LVTTL等。

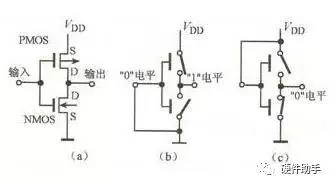

2、CMOS電平

常見的CMOS電平有5V CMOS,3.3V LVCMOS,2.5V LVCMOS,1.8V LVCMOS,1.5V LVCMOS,1.2V LVCMOS,0.8V LVCMOS等。

CMOS電路輸出高電平是通過導通PMOS實現的,輸出低電平是通過導通NMOS實現的,PMOS的載流子為空穴,NMOS的載流子為電子,空穴的電導率低于電子,所以PMOS的導通電阻比NMOS的導通電阻大(且相同額定值的PMOS比NMOS貴!!!),也就是輸出高電平時其RC(C為傳輸線等效電容,寄生電容等)時間常數大,上升沿更緩,CMOS電路的上升時間比下降時間長。

CMOS器件是電壓控制器件,而未被連接的輸入端有靠近CMOS門檻電壓輸入的趨勢,使得芯片內部的三極管作不必要的開關動作,這既增加了噪聲干擾,又耗費了系統功率。MOS管輸入阻抗很大(柵極源極之間有一層氧化層),輸入阻抗大,對微弱信號的捕捉能力就很強(簡單地把干擾源等效為一個理想電壓源和一個內阻的串聯,根據分壓原理可知輸入電阻越大輸入的分壓越大),所以懸空時很容易受周圍信號的干擾。一般,使用上拉電阻或下拉電阻,把未被連接的輸入引腳與電源或接地點連接,使它們有一個確定的電壓值。CMOS輸入引腳的最大輸入電流非常小,只有1μA左右(最多幾μA),因此選用1MΩ作為上拉電阻或下拉電阻就可以。

在許多嵌入式系統中,輸入引腳的有效電壓一般是5V以上或為負值(對地),在這種情況下,使用幾個電阻就可以防止輸入引腳過壓。CMOS集成塊內部的兩個二極管可以把電壓鉗位在CMOS器件輸入電壓值,這兩個二極管是高速CMOS器件(74HC系列)靜電保護措施的一部分。

TTL集成電路內部都是用雙極型三極管構成的,這種電路的輸入電阻一般都不高(7400和74LS00這些門電路的輸入電流一般都在幾百μA以上,74LS系列的稍小一些),對外界各種雜波不是很敏感,故不用的輸入端懸空即可(懸空相當于高電平!),亦可以直接接高電平或地(視具體情況而定)。

3、GTL(Gunning Transceiver Logic)電平

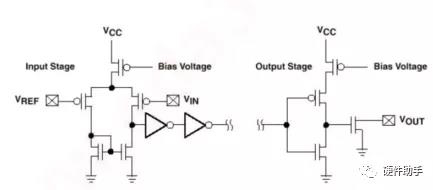

GTL輸入電路是一個電壓比較器,輸入電壓同一個外部連接的參考電壓進行比較,輸入門限設計為精確的窗口電壓,可以提高最大的抗噪性能。輸出電路是一個漏極開路N通道器件,當電路關閉時輸出電壓被上拉到末端匹配電壓VTT,當輸出電路打開時,器件可以吸收40mA的電流,可以產生最大的輸出電壓0.4V。輸出電阻為25歐姆,輸入輸出被設計為與VCC的電壓獨立,器件可以工作在5V、3.3V,甚至是2.5V的VCC電壓。

GTL和GTL+信號的參考電平Vref為信號上拉電平的2/3,這是同GTL電平的特點相關的,GTL信號的低電平一般為上拉電平的1/3左右,當GTL信號的參考電平設置為上拉電平的2/3時信號的高低電平有最大的抗噪冗余量,可以得到最佳的傳輸效果。現在很多廠家提供的GTL芯片的Vref都是可以通過外部進行調整,提供最佳的信號傳輸要求。同時因為GTL的輸入閾值電平都很小,可以提供大的噪聲容限,而小的輸出電平提供的信號變化也很小。這些對信號的完整性有利。GTL+的信號的電平更高,有更大的驅動能力,一般對于重負載情況下使用GTL+的效果會更好一些。

4、SSTL電平

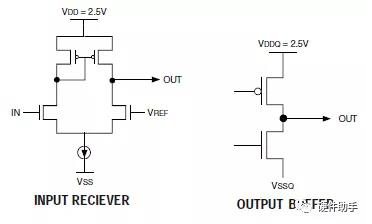

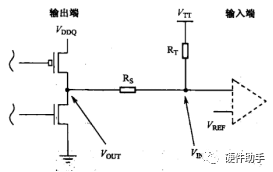

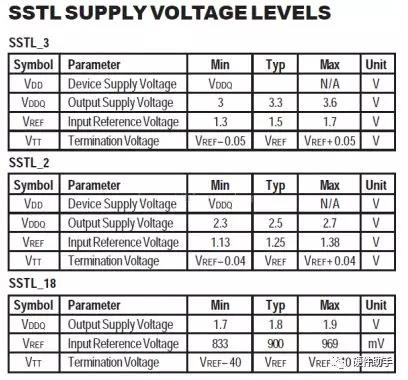

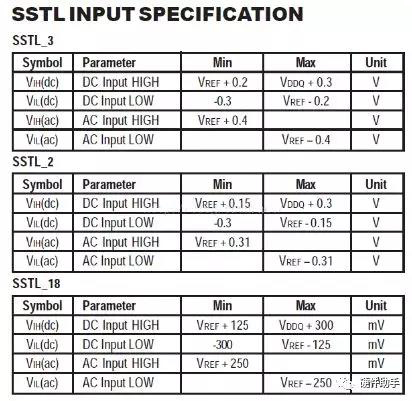

SSTL即Stub Series Termination Logic,分為SSTL_3(3.3V)、SSTL_2(2.5V)、SSTL_18(1.8V)、SSTL_15(1.5V)(對應的VREF=VTT分別為1.5V、1.25V、0.9V、0.75V),對應不同的供電電壓,SSTL是傳輸線終端匹配的,因此SSTL具有輸出阻抗和匹配方法的要求,這使其在高速信號傳輸時降低了EMI,改善了建立時間。SSTL的輸入是一個差分比較電路,一端為輸入,另一端為參考電壓VREF。DDR使用的就是SSTL電平標準。

STL對于不同類型的驅動器有不同的參數。SSTL_3和SSTL_2定義了2類驅動器,以區別不同的終端匹配方案。SSTL_18沒有明確的類型定義,但是,取決于終端環境,驅動器必須能夠在輸入緩沖處產生相應的電壓擺幅。

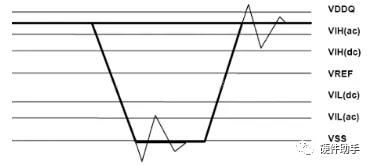

AC參數指的是一個閾值電壓,當信號跨越這個閾值電壓時,接收器狀態一定會發生改變。只要輸入保持在定義的DC閾值之上,接收器將維持邏輯狀態不變。這有利于系統設計者對整個系統性能進行優化。

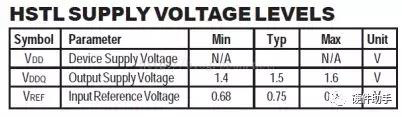

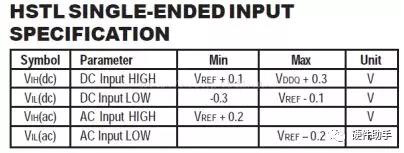

5、HSTL電平

HSTL即High Speed Transceiver Logic,其最主要用于高速存儲器讀寫,傳統的慢速存儲器阻礙了高速處理器的運算操作。在中頻區域(100~180MHz),可供選擇的單端信號IO結構有:HSTL、GTL/GTL+、SSTL、LVTTL;在180MHz以上,HSTL是唯一可用的單端IO接口。QDR使用的就是HSTL電平標準

JEDEC定義了四種驅動模式:Class I~IV,其區別僅在于輸出電流的不同:

? Class I:IOH≥8mA,IOL≥-8mA;并行終端負載

? Class II:IOH≥16mA,IOL≥-16mA;串行終端負載

? Class III:IOH≥8mA,IOL≥-24mA;并行終端負載

? Class IV:IOH≥8mA,IOL≥-48mA;并行終端負載

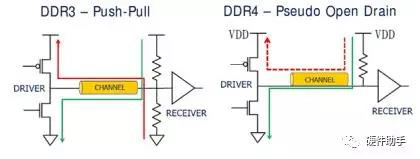

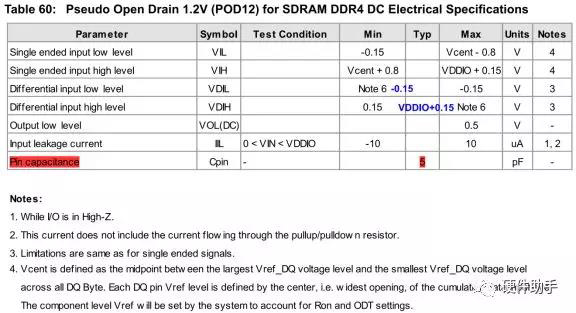

6、POD12電平

POD和SSTL的最大區別在于接收端的終端電壓(POD為VDDQ,SSTL為VDDQ/2)。POD可以降低寄生引腳電容和I/O終端功耗,并且即使在VDD電壓降低的情況下也能穩定工作。

當驅動端的上拉電路導通,電路處于高電平時,回路上沒有電流流過,這樣的設計較少了功耗。

除了上述一些常見的單端電平之外,還有BTL、ETL、HSUL等等。詳細可參見相關標準。

編輯:hfy

-

CMOS

+關注

關注

58文章

5736瀏覽量

236099 -

TTL

+關注

關注

7文章

504瀏覽量

70427 -

邏輯電平

+關注

關注

0文章

158瀏覽量

14473 -

HSTL

+關注

關注

0文章

4瀏覽量

9666

發布評論請先 登錄

相關推薦

常見單端邏輯電平(TTL、CMOS、SSTL、HSTL、POD12)

常見單端邏輯電平(TTL、CMOS、SSTL、HSTL、POD12)

評論