描述

本設計咨詢主要介紹一個錯誤的時鐘偏移計算導致錯誤時序收斂的問題。

出現問題的情況:

這可能會影響使用生成時鐘的設計,其具有以下特征:

- 使用 Vivado 2018.2.x 及更早版本。

- 用戶生成的時鐘沒有使用‘-master_clock’定義

- 在同一時鐘網絡的并行分支上的層級引腳上創建的主時鐘或生成的時鐘連接至上述用戶生成的時鐘源引腳

在上述情況下,時序引擎可能會為生成的時鐘選擇錯誤的主時鐘,這可能會導致在路徑上報告的不正確時鐘偏移。

在 Vivado 2018.3 中,定時器使用正確的主時鐘,這會導致相同路徑上不同的時鐘偏移和不同的簽收時序。

注:如果用戶生成的時鐘用‘-master_clock’創建并指向正確的主時鐘,該問題就不會出現。

該問題的示例:

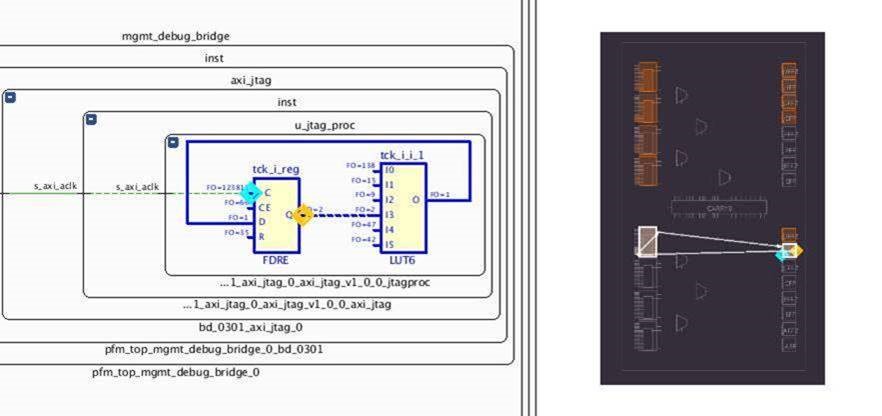

在本示例中,datapath 通過 LUT 循環回到相同的寄存器。寄存器和 LUT 都放在同一個 SLICE 中。

示例時鐘拓撲:

示例 Datapath 拓撲:

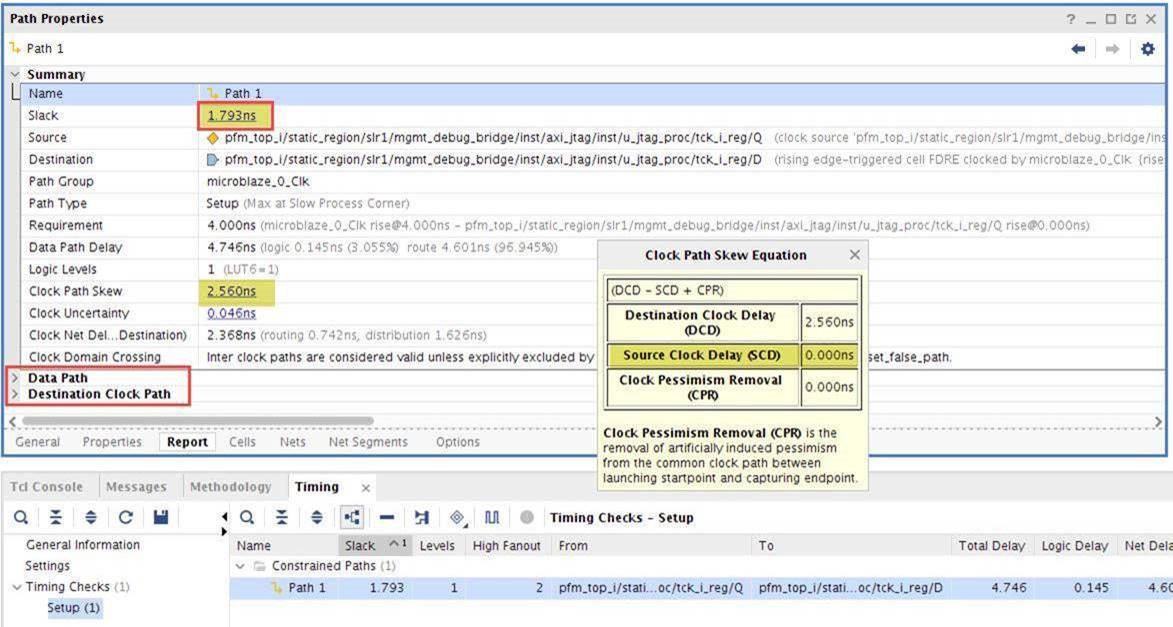

請注意,由于缺少源時鐘路徑,2.560nS 的路徑偏移過大。

由于選擇了錯誤的主時鐘進行時序分析,因此在工具選擇的主時鐘和用戶生成的時鐘之間沒有路徑,從而導致較大的時鐘偏移。

這將迫使路由器在路徑上通過一個較長的路由繞道來修復保持違規。

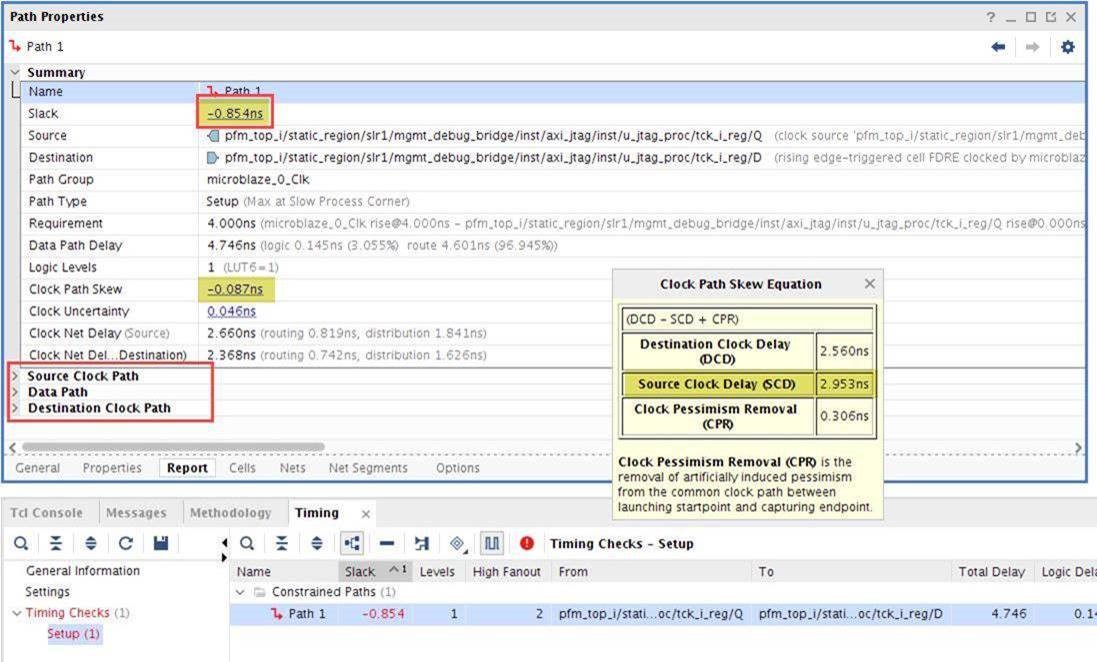

該路徑通過在 Vivado 2018.3 中重新加載路由后檢查點來顯示違規:

在 Vivado 2018.3 中,由于可以計算源時鐘延遲,因此路徑偏移要小得多。

時鐘偏移會導致設置違規,這是由于在該路徑上為了修復 Vivado 2018.2.x 及更早版本中出現的保持違規而繞道了很長的路由路徑。

可能會出現問題的典型情況:

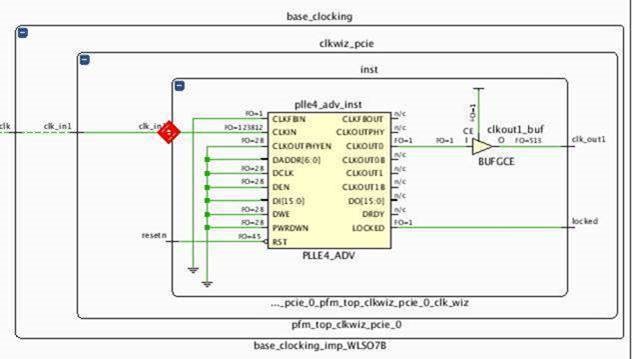

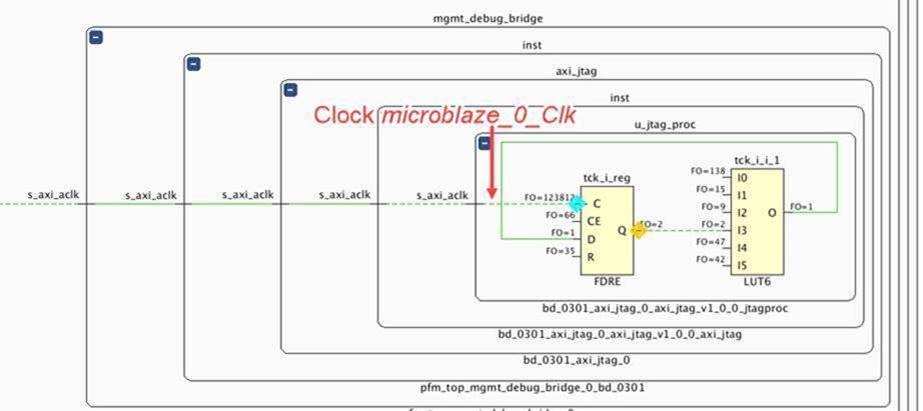

在本實例中,在層級引腳上創建的主時鐘不正確。

有問題的時鐘約束來自輸入時鐘源選項被設置為“單端時鐘支持引腳(默認)”或“差分時鐘支持引腳”而 IP 時鐘輸入沒有連接至頂層輸入端口的時鐘向導。

####################################################################################

# Constraints from file : 'pfm_top_clkwiz_kernel_0.xdc'

####################################################################################

current_instance -quiet

current_instance pfm_top_i/static_region/slr1/base_clocking/clkwiz_kernel/inst

create_clock -period 10.000 [get_ports -scoped_to_current_instance clk_in1]

set_input_jitter [get_clocks -of_objects [get_ports -scoped_to_current_instance clk_in1]] 0.100

在時鐘向導輸入時鐘源設置為“全緩沖”或“無緩沖”時,層級引腳上沒有創建主時鐘。

確認:

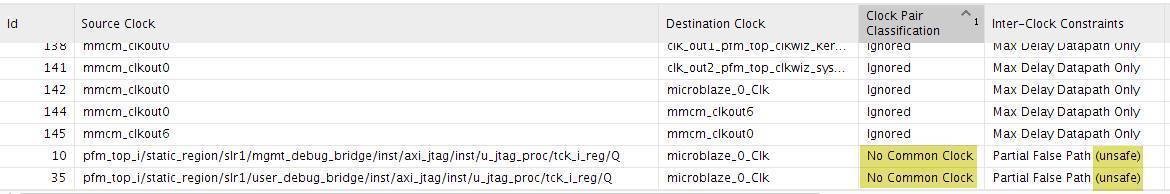

上述問題由‘report_methodology’檢測報告。

建議始終運行“report_methodology”并處理報告的違規:

TIMING-6#1 Warning

No common primary clock between related clocks

The clocks pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q and microblaze_0_Clk are related (timed together) but they have no common primary clock. The design could fail in hardware. To find a timing path between these clocks, run the following command: report_timing -from [get_clocks pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q] -to [get_clocks microblaze_0_Clk]

Related violations:

TIMING-30#1 Warning

Sub-optimal master source pin selection for generated clock

The generated clock pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q has a sub-optimal master source pin selection, timing can be pessimistic

Related violations:

TIMING-36#1 Warning

Invalid Generated Clock due to missing edge propagation

There is no rising/falling edge propagation between master clock pfm_top_i/static_region/slr1/base_clocking/clkwiz_pcie/inst/clk_in1 to generated clock pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q

Related violations:

Vivado 2018.2.x 和 2018.3 中也會報告 TIMING-27 違規。

TIMING-27 檢查指向層級引腳上不正確的主時鐘定義,這可能會導致不安全的時序。

TIMING-27#1 Warning

Invalid primary clock on hierarchical pin

A primary clock pfm_top_i/static_region/slr1/base_clocking/clkwiz_kernel/inst/clk_in1 is created on an inappropriate internal pin pfm_top_i/static_region/slr1/base_clocking/clkwiz_kernel/inst/clk_in1. It is not recommended to create a primary clock on a hierarchical pin when its driver pin has a fanout connected to multiple clock pins

Related violations:

此外,在 Vivado 2018.2 中,‘report_clock_interaction’也會顯示不安全的時鐘對,但在 2018.3 版中不會:

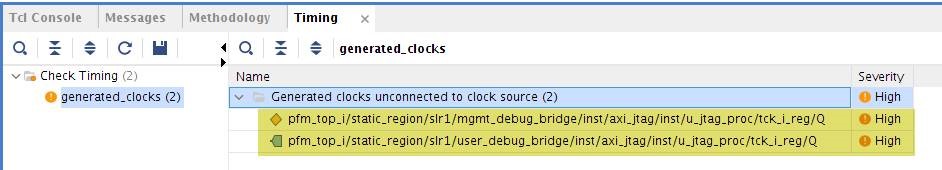

‘check_timing’報告了一個在 2018.2.x 中生成的時鐘的問題:

‘report_clock’報告 Vivado 為用戶生成的時鐘使用的實際主時鐘。

雖然時鐘 microblaze_0_Clk 傳播至所生成時鐘的源引腳,但‘report_clocks’會按照主時鐘報告 pfm_top_i/static_region/slr1/base_clocking/clkwiz_pcie/inst/clk_in1:

Vivado 2018.2.x:

report_clocks pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q

Generated Clock : pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q

Master Source : pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/C

Master Clock : pfm_top_i/static_region/slr1/base_clocking/clkwiz_pcie/inst/clk_in1

Divide By : 8

Generated Sources : {pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q}

Vivado 2018.3:

report_clocks pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q

Generated Clock : pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q

Master Source : pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/C

Master Clock : microblaze_0_Clk

Divide By : 8

Generated Sources : {pfm_top_i/static_region/slr1/mgmt_debug_bridge/inst/axi_jtag/inst/u_jtag_proc/tck_i_reg/Q}

解決方案

該問題將在 Vivado 2018.3 中修復。

出現該問題時,通常的解決方法是在創建用戶生成的時鐘時指定主時鐘名:

create_generated_clock -source [get_pins -filter REF_PIN_NAME=~C -of_objects [get_cells -hierarchical -filter {NAME =~ "*/u_jtag_proc/tck_i_reg*"}]] -divide_by 8 [get_pins -filter REF_PIN_NAME=~Q -of_objects [get_cells -hierarchical -filter {NAME =~ "*/u_jtag_proc/tck_i_reg*"}]] -master_clock microblaze_0_Clk

但在本示例設計中,最初的問題是沒有正確配置時鐘向導。

對于該設計,需要重新運行時鐘向導并糾正配置。

常見問題解答:

1) 該問題會影響 Vivado 的哪些版本?

該問題會影響 Vivado 2018.2 及更早版本。

2) 如果一個設計使用 2018.2 及更早 Vivado 版本符合時序要求,那用戶對時序覆蓋范圍應該有多大的信心?(如果他們不想升級至最新 Vivado 版本,即 2018.3)

該漏洞主要針對錯誤的/部分時鐘定義。因此,如果設計有適當的約束,并且符合時序要求,那就不應該有問題。

要進行完整性檢查,您可以運行以下命令并查找與時序相關的警告/重要警告。

- 運行‘report_clock’命令并驗證 所有主時鐘(‘create_clock’約束)是否都在 I/O 端口上。

- 運行‘report_method’命令并驗證在設計中是不是沒有 Timing-6、Timing-27、Timing-30 和 Timing-36 警告。

- 建議使用‘master_clock’選項編輯‘generated_clock’約束。

注:請參閱 (UG903) 和 (UG835),了解更多詳情。

3) 在 Vivado 2018.3 中,用戶是需要為生成的時鐘約束使用‘master_clock’選項,還是這只是在早期 Vivado 版本中避免該問題的解決方法?

該問題已在 Vivado 2018.3 中修復。

根據 Xilinx 方法指南,始終建議為‘generated_clock’約束使用‘master_clock’選項。這個建議不僅僅只針對早期的 Vivado 版本。

4) 將設計從 Vivado 2018.2 及更早版本升級至 Vivado 2018.3 版有多安全?

該問題已在 Vivado 2018.3 中修復。

將設計從舊 Vivado 版本升級至最新的 Vivado 版本(即 2018.3)沒有風險。

5) 在我的設計中有一個上述警告,但是電路板上一切正常,時序得分為 0,忽略該警告安全嗎?

Xilinx 建議搞清楚警告的根本原因并正確修復。

重要通知:

Timing-6:如果該警告發生在介紹部分列出的條件下,就需要應用上述解決方法來解決該問題。

-

寄存器

+關注

關注

31文章

5363瀏覽量

121196 -

路由器

+關注

關注

22文章

3745瀏覽量

114490 -

Slice

+關注

關注

0文章

7瀏覽量

8088 -

Vivado

+關注

關注

19文章

815瀏覽量

66893 -

時鐘網絡

+關注

關注

0文章

16瀏覽量

6583

發布評論請先 登錄

相關推薦

常見xgboost錯誤及解決方案

常見電位測量錯誤及解決方案

EEPROM編程常見錯誤及解決方案

dac161p997這幾個寄存器全配置為0,當發生錯誤時,dac161p997會不會依據錯誤的數據進行輸出?

常見的GND連接錯誤及解決方案

SQL錯誤代碼及解決方案

aes加密的常見錯誤及解決方案

socket 常見錯誤與解決方案

CAN總線常見錯誤碼及其解決方法

SUMIF函數常見錯誤及解決方案

網關錯誤是什么意思

時鐘抖動和時鐘偏移的區別

FPGA 高級設計:時序分析和收斂

一文讀懂CAN通訊錯誤幀

介紹一個IC設計錯誤案例:可讀debug寄存器錯誤跨時鐘

錯誤時鐘偏移計算導致錯誤時序收斂的解決方案

錯誤時鐘偏移計算導致錯誤時序收斂的解決方案

評論