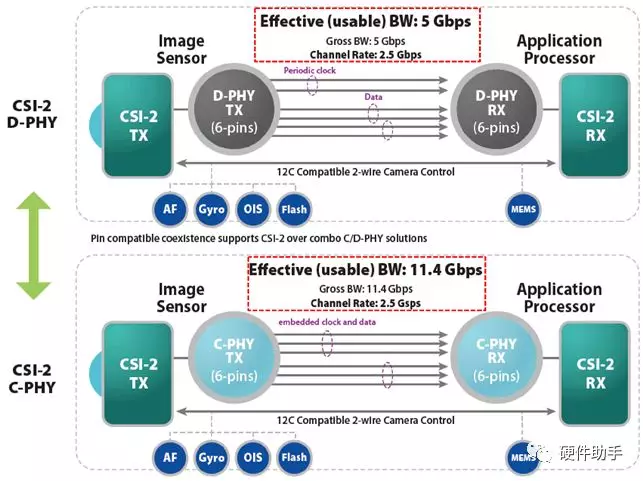

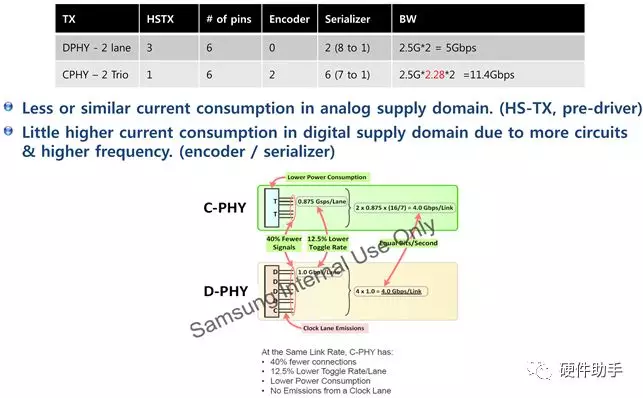

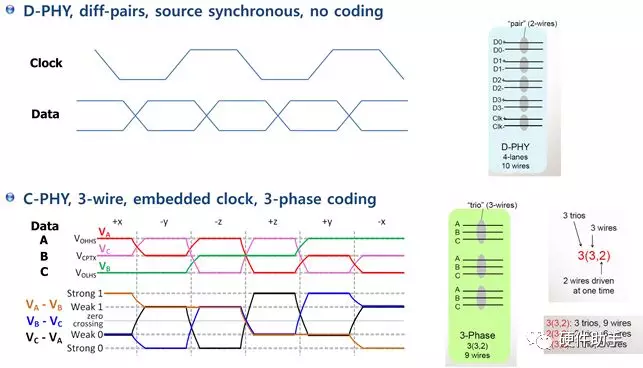

本篇主要介紹物理層WG中的C-PHY。C-PHY基于3-Phase symbol編碼技術,通過three-wire trios傳輸2.28 bits/symbol,其目標速率是2.5Gsymbols/s。C-PHY與D-PHY有許多共同點,C-PHY的絕大部分特性都是從D-PHY改編而來的。C-PHY被設計成能夠與D-PHY在同一個IC管腳上共存,從而可以開發出既支持C-PHY又支持D-PHY的雙模器件。

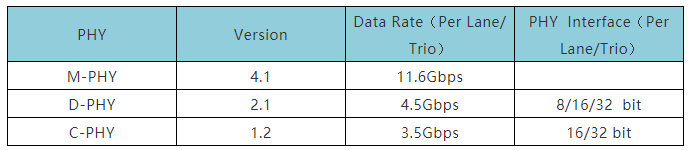

由于C-PHY絕大部分特性和D-PHY一樣,因此該部分主要通過對比D-PHY進行介紹,同時在某些時候也會對比M-PHY對整個PHY層進行一個全面的對比總結。

MIPI C-PHY 通過帶寬受限的通道提供高吞吐量,將顯示器和攝像頭連接到應用處理器。它為MIPI CSI-2和MIPI DSI-2生態系統提供PHY,使設計人員能夠擴展實現支持各種更高分辨率的圖像傳感器和顯示器,同時保持低功耗。同時它還可以應用于許多其他地方,例如汽車攝像頭傳感系統,防撞雷達,車載信息娛樂系統和儀表盤等。

MIPI C-PHY是一種嵌入式時鐘鏈路,可為鏈路內的重新分配通道提供極大的靈活性。

C的真正含義是“C-PHYs may be used in channel-limited applications, hence the use of the character “C””。

它還提供高速和低功耗模式之間的低延遲轉換。MIPI C-PHY通過在雙線通道上脫離傳統的差分信號技術并引入大約2.28位/符號的三相符號編碼來在三線通道上傳輸數據符號來實現這一點,其中每個通道包括嵌入式時鐘。以3 Gsym / s運行的三個three-wire trios接口上實現了大約24 Gbps的峰值數據速率。MIPI C-PHY可以與MIPI D-PHY在同一設備上引腳共存,因此設計人員可以開發雙模設備。

鏈路的操作和可用數據速率可以是不對稱的,這使實現人員能夠根據系統需求優化傳輸速率。支持雙向和半雙工操作。

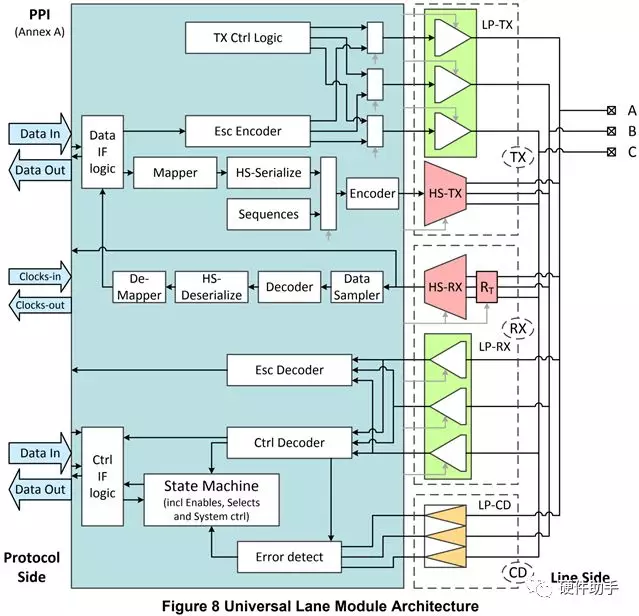

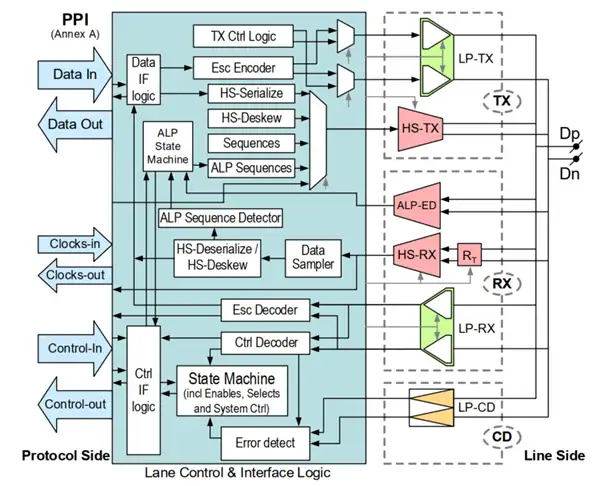

1、架構

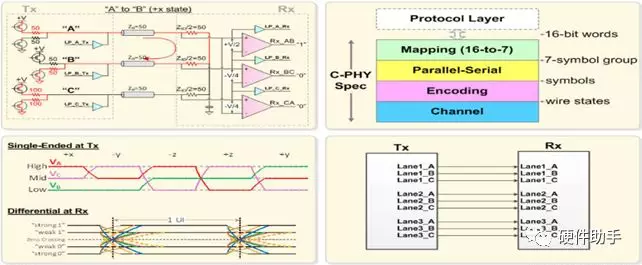

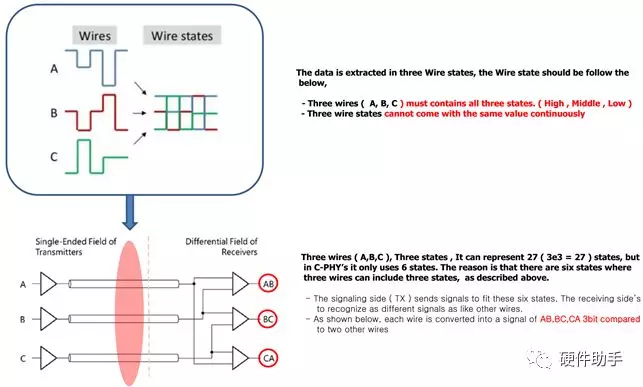

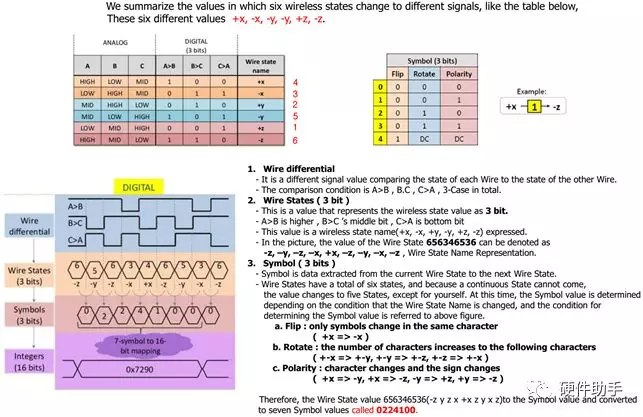

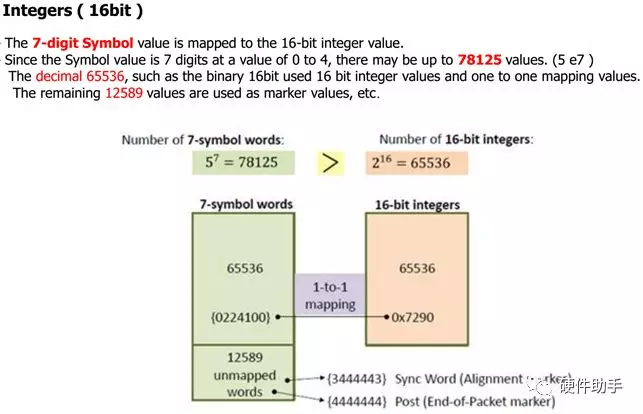

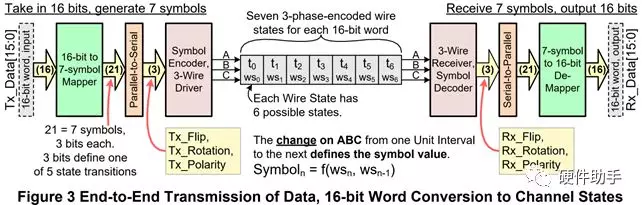

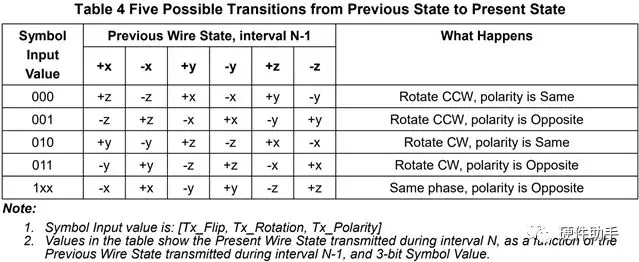

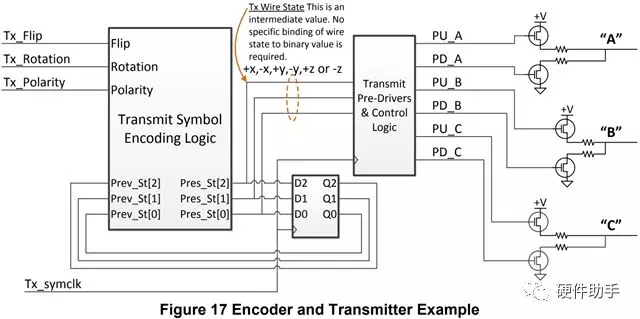

C-PHY使用 3-Phase symbol encoding技術,每一個符號可以傳輸2.28bits數據。C-PHY復用了大部分D-PHY的標準,能和D-PHY在同一芯片中共存,但是其數據編碼技術和D-PHY有本質的區別,其特性如下:

- 使用三根線一組傳輸,而不是之前使用的差分對;

- 采用5進制傳輸,效率高于D-PHY的二進制,效率為原來的2.27倍;

- 沒有時鐘信號,由于使用了三根線,并且時鐘編碼到每一個symbol中,而且在每一個symbol boundary都有電壓的跳變,時鐘恢復也比較簡單。

C-PHY lane is known as a Trio. 1 Sym=2.28 bits

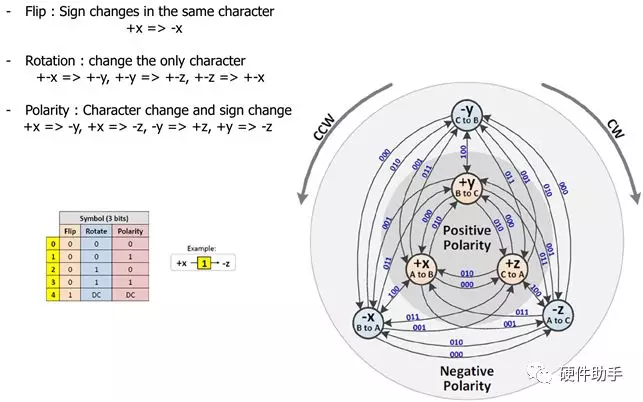

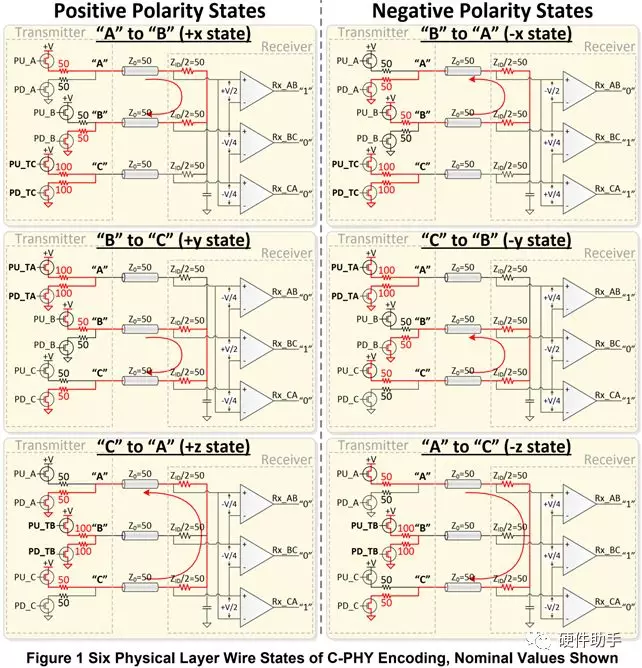

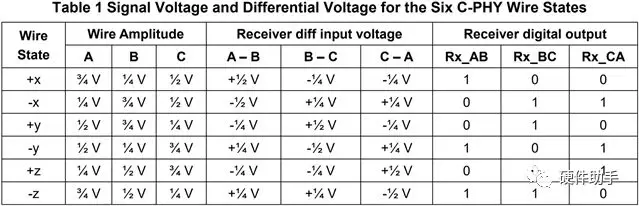

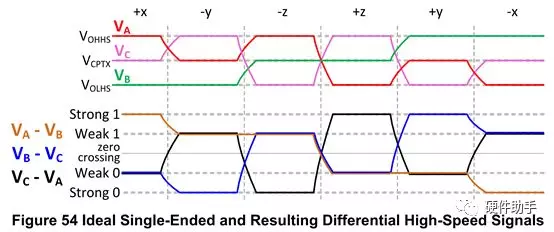

2、3-Phase symbol encoding

3、操作模式及模式轉換

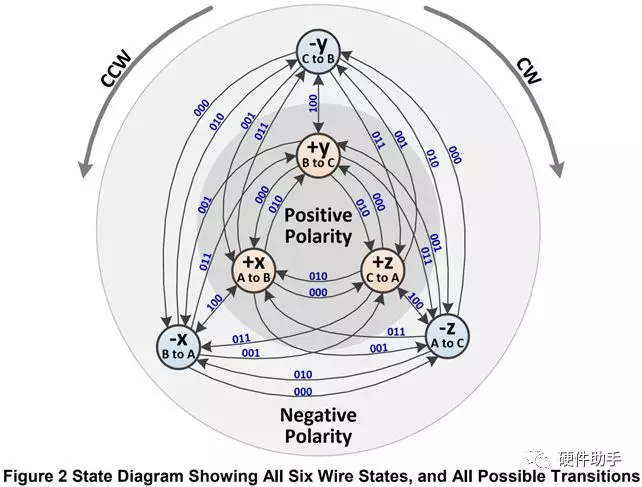

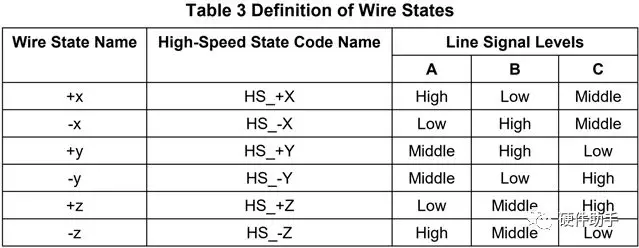

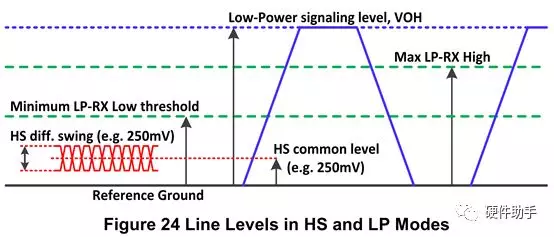

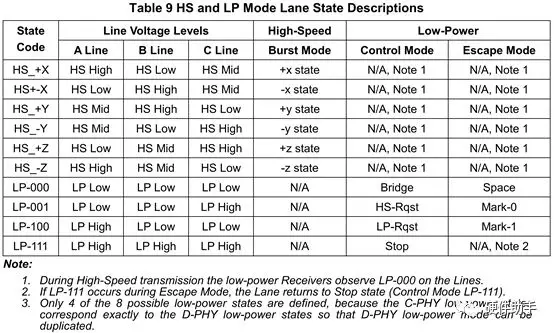

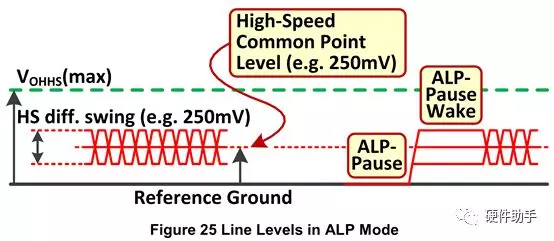

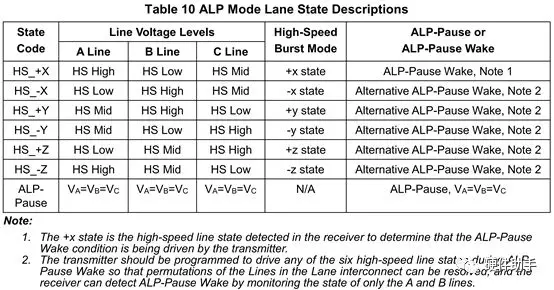

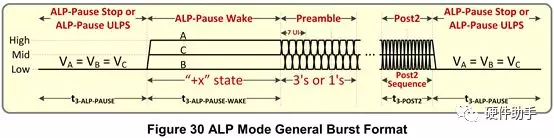

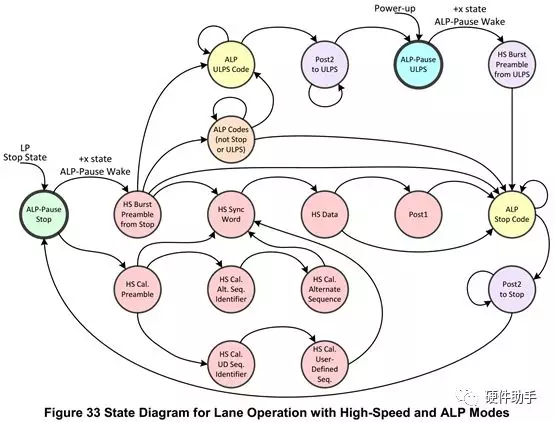

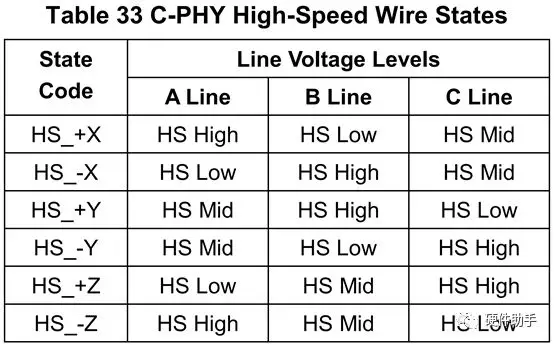

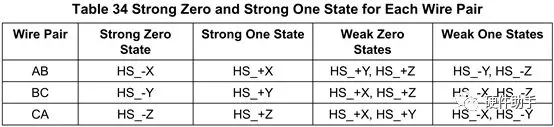

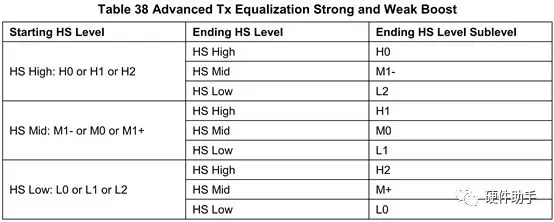

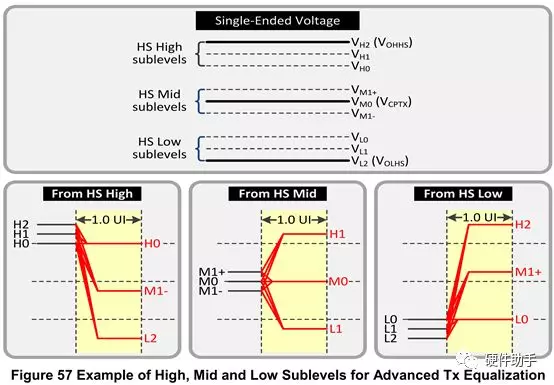

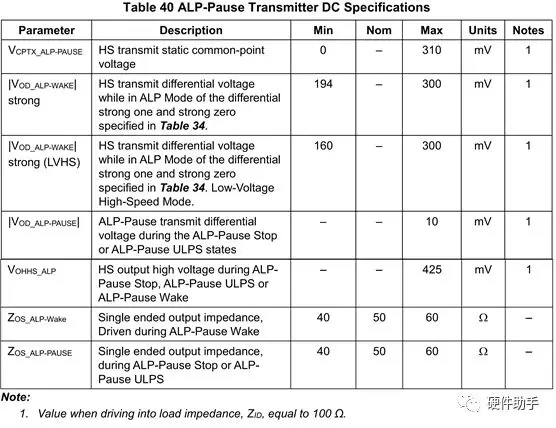

C-PHY一共有三種模式:HSMode、LPMode和AlternateLow-Power (ALP) mode,其中HS Mode傳輸線有六種狀態:+x, -x, +y, -y, +z and–z,LPMode傳輸線有四種狀態:LP-000,604 LP-001, LP-100 and LP-111,ALP Mode除了HS Mode的六種狀態之外還定義了兩種狀態ALP-Pausestate (VOD = 0) and ALP-Pause Wake state (VOD = |VOD| Strong),其中ALP-Pause有可以分為ALP-PauseStop and ALP-Pause ULPS兩種。

- 一個典型的HS傳輸過程的序列為:LP-111→LP-001→LP-000→HS→LP-111;

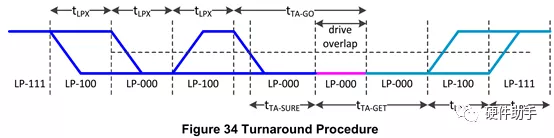

- 轉向(TurnAround)的序列為:LP-111→LP-100→LP-000→LP-100→LP-000;

-

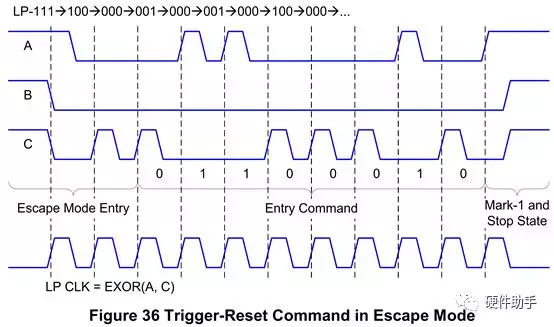

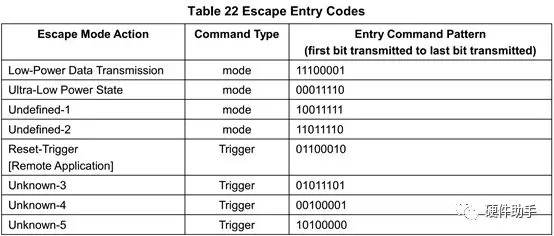

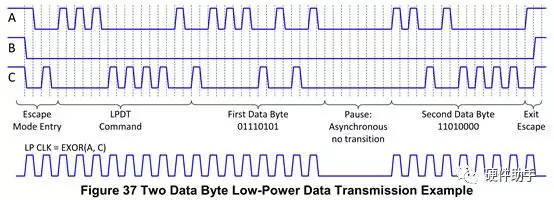

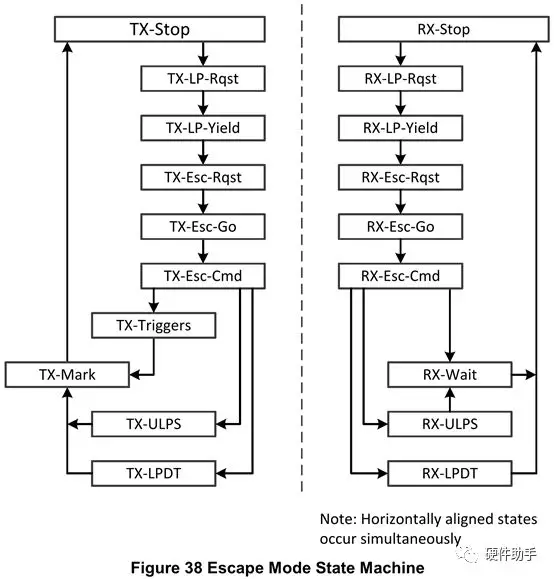

EscapeMode傳輸過程的序列為:LP-111→LP-100→LP-000→LP-001→LP-000;

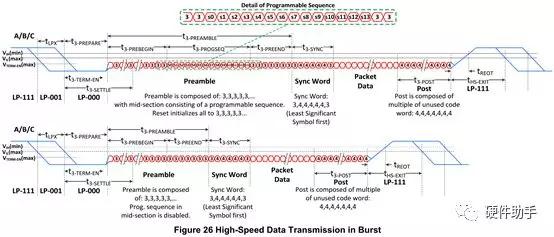

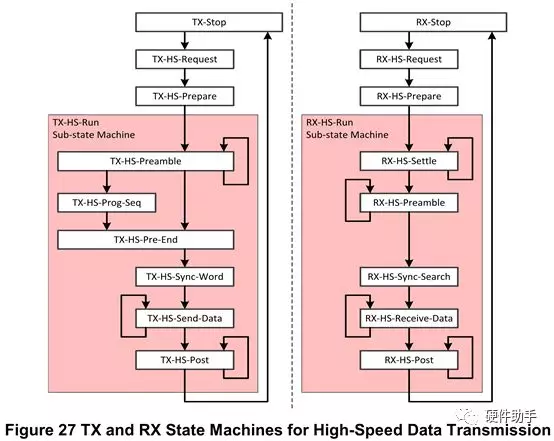

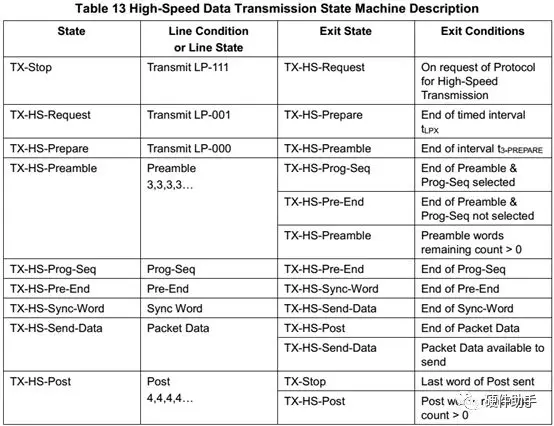

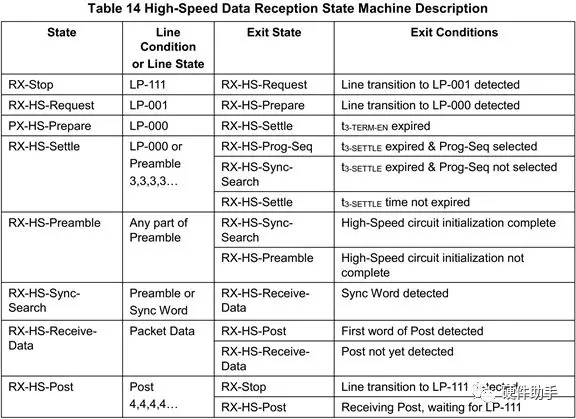

3.1、High-Speed Data Transmission

Start-of-Transmission的流程如下表所示:

-

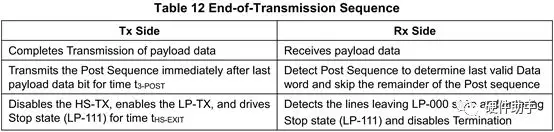

End-of-Transmission的流程如下表所示:

-

HS Data Transmission Burst的流程如下所示:

-

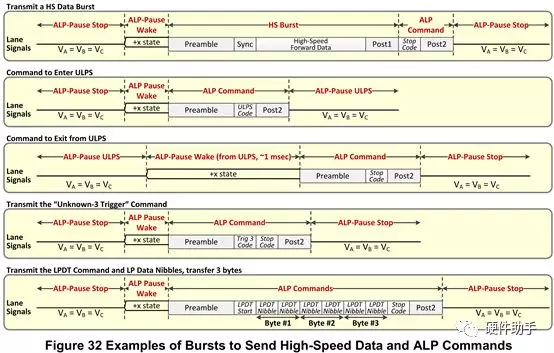

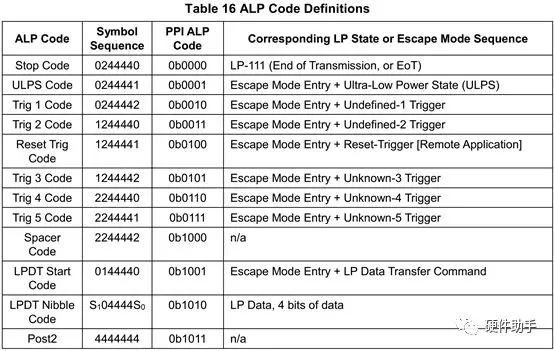

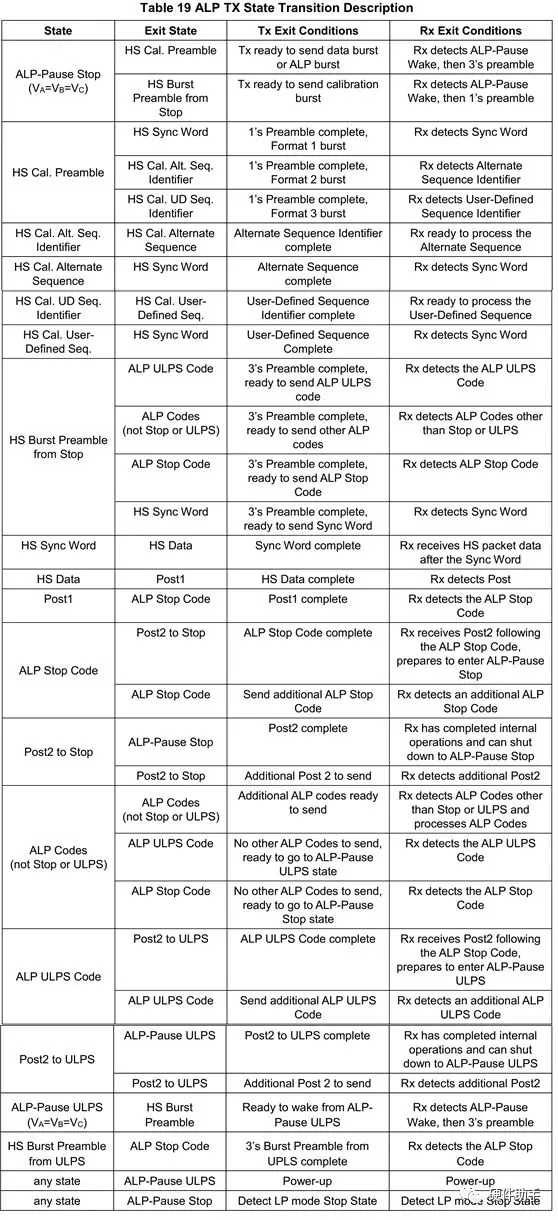

3.2、ALP Mode Transmission Burst

-

3.3、Bi-Directional Lane Turnaround

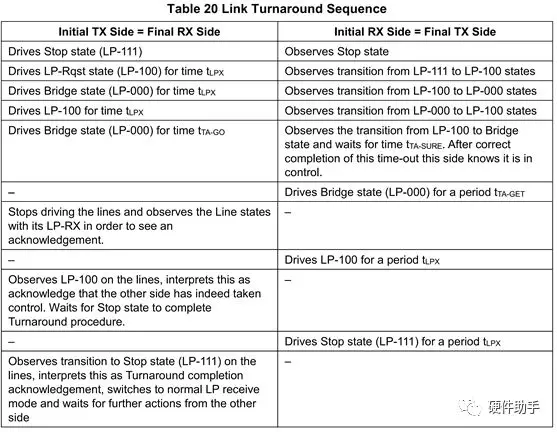

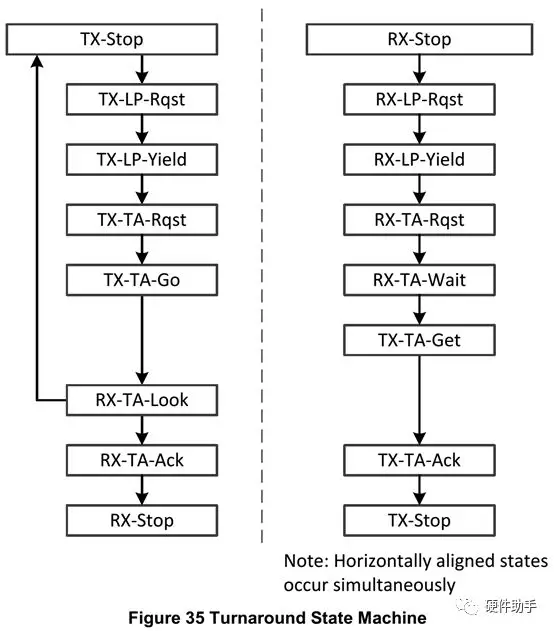

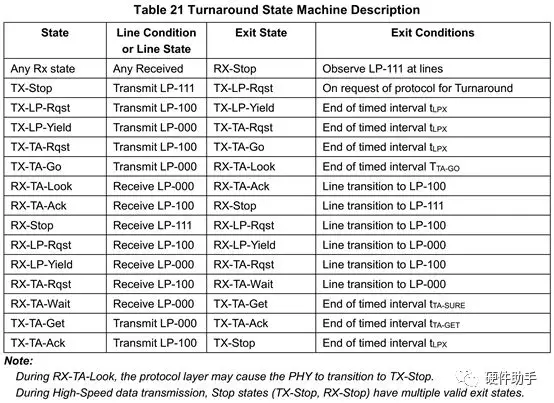

Turnaround的流程如下所示:

-

當通道沒有進入TX-LP-Yield之前,如果通道上有STOP狀態出現,反轉過程可以被打斷,當Lan已經進入TX-LP-Yield,通道已經完成了反轉,此時再有STOP狀態也不能打斷turnaround過程。PHY應該保證在TX-TA-Rqst,RX-TA-Rqst, or TX-TA-GO結束之后,程序不會中斷。

-

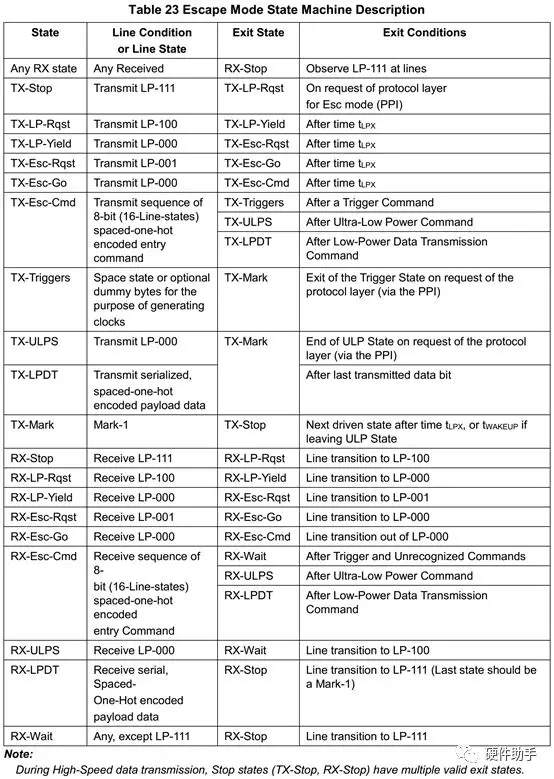

3.4、Escape Mode

-

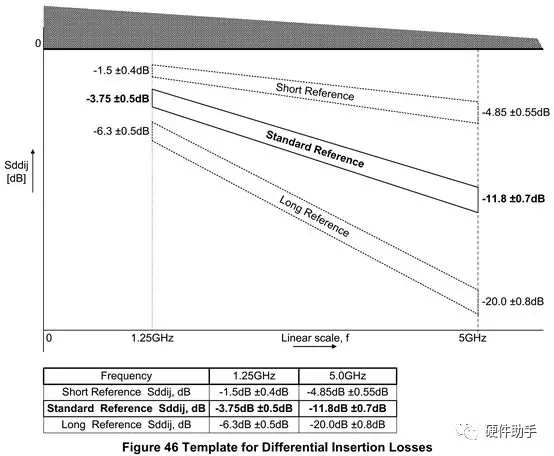

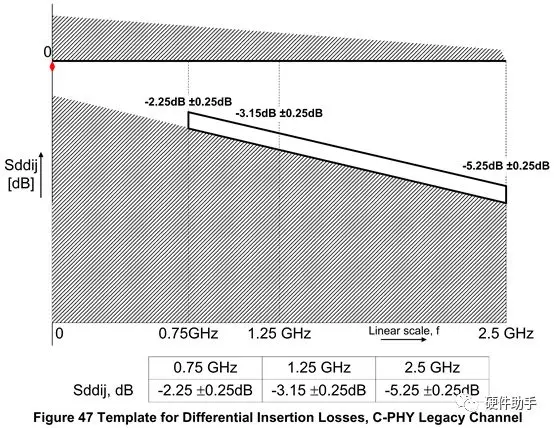

其中差分回損(RL)要求為:在整個工作頻率范圍內Sdd11和Sdd22均小于-12dB。

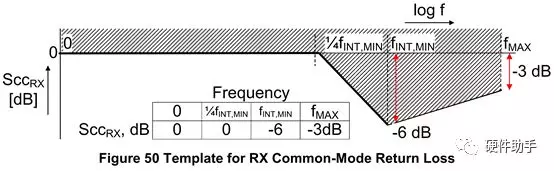

共模插損(IL)的要求和差分插損一樣,共模回損(RL)要求在2*fh(the highest fundamentalfrequency for data transmission)頻率內Scc11和Scc22均小于-12dB。

差分對用作單端想信號線時,其線間耦合參數通過S參數Scc21和Sdd21(或者Scc12和Sdd12)之間的差值來約束,在10*fLP,MAX(the maximum togglefrequency for low-power mode)頻率范圍內不能超過-20dB。

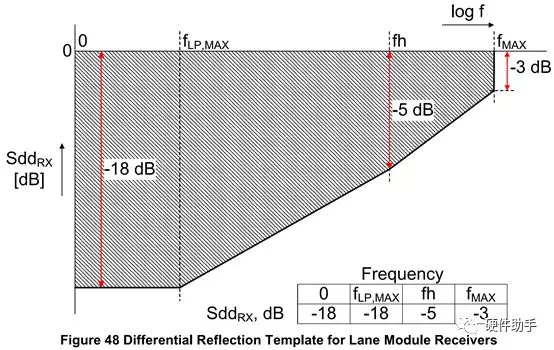

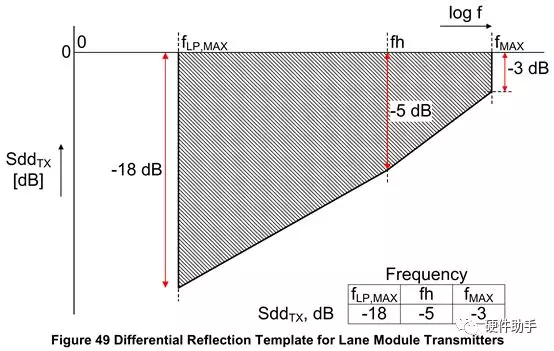

驅動端和接收端的差分回損參數要求如下:

-

HS-TX的回損要求從fLP,MAX到fMAX頻率范圍內不大于-3dB,HS-RX的回損要求如下圖所示:

-

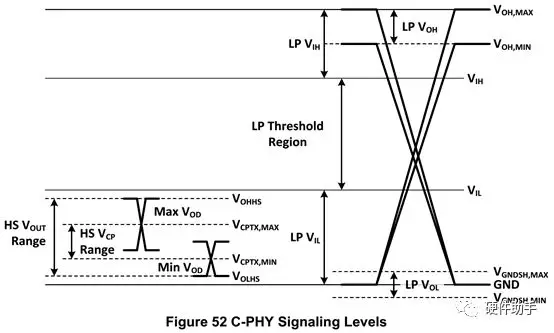

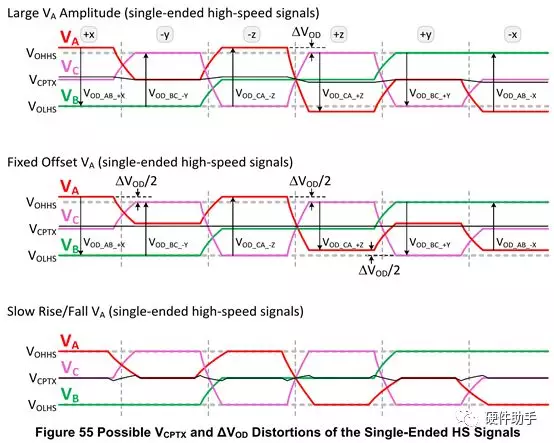

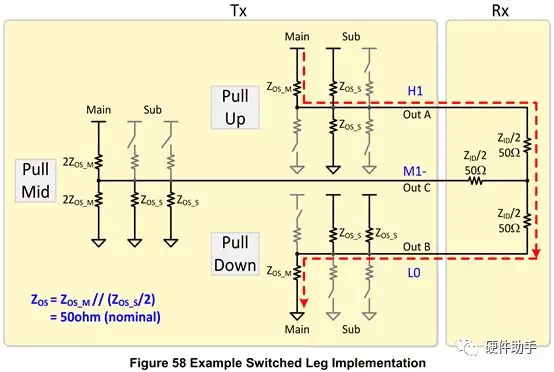

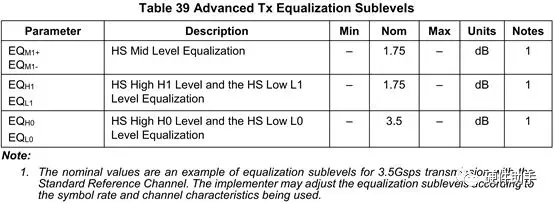

5、電氣特性

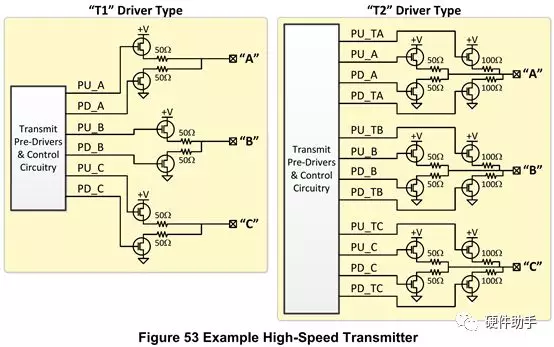

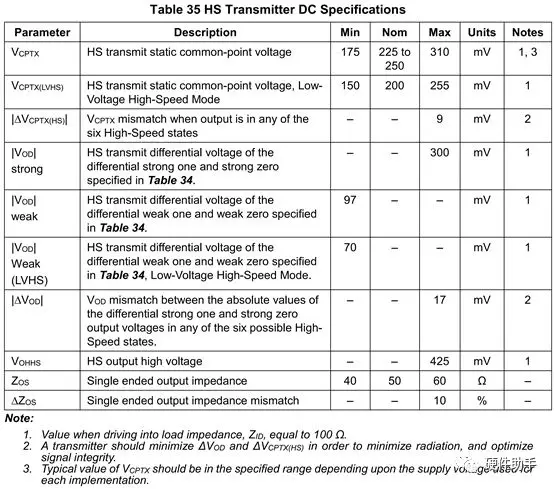

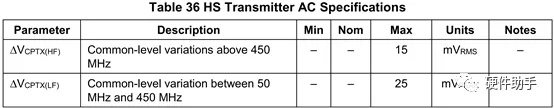

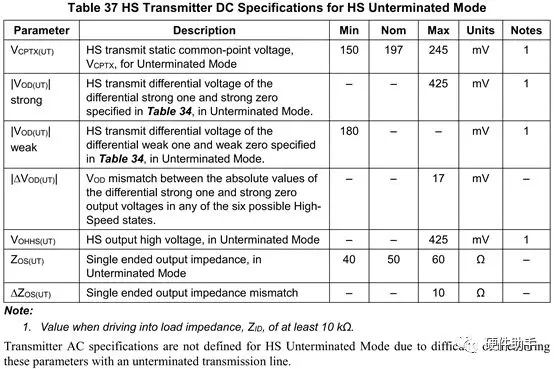

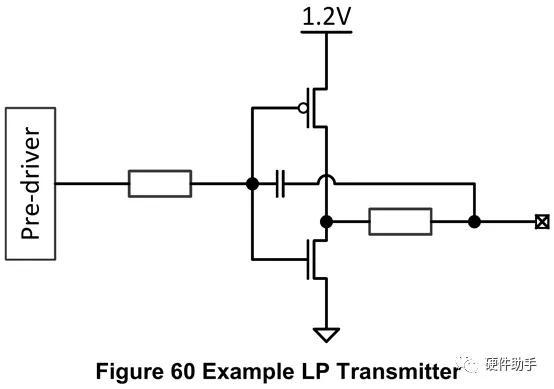

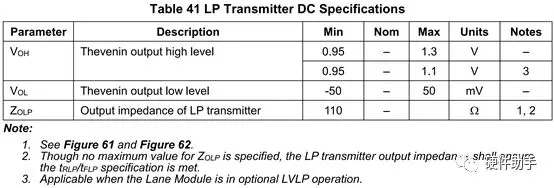

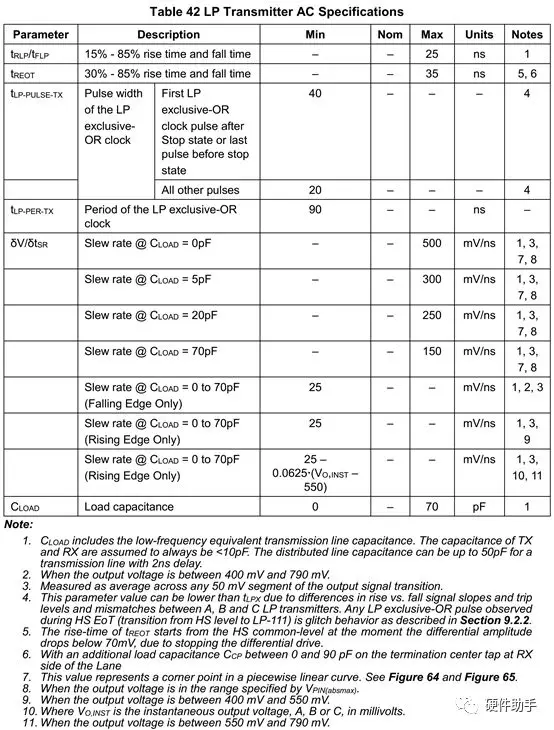

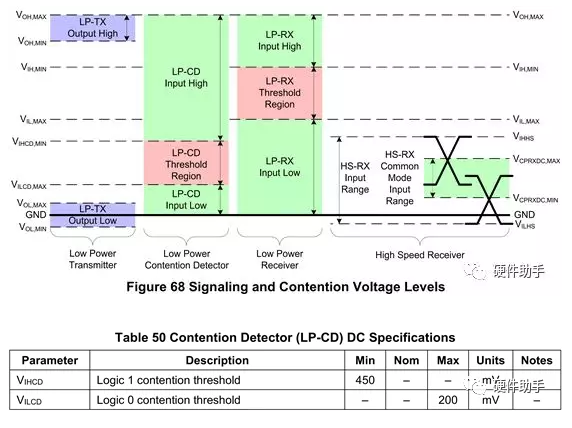

5.1、驅動端電氣特性

-

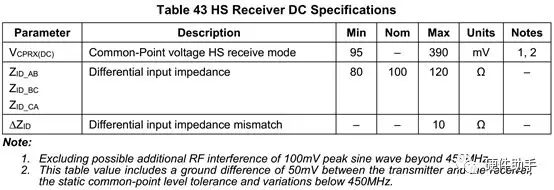

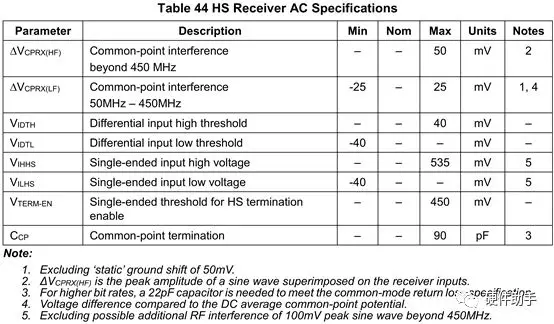

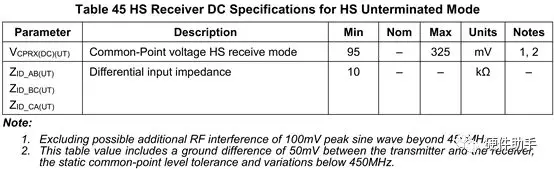

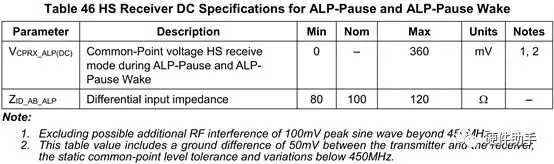

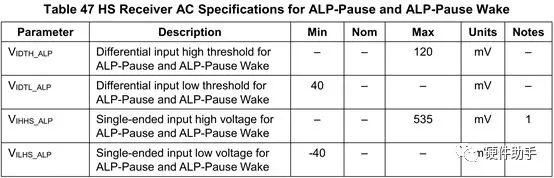

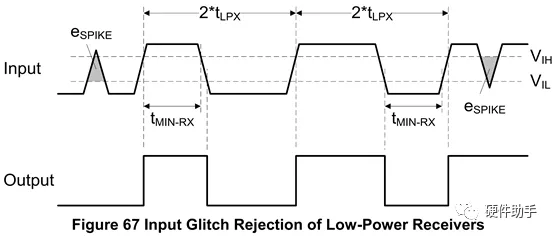

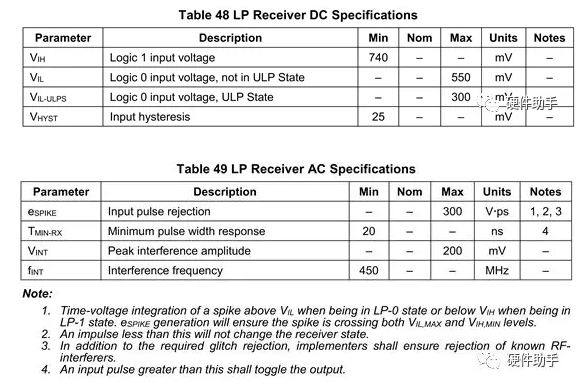

5.2、接收端的電氣特性

-

以上就是針對C-PHY的硬件架構、三相符號編碼、操作模式、模式轉換、電氣特性等的簡單介紹,規范中還對高速信號時序及眼圖模板、內置測試電路等進行了詳細介紹,涉及到相關內容可參看規范《MIPI C-PHY? v1.2, 28-Mar-2017》。其操作模式及模式轉換部分和D-PHY非常相似,也可以參考D-PHY相關資料。

編輯:hfy

-

編碼技術

+關注

關注

1文章

35瀏覽量

11087 -

D-PHY

+關注

關注

1文章

7瀏覽量

25626 -

車載信息娛樂系統

+關注

關注

1文章

66瀏覽量

19849

發布評論請先 登錄

相關推薦

D3 Embedded推出基于Valens VA7000 MIPI A-PHY芯片組的攝像頭模組

使用C2000 EtherCAT從站控制器的SMI進行以太網PHY配置

Capture Symbol 檔名長度

聚焦MIPI 系列之四:一文盤點D-PHY/C-PHY/M-PHY之架構與測試解決方案

求助,關于ESP32C3 RMT紅外編碼器3bit數據編碼問題求解

M31攜手臺積電5奈米先進制程 成功發表MIPI C/D PHY Combo IP

具有NVM和PMBus? 的TPS53681雙通道(6-Phase + 2-Phase) or (5-Phase + 3-Phase) D-CAP+? 降壓多相控制器數據表

NuLink PHY技術:突破計算芯片內存瓶頸

如何快速理解PHY芯片

Teledyne LeCroy擴展CrossSync PHY技術到PCI Express 6.0

一文詳解以太網MAC芯片與PHY芯片

基于3-Phase symbol編碼技術的C-PHY詳解

基于3-Phase symbol編碼技術的C-PHY詳解

評論