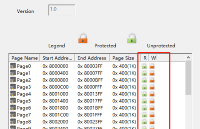

-flatten_hierarchy

full: 綜合時(shí)將原始設(shè)計(jì)打平,只保留頂層層次,執(zhí)行邊界優(yōu)化

none: 綜合時(shí)完全保留原始設(shè)計(jì)層次,不執(zhí)行邊界優(yōu)化

rebuilt: 綜合時(shí)將原始設(shè)計(jì)打平,執(zhí)行邊界優(yōu)化,綜合后將網(wǎng)表文件按照原始層次顯示,故與原始層次相似。

當(dāng)-flatten_hierarchy為none時(shí)消耗的寄存器最多,建議其設(shè)定為默認(rèn)值rebuilt。

用于設(shè)定狀態(tài)機(jī)的編碼方式,默認(rèn)值為auto。

-fsm_encoding

功能同上,優(yōu)先級(jí)高于-fsm_extraction,但如果代碼本身已經(jīng)定義了編碼方式,該設(shè)定將無(wú)效。

one-hot:任意狀態(tài)只有一個(gè)比特位置一。

-keep_equivalent_registers

equivalent registers,等效寄存器,即共享輸入數(shù)據(jù)的寄存器。

勾選時(shí),等效寄存器不合并;

不勾選時(shí),等效寄存器合并。

等效寄存器可以有效的降低扇出,可以通過(guò)綜合屬性keep避免其被合并。

-resource_sharing

其目的是對(duì)算術(shù)運(yùn)算通過(guò)資源共享優(yōu)化設(shè)計(jì)資源

auto

on

off

-control_set_opt_threshold

觸發(fā)器的控制集由時(shí)鐘信號(hào)、復(fù)位/置位信號(hào)和使能信號(hào)構(gòu)成,通常只有{clk,set/rst,ce}均相同的觸發(fā)器才可以被放置在一個(gè)SLICE中。

control_set_opt_threshold的值為控制信號(hào)(不包括時(shí)鐘和數(shù)據(jù))的扇出個(gè)數(shù),表明對(duì)小于此值的同步信號(hào)進(jìn)行優(yōu)化,顯然此值越大,被優(yōu)化的觸發(fā)器越多,但占用的查找表也越多。

control_set_opt_threshold的值為0,不進(jìn)行優(yōu)化。

auto:默認(rèn)值。

-no_lc

對(duì)于一個(gè)x輸入布爾表達(dá)式和一個(gè)y輸入的布爾表達(dá)式,只要滿足x + y ≤5(相同變量只算一次),這兩個(gè)布爾表達(dá)式就可以放置在一個(gè)LUT6中實(shí)現(xiàn)。

當(dāng)-no_lc被勾選時(shí),則不允許出現(xiàn)LUT整合。

通過(guò)LUT整合可以降低LUT的資源消耗率,但也可能導(dǎo)致布線擁塞。因此,xilinx建議,當(dāng)整合的LUT超過(guò)了LUT總量的15%時(shí),應(yīng)考慮勾選-no_lc,關(guān)掉LUT整合。

-shreg_min_size

shreg_min_size決定了當(dāng)VHDL代碼描述的移位寄存器深度大于此設(shè)定值時(shí),將采用“觸發(fā)器+SRL+觸發(fā)器”的方式實(shí)現(xiàn)。

編輯:hfy

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121172 -

vhdl

+關(guān)注

關(guān)注

30文章

817瀏覽量

128343 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

164瀏覽量

48021 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66890

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Vivado之實(shí)現(xiàn)布局布線流程介紹

U50的AMD Vivado Design Tool flow設(shè)置

每次Vivado編譯的結(jié)果都一樣嗎

洛杉磯共享主機(jī)怎么設(shè)置

淺談Vivado編譯時(shí)間

【GD32 MCU 入門教程】六、GD32 MCU 選項(xiàng)字節(jié)設(shè)置及解除方法

Vivado編譯常見(jiàn)錯(cuò)誤與關(guān)鍵警告梳理與解析

詳解Vivado非工程模式的精細(xì)設(shè)計(jì)過(guò)程

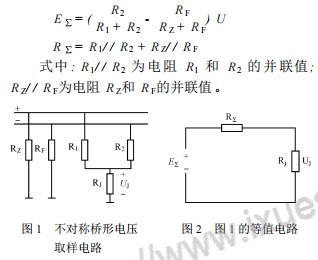

淺談直流絕緣監(jiān)測(cè)及接地點(diǎn)定位綜合裝置的設(shè)計(jì)與應(yīng)用

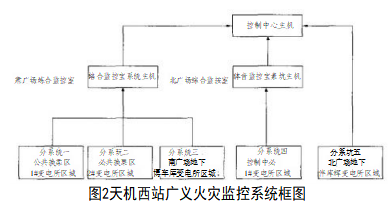

淺談電氣火災(zāi)監(jiān)控系統(tǒng)在天津西站綜合交通樞紐中的應(yīng)用

淺談城市綜合管廊基于物聯(lián)網(wǎng)融合通信系統(tǒng)應(yīng)用分析

淺談綜合管廊監(jiān)控及安防技術(shù)

淺談智能照明控制系統(tǒng)在綜合管廊中的設(shè)計(jì)應(yīng)用與研究

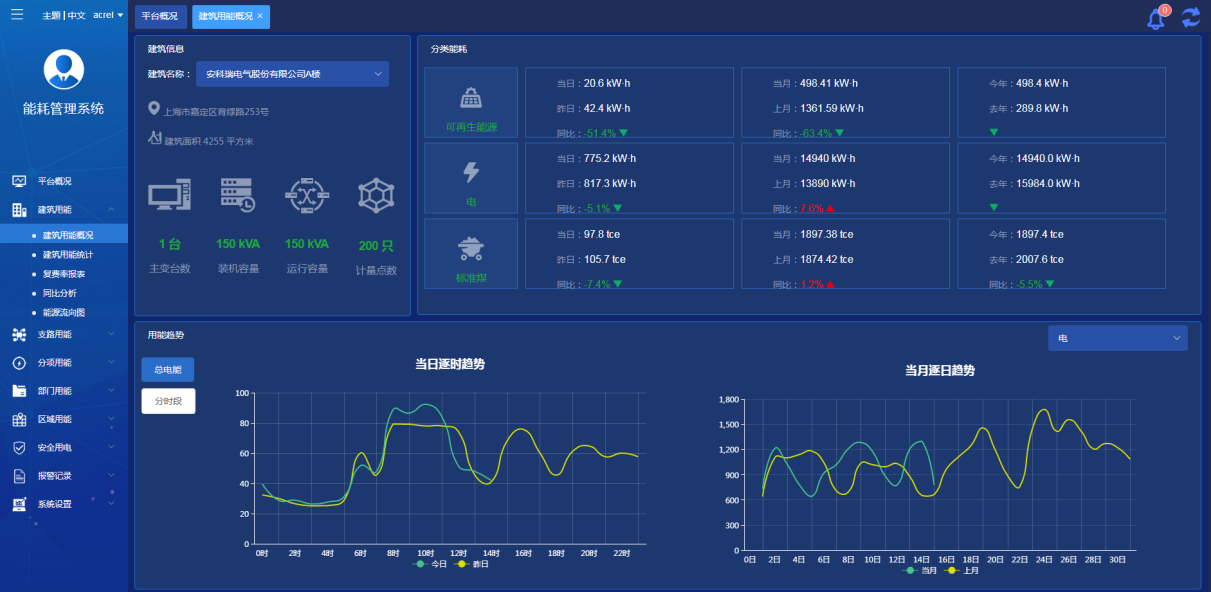

淺談商業(yè)綜合建筑能耗分析及節(jié)能發(fā)展情況

淺談Vivado 綜合選項(xiàng)的7種設(shè)置

淺談Vivado 綜合選項(xiàng)的7種設(shè)置

評(píng)論