背景與問題

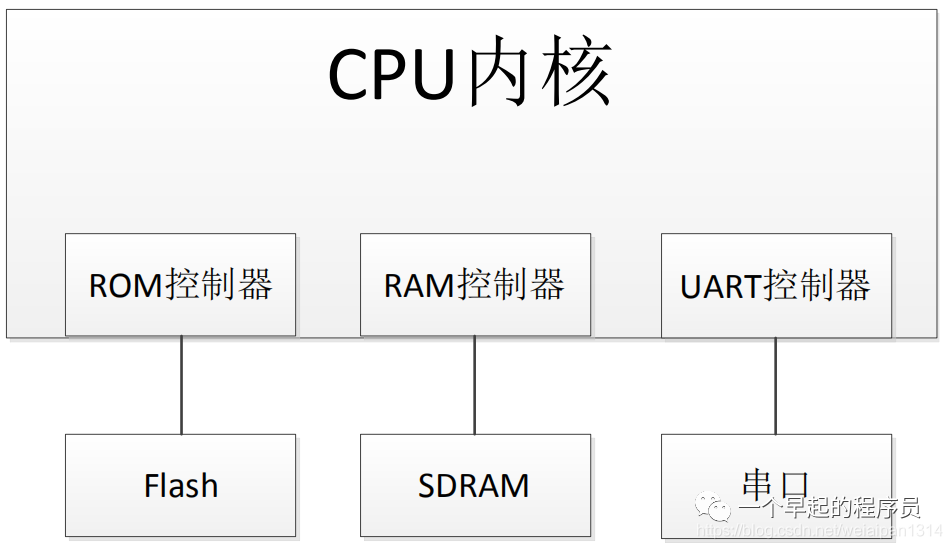

? FPGA邏輯(Vivado ->BD -> Address Editor)中如何設置PCIe to AXI Translation;

? FPGA邏輯中如何設置AXI to PCIe Address Translation。

1. Root Complex到Endpiont

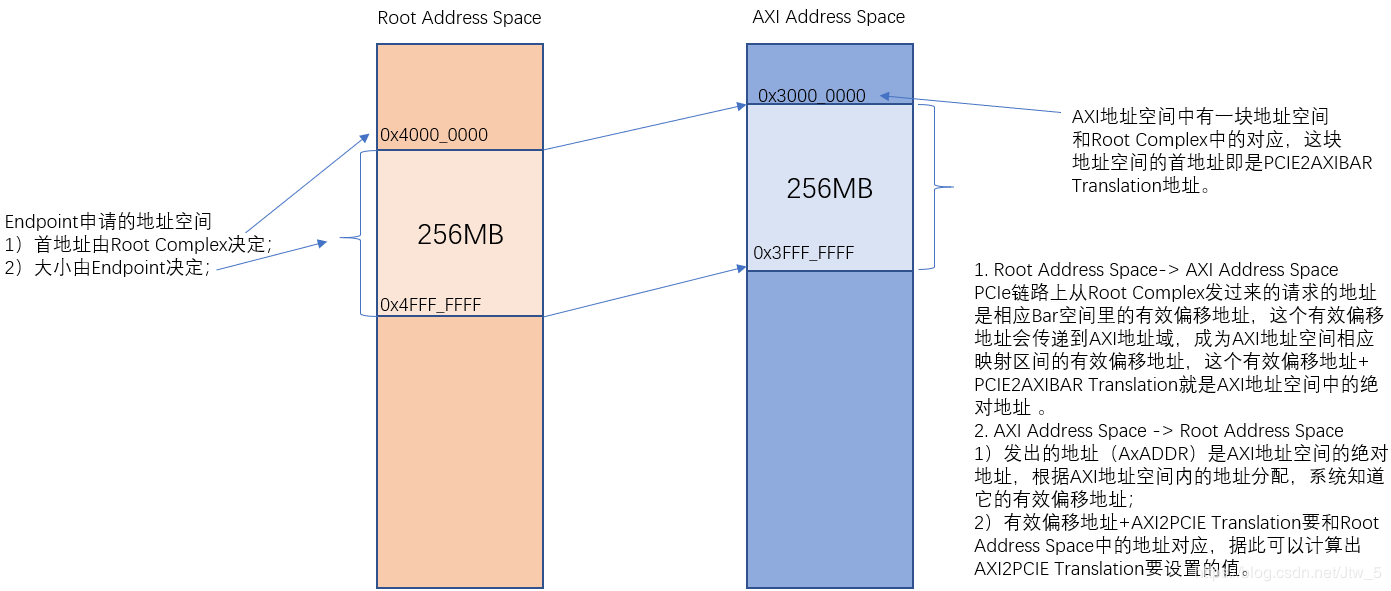

1.1 Root Complex到Endpiont,即PCIe域(Root Complex中的系統地址空間)到AXI域(FPGA邏輯中的AXI地址空間)。PCIe發起的對Endpoint的訪問應在Endpoint申請的BAR空間內,Endpoint申請BAR空間時申明了地址空間的大小(比如256M,而且我們假設這256M空間對應AXI域中0x3000_0000~0x3FFF_FFFF),而Root Complex則根據實際情況決定從某個地址開始分配一段地址空間給Endpoint(比如0x4000_0000~0x4FFF_FFFF)。

1.2 PCIe想對Endpoint中的0x3000_0010地址發起一次訪問。PCIe發出訪問的地址為0x4000_0010,FPGA的PCIe Core會收到相應BAR空間中的有效地址偏移0x10,PCIe Core使用有效地址偏移+ C_PCIEBAR2AXIBAR(根據1.1中的假設,這個值為0x3000_0000)作為其AXI總線訪問的地址。

2. Endpiont到Root Complex

2.1 假設PCIe域和AXI域的映射跟1. Root Complex到Endpiont的設定相同。

2.2 來自映射地址為0x3000_0000~0x3FFF_FFFF的AX總線訪問給出的地址0x3000_1234會被PCIe Core剝離出有效偏移地址0x1234,使用該偏移地址+C_AXIBAR2PCIEBAR作為PCIe TLP的地址發送給Root Complex。C_AXIBAR2PCIEBAR的值應該設為Root Complex給Endpoint分配的地址空間的首地址,即0x4000_0000。

3. 總結與疑問

3.1 總結

? 地址空間的有效偏移地址。

? 地址空間的首地址。

3.2 疑問

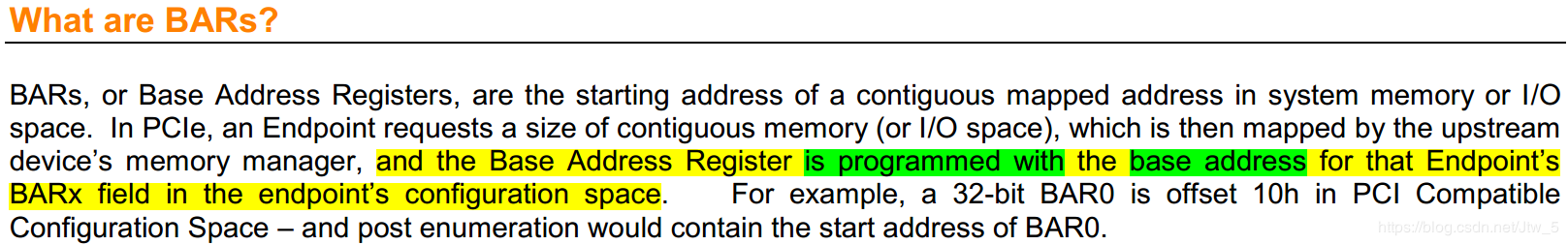

CPU發出的訪問地址到FPGA的PCIe IP是如何被提取出有效偏移地址的? PCIe的配置空間里記錄了CPU分配的BAR空間的首地址?

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606046 -

cpu

+關注

關注

68文章

10905瀏覽量

213031 -

PCIe

+關注

關注

15文章

1262瀏覽量

83195

發布評論請先 登錄

相關推薦

Linux內核地址映射模型與Linux內核高端內存詳解

關于ARM地址映射的理解

hyperlink地址映射方式不對

STM32核心在Cortex的地址映射說明

FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明

2020.4.14 第四次 寄存器地址名稱映射

FPGA邏輯中關于地址映射說明

FPGA邏輯中關于地址映射說明

評論