約束衍生時鐘

系統中有4個衍生時鐘,但其中有兩個是MMCM輸出的,不需要我們手動約束,因此我們只需要對clk_samp和spi_clk進行約束即可。約束如下:

create_generated_clock -name clk_samp -source [get_pins clk_gen_i0/clk_core_i0/clk_tx] -divide_by 32 [get_pins clk_gen_i0/BUFHCE_clk_samp_i0/O] create_generated_clock -name spi_clk -source [get_pins dac_spi_i0/out_ddr_flop_spi_clk_i0/ODDR_inst/C] -divide_by 1 -invert [get_ports spi_clk_pin]

這里需要注意的是,如果該約束中使用get_pins(即產生的時鐘并非輸出到管腳),那么無論是source的時鐘還是我們衍生的時鐘,在get_pins后面的一定是這個時鐘最初的產生位置。在視頻中我們會具體展示)。

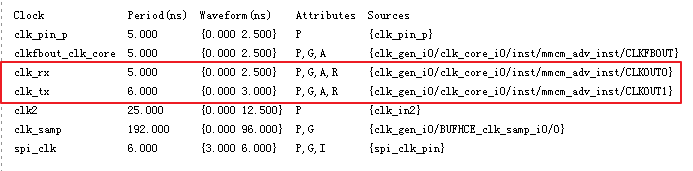

我們再運行report_clocks,顯示如下:

我們在理論篇的“create_generated_clock”一節中講到,我們可以重新設置Vivado自動生成的衍生時鐘的名字,這樣可以更方便我們后續的使用。按照前文所講,只需設置name和source參數即可,其中這個source可以直接從report_clocks中得到,因此我們的約束如下:

create_generated_clock -name clk_tx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT1] create_generated_clock -name clk_rx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT0]

大家可以對比下report_clocks的內容和約束指令,很容易就能看出它們之間的關系。

把上述的約束指令在tcl中運行后,我們再運行一遍report_clocks,顯示如下:

在時序樹的分析中,我們看到,clk_samp和clk2兩個異步時鐘之間存在數據交互,因此要進行約束,如下:

set_clock_groups -asynchronous -group [get_clocks clk_samp] -group [get_clocks clk2]

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605998 -

Vivado

+關注

關注

19文章

815瀏覽量

66887

發布評論請先 登錄

相關推薦

FPGA主時鐘約束詳解 Vivado添加時序約束方法

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA時序約束之建立時間和保持時間

FPGA實戰演練邏輯篇56:VGA驅動接口時序設計之3時鐘約束

FPGA時鐘約束問題

FPGA設計約束技巧之XDC約束之I/O篇(下)

FPGA案例之衍生時鐘約束

FPGA案例之衍生時鐘約束

評論