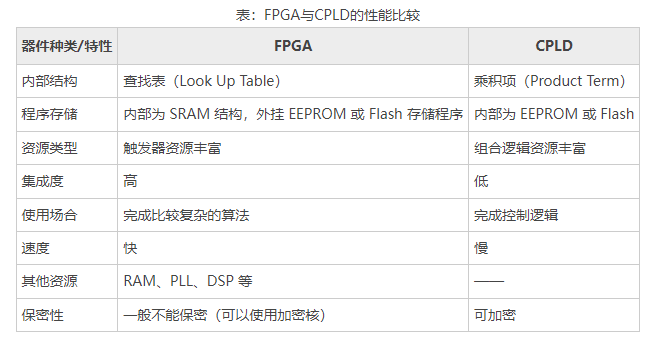

CPLD是復雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field Programable Gate Array)的簡稱,兩者的功能基本相同,編程等過程也基本相同(燒寫文件不一樣,但是是由軟件自動產生的),只是芯片內部的實現原理和結構略有不同。

CPLD

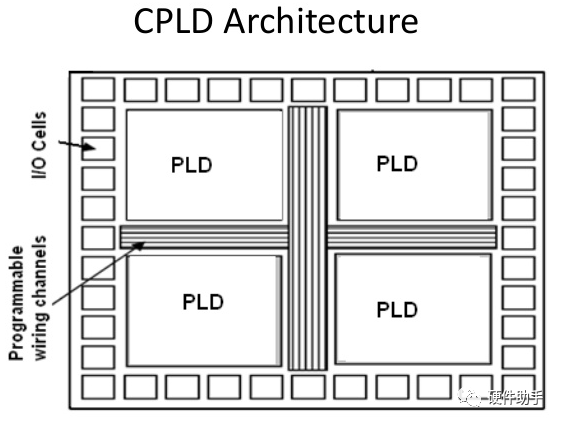

CPLD主要由可編程I/O單元、基本邏輯單元、布線池和其他輔助功能模塊構成。

可編程邏輯單元

作用與FPGA的基本I/O口相同,但是CPLD應用范圍局限性較大,I/O的性能和復雜度與FPGA相比有一定的差距,支撐的I/O標準較少,頻率也較低。

基本邏輯單元

CPLD中基本邏輯單元是宏單元。所謂宏單元就是由一些與、或陣列加上觸發器構成的,其中“與或”陣列完成組合邏輯功能,觸發器用以完成時序邏輯。 與CPLD基本邏輯單元相關的另外一個重要概念是乘積項。所謂乘積項就是宏單元中與陣列的輸出,其數量標志了CPLD容量。乘積項陣列實際上就是一個“與或”陣列,每一個交叉點都是一個可編程熔絲,如果導通就是實現“與”邏輯,在“與”陣列后一般還有一個“或”陣列,用以完成最小邏輯表達式中的“或”關系。

布線池、布線矩陣

CPLD中的布線資源比FPGA的要簡單的多,布線資源也相對有限,一般采用集中式布線池結構。所謂布線池,其本質就是一個開關矩陣,通過打結點可以完成不同宏單元的輸入與輸出項之間的連接。由于CPLD器件內部互連資源比較缺乏,所以在某些情況下器件布線時會遇到一定的困難。由于CPLD的布線池結構固定,所以CPLD的輸入管腳到輸出管腳的延時固定,被稱為Pin to Pin延時,用Tpd表示,Tpd延時反映了CPLD器件可以實現的最高頻率,也就清晰地表明了CPLD器件的速度等級。

FPGA

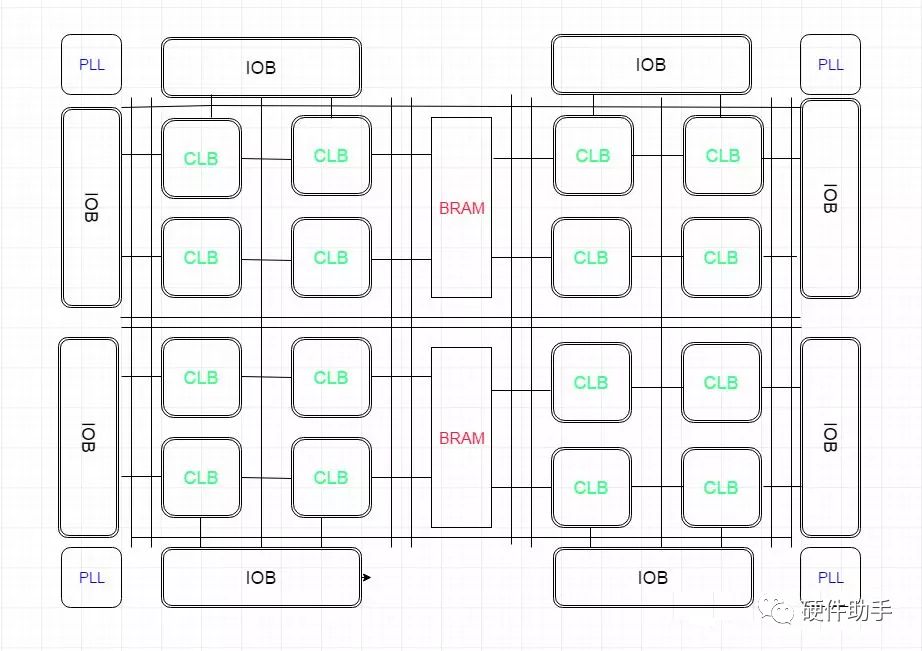

FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內嵌專用硬核等。

可編程輸入/輸出單元(IOB)

可編程輸入/輸出單元是芯片與外界電路的接口部分,完成不同電氣特性下對輸入/輸出信號的驅動與匹配要求。FPGA內部的I/O按組分類,每組都能夠獨立地支持不同的I/O標準。通過軟件的靈活配置,可適應不同的電氣標準與I/O物理特性,可以調整匹配阻抗特性,可以改變上、下拉電阻,可以調整驅動電流的大小。 外部輸入信號可以通過IOB模塊的存儲單元輸入到FPGA的內部,也可以直接輸入FPGA內部。當外部輸入信號經過IOB模塊的存儲單元輸入到FPGA內部時,其保持時間(Hold Time)的要求可以降低,通常默認為0。 為了便于管理和適應多種電器標準,FPGA的IOB被劃分為若干個組(bank),每個bank的接口標準由其接口電壓VCCO決定,一個bank只能有一種VCCO,但不同bank的VCCO可以不同。只有相同電氣標準的端口才能連接在一起,VCCO電壓相同是接口標準的基本條件。

基本可編程邏輯單元

FPGA的基本可編程邏輯單元是由查找表(LUT)和寄存器(Register)組成的,查找表完成純組合邏輯功能。FPGA內部寄存器可配置為帶同步/異步復位和置位、時鐘使能的觸發器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設計。一般來說,比較經典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內部結構有一定的差異,而且寄存器和查找表的組合模式也不同。 了解底層配置單元的LUT和Register比率的一個重要意義在于器件選型和規模估算。由于FPGA內部除了基本可編程邏輯單元外,還有嵌入式的RAM、PLL或DLL,專用的Hard IP Core等,這些模塊也能等效出一定規模的系統門,所以簡單科學的方法是用器件的Register或LUT的數量衡量。

嵌入式塊RAM

目前大多數FPGA都有內嵌的塊RAM。嵌入式塊RAM可被配置為單端口RAM、雙端口RAM、內容地址存儲器(CAM)以及FIFO等常用存儲結構。 CAM,即為內容地址存儲器。寫入CAM的數據會和其內部存儲的每一個數據進行比較,并返回與端口數據相同的所有內部數據的地址。簡單的說,RAM是一種寫地址,讀數據的存儲單元;CAM與RAM恰恰相反。 除了塊RAM,Xilinx和Lattice的FPGA還可以靈活地將LUT配置成RAM、ROM、FIFO等存儲結構。

豐富的布線資源

布線資源連通FPGA內部所有單元,連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別:

全局性的專用布線資源:用以完成芯片內部全局時鐘和全局復位/置位的布線;

長線資源:用以完成器件Bank間的一些高速信號和一些第二全局時鐘信號的布線;

短線資源:用來完成基本邏輯單元間的邏輯互連與布線;

其他:在邏輯單元內部還有著各種布線資源和專用時鐘、復位等控制信號線。

由于在設計過程中,往往由布局布線器自動根據輸入的邏輯網表的拓撲結構和約束條件選擇可用的布線資源連通所用的底層單元模塊,所以常常忽略布線資源。其實布線資源的優化與使用和實現結果有直接關系。

底層內嵌功能單元

內嵌功能模塊主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等軟處理核(Soft Core)。現在越來越豐富的內嵌功能單元,使得單片FPGA成為了系統級的設計工具,使其具備了軟硬件聯合設計的能力,逐步向SOC平臺過渡。 DLL和PLL具有類似的功能,可以完成時鐘高精度、低抖動的倍頻和分頻,以及占空比調整和移相等功能。Xilinx公司生產的芯片上集成了DLL,Altera公司的芯片集成了PLL,Lattice公司的新型芯片上同時集成了PLL和DLL。PLL和DLL可以通過IP核生成的工具方便地進行管理和配置。

內嵌專用硬核

與“底層嵌入單元”是有區別的,這里指的硬核主要是那些通用性相對較弱,不是所有FPGA器件都包含的硬核。 內嵌專用硬核是相對底層嵌入的軟核而言的,指FPGA處理能力強大的硬核(Hard Core),等效于ASIC電路。為了提高FPGA性能,芯片生產商在芯片內部集成了一些專用的硬核。例如:為了提高FPGA的乘法速度,主流的FPGA中都集成了專用乘法器;為了適用通信總線與接口標準,很多高端的FPGA內部都集成了串并收發器(SERDES),可以達到數十Gbps的收發速度。 Xilinx公司的高端產品不僅集成了ARM,還內嵌了DSP Core模塊,并提出MPSoC、RFSoC等概念。

原文標題:FPGA系列之“CPLD和FPGA的基本結構”

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605991 -

cpld

+關注

關注

32文章

1257瀏覽量

169633

原文標題:FPGA系列之“CPLD和FPGA的基本結構”

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CPLD 在汽車電子中的應用

如何優化 CPLD 性能

常見 CPLD 故障排除方法

CPLD 優勢與劣勢分析

CPLD 在嵌入式系統中的應用

CPLD 應用場景分析

CPLD 與 FPGA 的區別

詳解FPGA的基本結構

如何將自定義邏輯從FPGA/CPLD遷移到C2000?微控制器

FPGA的配置模式有哪些?具體配置過程是怎樣的?

深入理解 FPGA 的基礎結構

FPGA和CPLD差異分析(FPGA結構圖)

CPLD和FPGA的基本結構

CPLD和FPGA的基本結構

評論