2020 年 9 月 9 日,日本東京訊 - 全球領先的半導體解決方案及內存接口產(chǎn)品供應商瑞薩電子集團今日宣布,面向數(shù)據(jù)中心、服務器和高性能工作站應用推出全新高速、低功耗的DDR5數(shù)據(jù)緩沖器。

在過去幾年中,實時分析、機器學習、HPC、AI及其它對內存和帶寬要求極高的應用飛速發(fā)展,推動了服務器內存帶寬需求的爆炸性增長,而減載雙列直插內存模組(LRDIMM)已成為推動這些應用發(fā)展的內存技術的基石。瑞薩全新兼容JEDEC的DDR5數(shù)據(jù)緩沖器5DB0148可為LRDIMM顯著提升速度并降低延遲。基于瑞薩組件的第一代DDR5 LRDIMM,與運行在3200MT/s的DDR4 LRDIMM相比,帶寬增加35%以上。

瑞薩電子數(shù)據(jù)中心事業(yè)部副總裁Rami Sethi表示:“作為業(yè)界完整的DDR5解決方案供應商,我們與客戶及生態(tài)系統(tǒng)合作伙伴緊密合作,將豐富的內存解決方案產(chǎn)品投入量產(chǎn)。瑞薩DDR5數(shù)據(jù)緩沖器對于LRDIMM、其他類型的高密度模組和多樣化存儲等高性能DRAM解決方案至關重要,使得新一代高性能計算應用成為可能并更加完善。”

瑞薩DDR5數(shù)據(jù)緩沖器通過降低容性負載、數(shù)據(jù)對準和信號恢復技術的組合,使重載通道的系統(tǒng)眼圖最大化。這使具有大量內存通道和插槽以及復雜路由拓撲的服務器主板即使在高密度內存滿載的情況下,也能夠以最高速度運行。此外,DDR5模組定義的改進允許更低的電源電壓(DDR5中為1.1V,DDR4中則為1.2V)、DIMM模組內電壓調節(jié)以及通過使用SPD集線器和現(xiàn)代控制總線通信(如I3C)來實現(xiàn)先進的控制平面架構。

自雙列直插式內存模組問世以來,瑞薩作為業(yè)界資深的內存接口產(chǎn)品供應商,始終致力于完整芯片組解決方案的研發(fā)。作為整體產(chǎn)品家族的一部分,經(jīng)過優(yōu)化的全新瑞薩DDR5數(shù)據(jù)緩沖器5DB0148,可與LRDIMM存儲器模組上的其它瑞薩DDR5組件無縫對接,包括電源管理芯片P8900、寄存時鐘驅動器5RCD0148、SPD集線器SPD5118以及溫度傳感器TS5111,確保部署瑞薩芯片組解決方案的內存供應商獲得完整的互操作性和穩(wěn)定的質量。

責任編輯:gt

-

半導體

+關注

關注

334文章

27719瀏覽量

222707 -

瑞薩電子

+關注

關注

37文章

2876瀏覽量

72415 -

DDR5

+關注

關注

1文章

430瀏覽量

24213

發(fā)布評論請先 登錄

相關推薦

DDR5內存與DDR4內存性能差異

瑞薩電子發(fā)布全新DDR5 MRDIMM內存接口芯片組

DDR5內存的工作原理詳解 DDR5和DDR4的主要區(qū)別

揭秘DDR5的讀寫分離技術奧秘

CAB4A-DDR4寄存器32位1:2命令/地址/控制緩沖器和1:4差分時鐘緩沖器數(shù)據(jù)表

Introspect DDR5/LPDDR5總線協(xié)議分析儀

PCA9518可擴展的5通道雙向緩沖器數(shù)據(jù)表

具有3態(tài)輸出的低功耗雙緩沖器/驅動器SN74AUP2G241數(shù)據(jù)表

低功耗雙施密特觸發(fā)器緩沖器SN74AUP2G17數(shù)據(jù)表

具有3態(tài)輸出的低功耗雙緩沖器/驅動器SN74AUP2G240數(shù)據(jù)表

低功耗三施密特-三格緩沖器SN74AUP3G17數(shù)據(jù)表

具有漏極開路輸出的 SN74AUP2G07低功耗雙路緩沖器/驅動器數(shù)據(jù)表

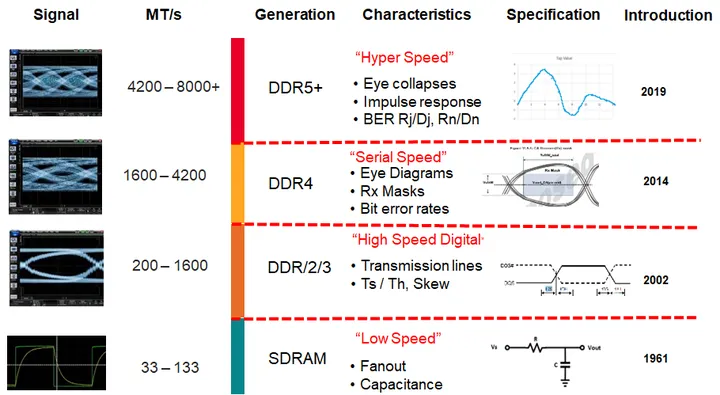

DDR5測試技術更新漫談

瑞薩電子推出采用自研RISC-V CPU內核的通用32位MCU

DDR5內存接口芯片組如何利用DDR5 for DIMM的優(yōu)勢?

瑞薩電子推出低功耗DDR5數(shù)據(jù)緩沖器,可實現(xiàn)先進的控制平面架構

瑞薩電子推出低功耗DDR5數(shù)據(jù)緩沖器,可實現(xiàn)先進的控制平面架構

評論