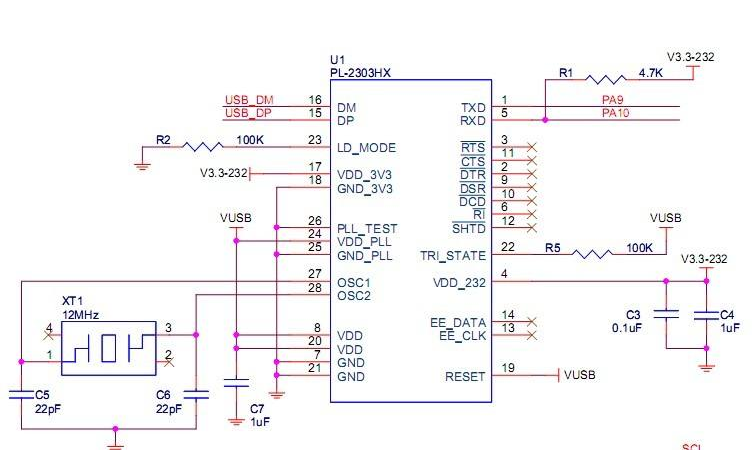

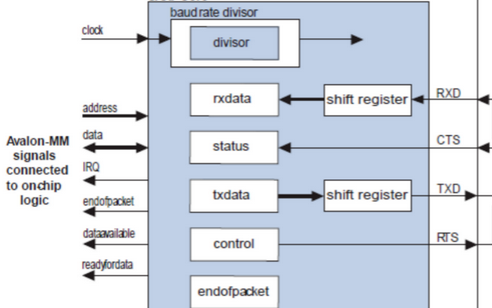

我們在讓Altera FPGA上的嵌入式系統和外部設備進行通信方式的時候,通常會用到擁有Avalon接口的通用異步收發傳輸器——UART IP核。UART核實現了RS-232通訊協議,并使得大家可以設置串口通信相關的波特率、奇偶校驗位、停止位和數據位,以及可選的RTS/CTS流控制信號等參數。

實驗任務

本節實驗是:在Qsys系統中通過使用官方UART IP核和PC進行環回,將收到的字符發送給PC。

硬件設計

創建Quartus II 工程

首先要創建Quartus II工程,工程名為“UART_ip”。

創建Qsys系統

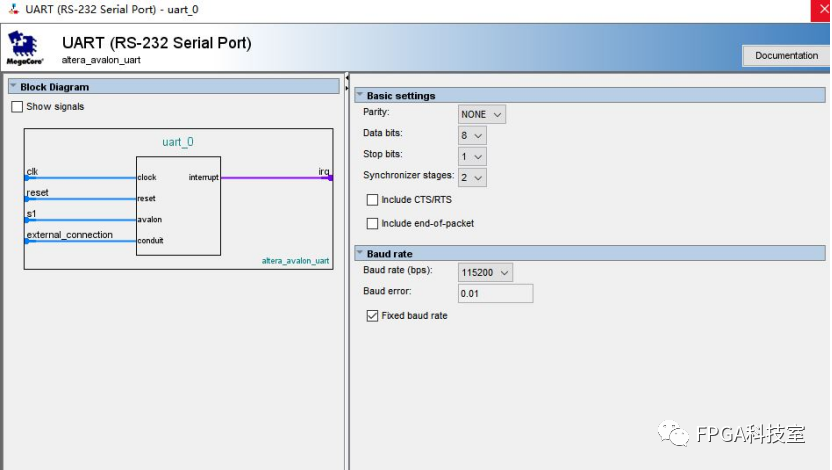

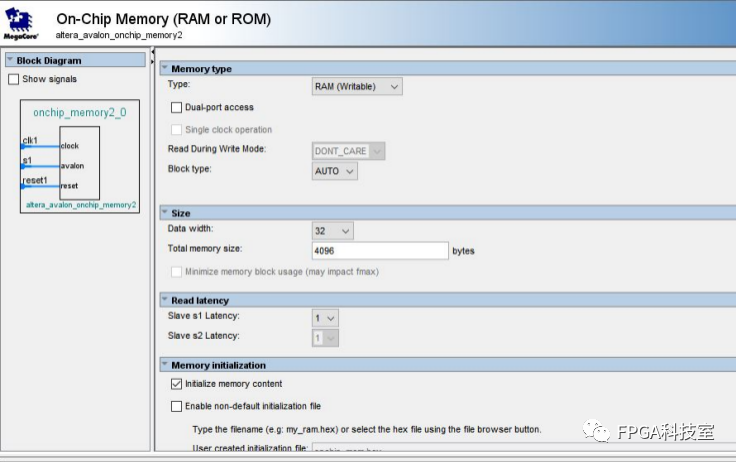

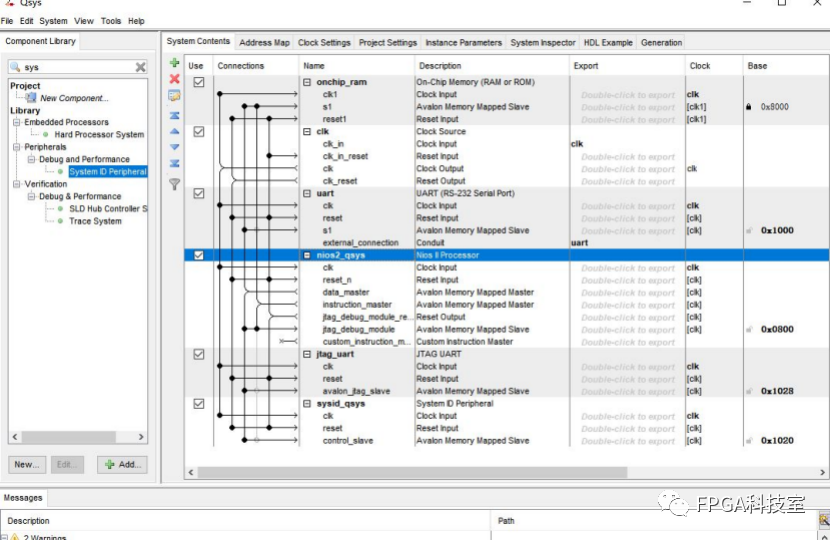

實驗中要用到的IP核有:clk(時鐘)、niosII(處理器)、onchip_ram(片內存儲)、jtag_uart、sysid_qsys、UART。其中只有UART IP核講解一下,其他的IP核都是按照以前的配置方法進行設置,從Library中選擇UART IP核(RS-232 Serial Port)并打開,出現以下界面:

這里我們使用默認設置,直接點擊【Finish】即可。

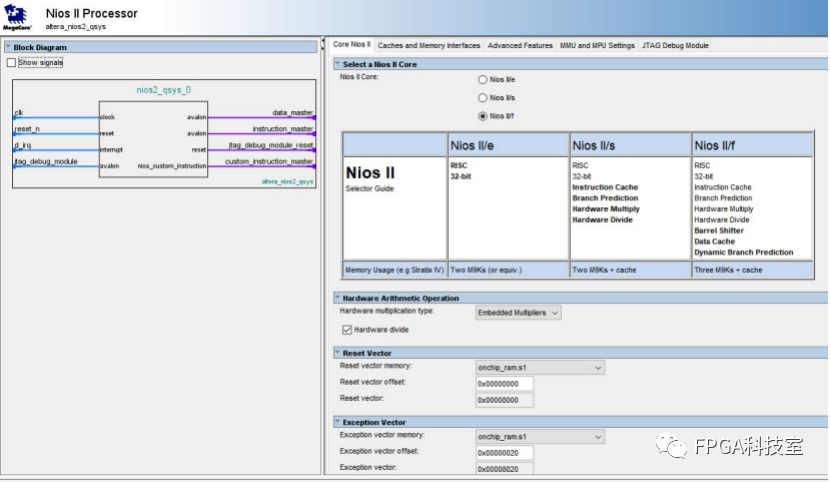

然后,我們打開niosII IP核配置界面,因為這里只用了onchip_ram IP核存儲代碼和指令,所以需要對相關的設置進行修改,在Reset Vector處將Reset vector memory處的選項選為onchip_ram,同時在Exception Vector處也將Exception vector memory處的選項選為onchip_ram。需要注意的是,在系統中加入onchip_ram IP核之后,niosII IP核的Reset Vector和Exception Vector選項中才會出現onchip_ram選項。

添加完IP核后就可以開始連線,大家若是不熟悉怎么連線,可以照著下面完成的Qsys系統界面圖連。需要注意的是,要將UART IP核的端口引出來,引出端口的方法是雙擊IP核的Export一欄,然后修改名稱,按下Enter鍵即可。

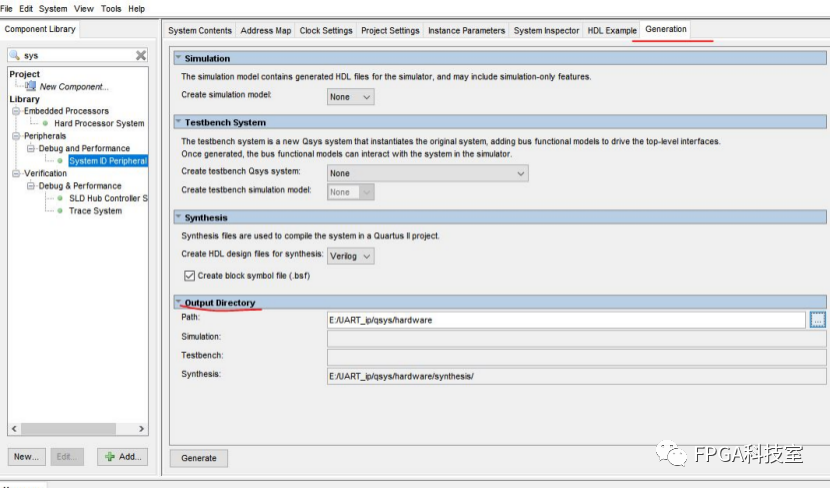

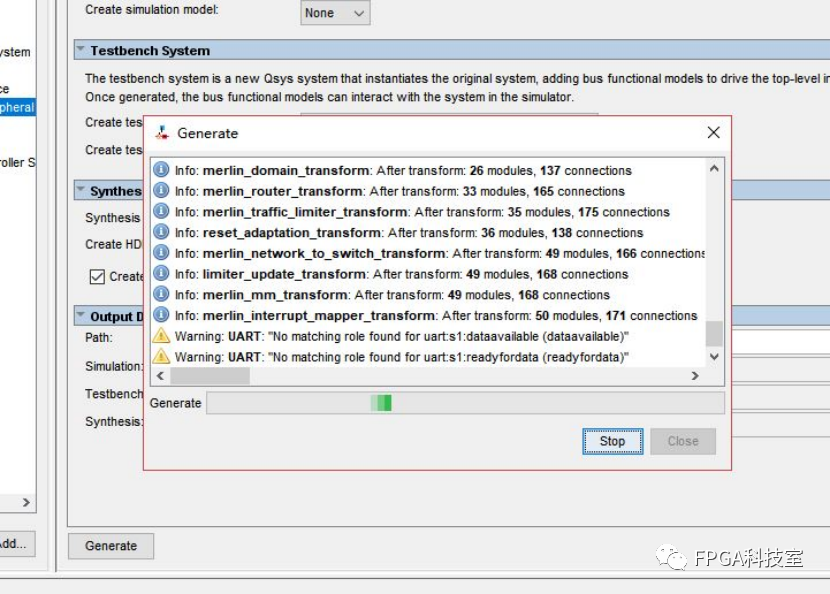

然后,點擊System→Assign Base Addresses 讓系統自動分配地址,這里最好把onchip_ram的地址鎖住,這是因為這個IP 核里存儲著指令,最好不要讓其地址發生變動。鎖住地址的方法是先點擊 IP 核,然后點擊右鍵→Lock Base Address。我們還可以將各個 IP 核的名稱修改一下。最后就是生成系統了,操作可以按照“Hello,World”推送里的進行。

集成Qsys系統

下面兩個圖為集成Qsys關鍵步驟,詳細集成步驟請參考“Hello,World”推送里的操作。

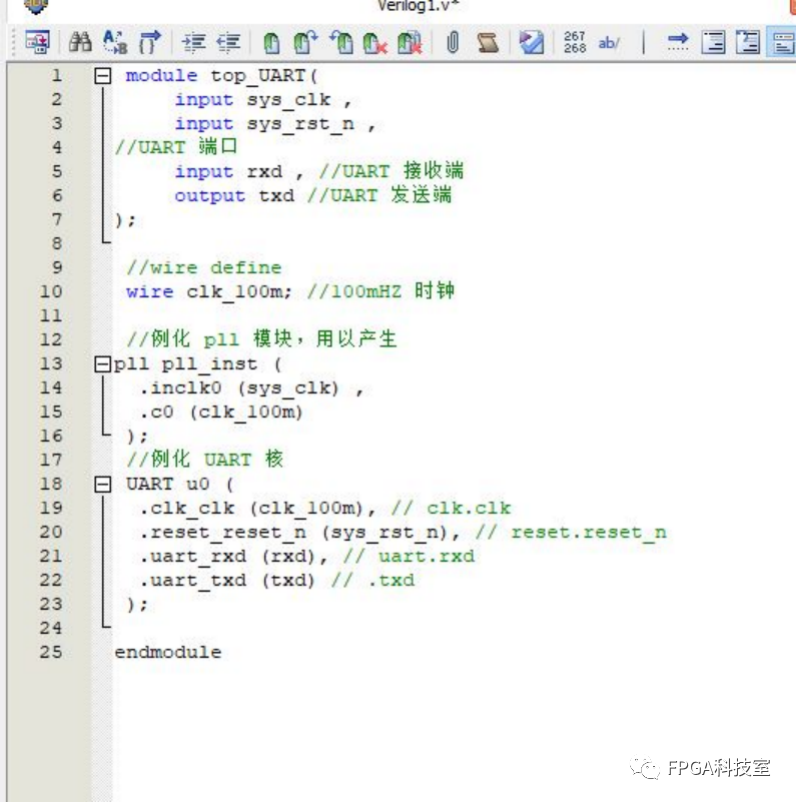

Quartus II工程中的頂層代碼如下。

編譯和下載

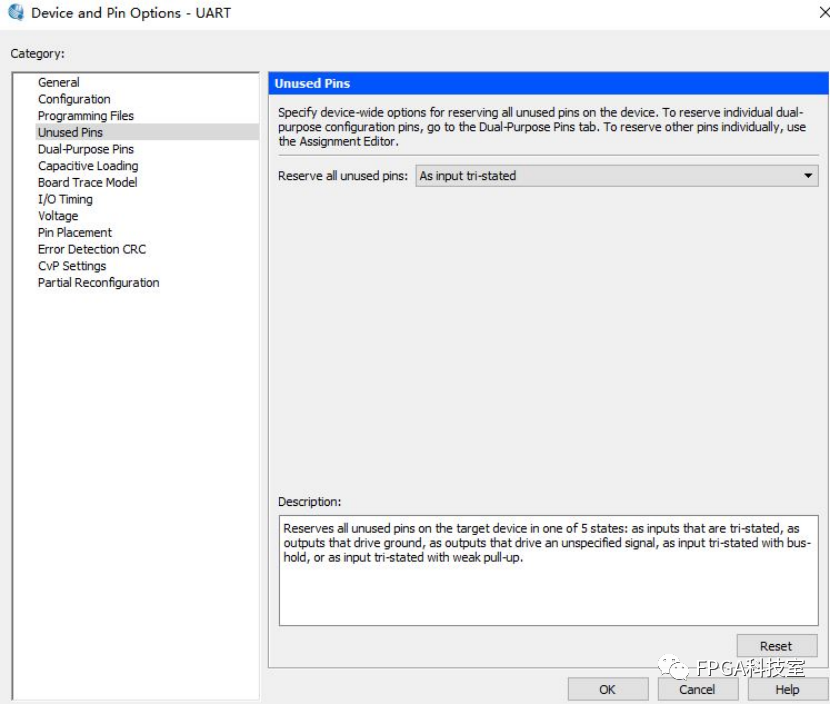

這時,我們便能夠進行編譯查錯了,我們可以通過Quartus II軟件菜單欄中的【Processing】→【Start Compilation】來進行編譯,也可以通過快捷欄中的快捷鍵進行編譯。接下來我們就需要進行配置IO,分配管腳。首先,點擊Quartus II軟件菜單欄中的【Assignment】→【Device】,然后我們在Device界面中找到【Device and Pin Options…】進入頁面配置IO。將未使用引腳設置為高阻輸入(As input tri-state),這樣上電后FPGA的所有不使用引腳都將進入高阻抗狀態。

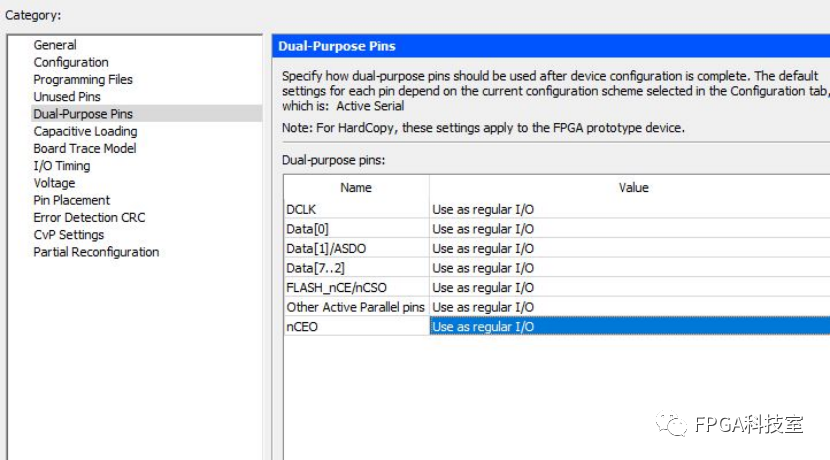

接下來,將一些IO設置成普通IO,通過雙擊紅框位置,將一個個Value的值修改過來。

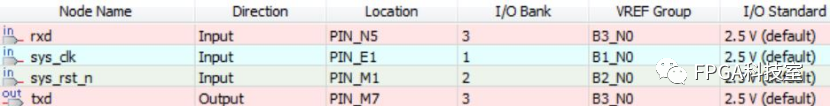

通過Quartus II軟件菜單欄中的【Assignments】→【Pin Planner】選項分配引腳

最后我們再進行一次全編譯,成功編譯硬件系統后,將產生用于配置FPGA的UART_ip.sof文件。下面我們就來說明一下將.sof文件下載到FPGA目標器件的步驟。

將下載器一端連接電腦,另一端與開發板上對應端口連接,最后連接電源線并打開電源開關。接下來我們下載程序。工程打開后通過點擊工具欄中的“Programmer”圖標打開下載界面,通過“Add File”按鈕選擇 output_files 目錄下的“UART_ip.sof”文件。

開發板電源打開后,在程序下載界面點擊“Hardware Setup”,在彈出的對話框中選擇當前 的硬件連接為“USB-Blaster[USB-0]”。然后點擊“Start”將工程編譯完成后得到的 sof 文件下載到開發板中。

至此,硬件部分設計完成,下面開始基于Nios II SBT for Eclipse的軟件部分的設計。

軟件設計

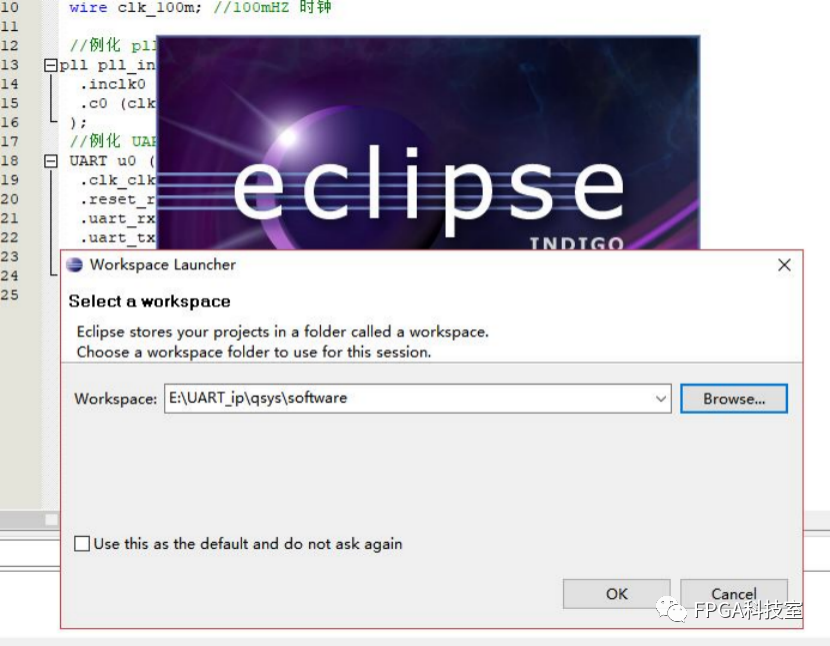

我們通過Quartus II軟件菜單欄中的【Toos】→【Nios II SBT for Eclipse】,來啟動NiosII SBT for Eclipse軟件。打開Nios II SBT for Eclipse軟件后,會彈出Workspace Launcher頁面。我們這里將工作空間設置為qsys路徑下的software文件夾,如圖所示。

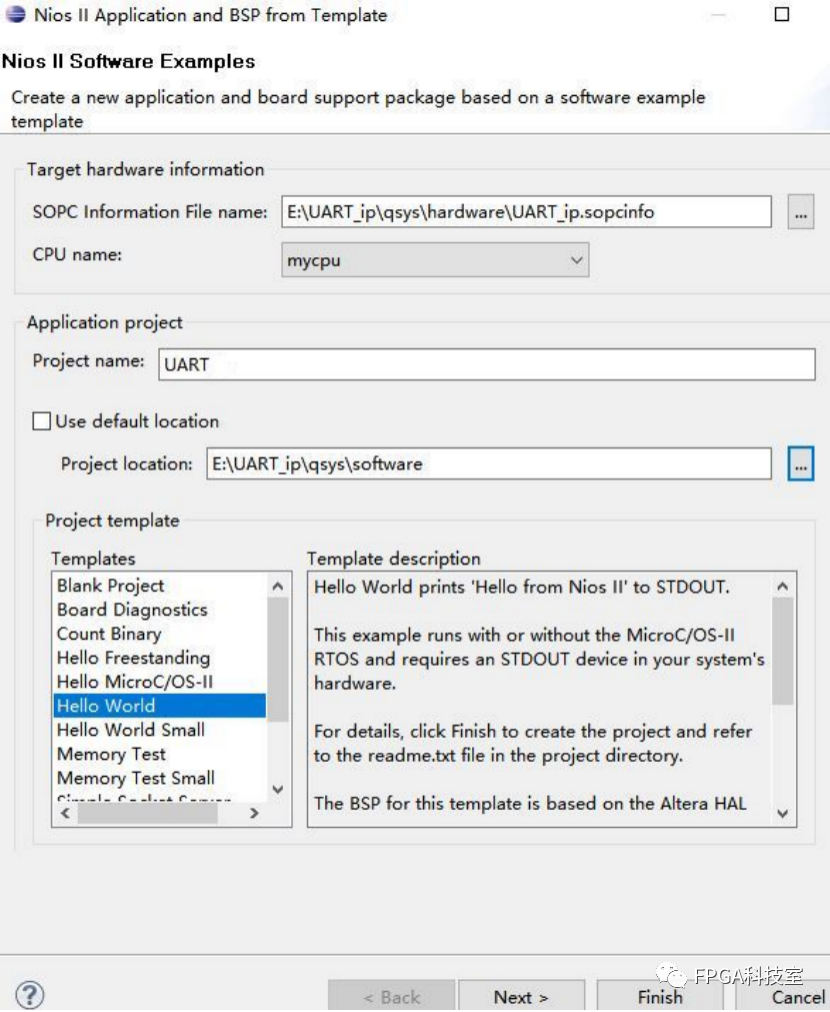

設置好工作空間后,我們點擊【OK】進入Nios II SBT for Eclipse軟件主界面中,在該頁面我們通過單擊菜單欄中的【File】→【New】→【Nios II Application and BSP from Template】,來新建工程。

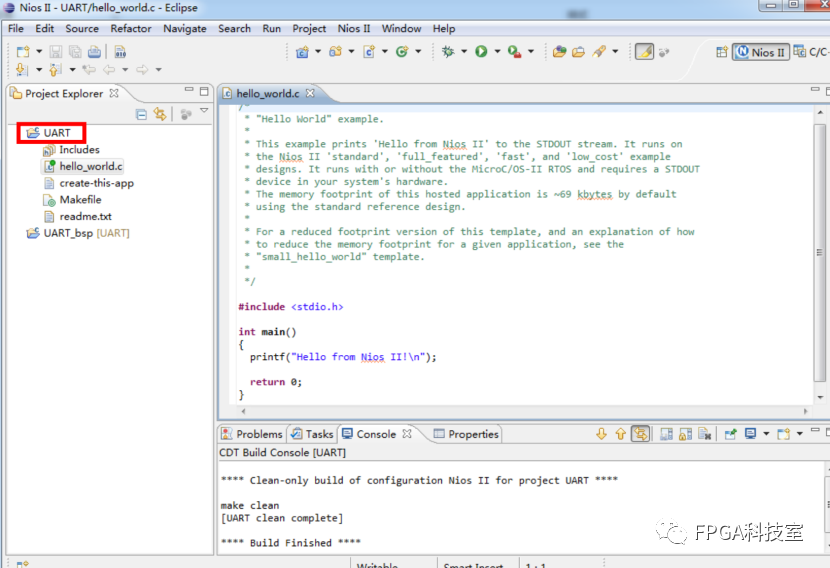

單擊【…】按鈕來選擇qsyshardware下的UART_ip.sopcinfo文件,即指向當前硬件設計系統。Nios II SBT for Eclipse軟件會自動識別Qsys系統中CPU的名稱,所以CPU name一項會自動生成。接下來,要給Nios II SBT for Eclipse軟件中的工程命名,這里的名稱沒有特殊要求,我們這里名為UART。然后將工程存放的位置修改為qsyssoftwareUART。注意不要漏掉了“UART”,不然生成系統的時候會報錯。最后我們來看下Project template窗口,該窗口中陳列的都是已經設計好的軟件工程。我們可以從中選擇一個,作為自己的工程的模板來使用。當然也可以選擇Bland Project(空白工程),就需要自己寫所有的代碼。這里我們選擇的是Hello World模板工程,然后我們在它的基礎上進行修改,這樣比空白工程更加方便。設置完工程后,直接點擊【Finish】完成工程創建。然后,在Nios II SBT for Eclipse軟件的

左側Project Explorer窗口中有兩個工程:UART 和 UART_bsp。其中UART 是C/C++應用工程,而UART_bsp是描述Qsys系統硬件細節的系統庫。打開UART 工程里的 hello_world.c文件。

我們在這里要驗證之前創建的Qsys系統是否能正常工作,驗證方法和“Hello,World”是一樣的。

這時大家點擊【Run As】→【Nios II Hardware】,然后點擊【Target Connection】標簽,然后在Target Connection窗口中點擊【Refresh Connections】按鈕后。這時軟件便會自動識別我們開發板上的Qsys系統,并顯示Qsys系統的相關信息。我們接著點擊【Run】,軟件會把irq.elf文件下載至開發板中運行起來。更加詳細的圖和文字描述,可以在“Hello,World”下載驗證部分查看。

這時,若之前創建的Qsys系統無誤,代碼下載完成后在Nios II console窗口會顯示“Hello from Nios II!”字符,如下圖所示。

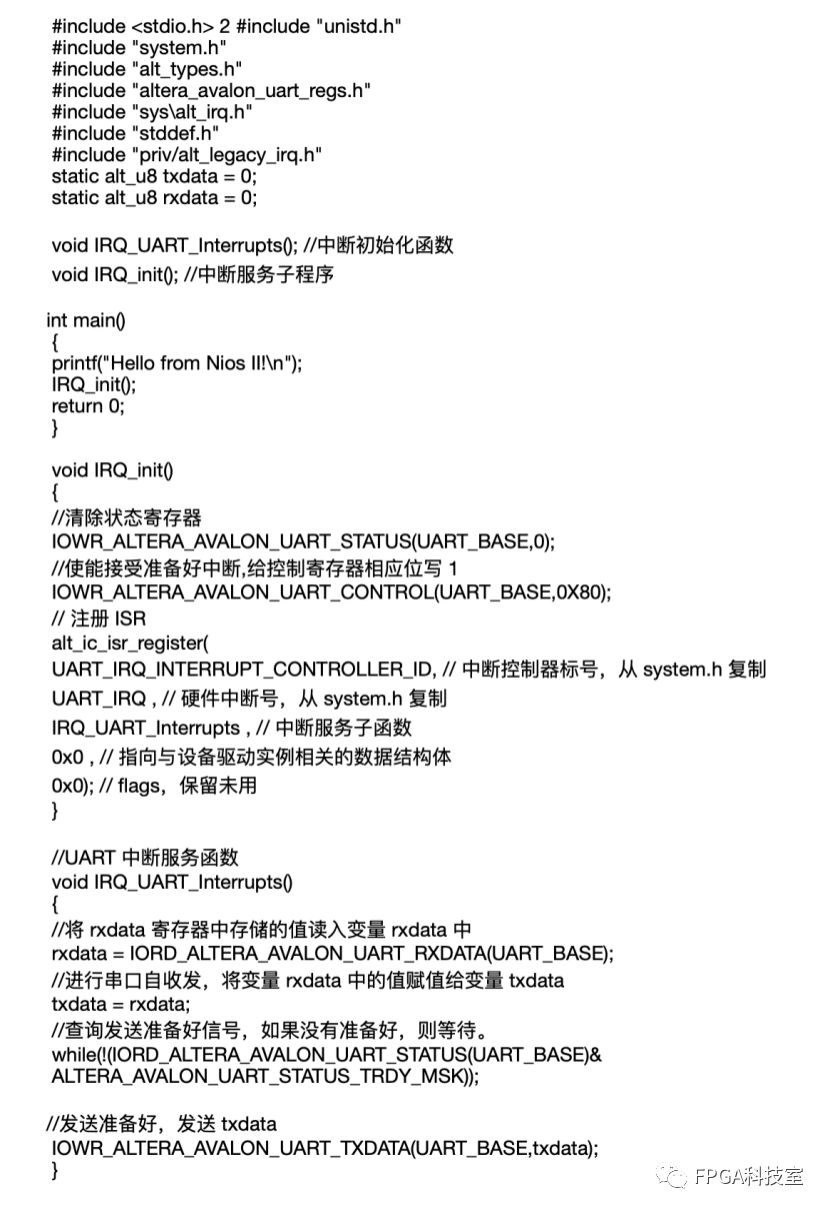

驗證完Qsys系統是否能正常運行之后,我們就可以開始軟件部分的設計了。這時只需要在當前的代碼窗口修改代碼就可以了。

下載驗證

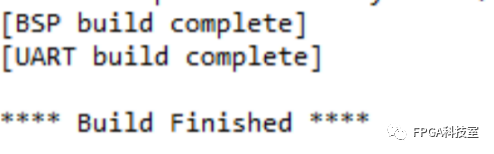

現在可以編譯UART工程了。右鍵UART工程,點擊build project。稍等片刻,Console窗口顯示的內容如下圖所示,這表示工程編譯成功。

右鍵UART工程,點擊【Run As】→【Nios II Hardware】,代碼就被下載到開發板上了。接下來需要連接串口線并利用串口助手進行驗證。

-

寄存器

+關注

關注

31文章

5363瀏覽量

121172 -

中斷

+關注

關注

5文章

900瀏覽量

41753 -

uart

+關注

關注

22文章

1243瀏覽量

101771

原文標題:NIOS II 處理器系統設計之異步收發傳輸UART ip核(應用部分)

文章出處:【微信號:fpgaerZT,微信公眾號:FPGA科技室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

Zynq uart軟件中斷hook的操作過程

ATMEL SAMC21的UART驅動寄存器操作和程序免費下載

使用寄存器的邏輯操作指令是什么?

STM32的寄存器操作

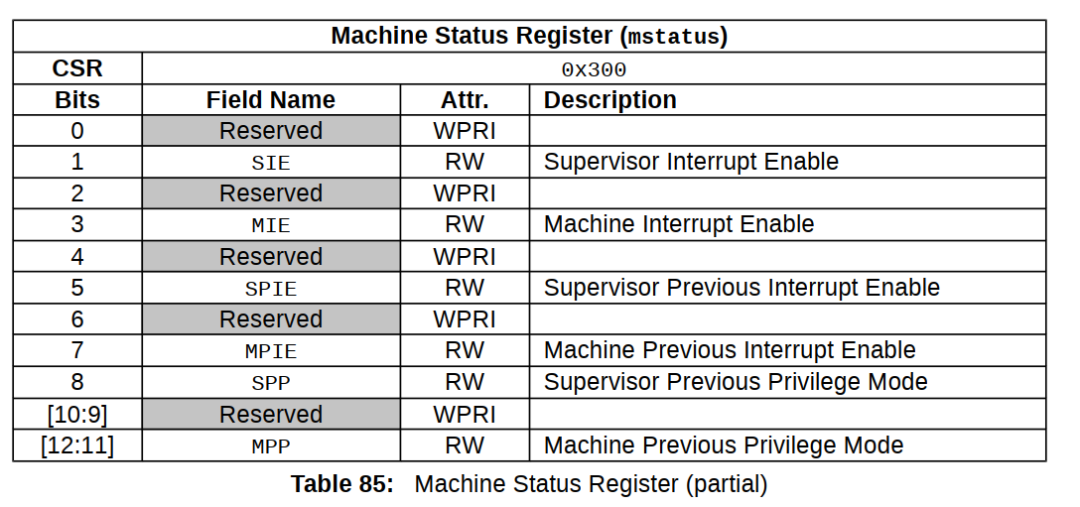

UART寄存器介紹與中斷操作詳解(應用部分)

UART寄存器介紹與中斷操作詳解(應用部分)

評論