有些朋友不理解為什么STM32時鐘要先倍頻N倍,再分頻?你會擔心這個值太大嗎?

1寫在前面

STM32時鐘的功能,可以說是越來越強大了。

從各個系列的時鐘樹可以看得出來,最早F1系列的時鐘功能相對比較簡單,到這后面H7、G0的時鐘越來越豐富。

今天講述一下其中的PLL環節。

2關于PLL

什么是PLL?

PLL:Phase Locked Loop鎖相環。

PLL用于振蕩器中的反饋技術,通常需要外部的輸入信號與內部的振蕩信號同步。

一般的晶振由于工藝與成本原因,做不到很高的頻率,而在需要高頻應用時,由相應的器件VCO,實現轉成高頻,但并不穩定,故利用鎖相環路就可以實現穩定且高頻的時鐘信號。

---來自百度百科

每一塊STM32處理器至少都有一個PLL,有的甚至有好幾個PLL。

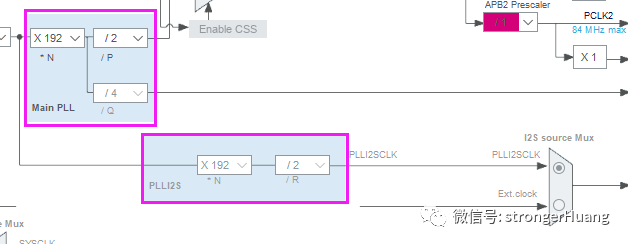

比如,F4有兩個PLL:

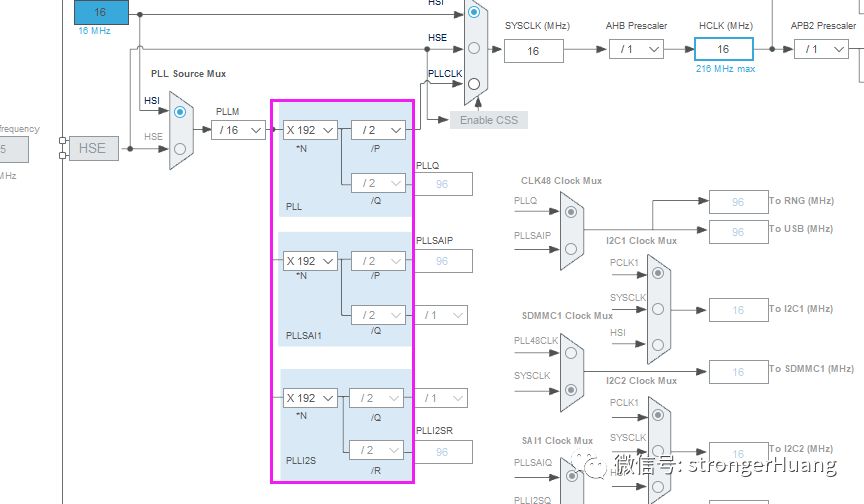

F7有三個PLL:

當然,每個MCU型號不同,其PLL數量,及功能也有差異,具體需要看相應手冊。

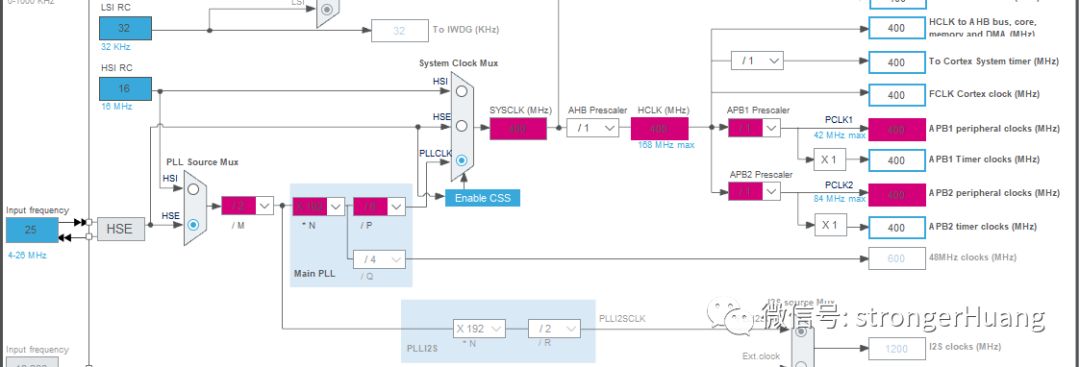

3STM32CubeMX配置時鐘樹

STM32CubeMX配置時鐘不用擔心出錯。

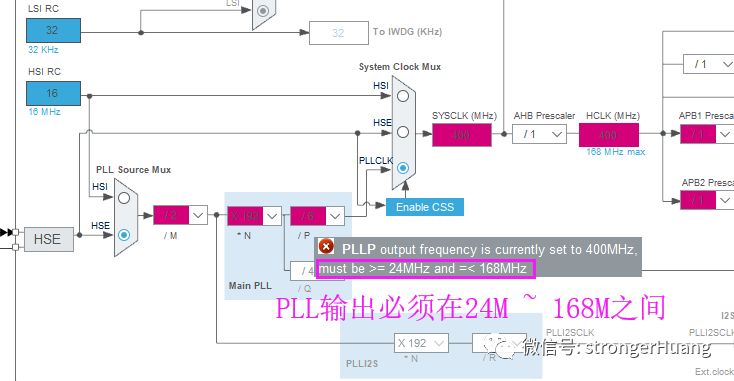

原因很簡單,這個工具配置時鐘樹,如果出錯,會有紅色警告。

如下圖:

具體每一個紅色警告錯誤的原因,將光標移到紅色警告過會有相應提示信息。

比如,輸出PLLP值超過規定范圍:

有這個提示信息,再也不怕配置出錯了。

PLL的倍頻和分頻值

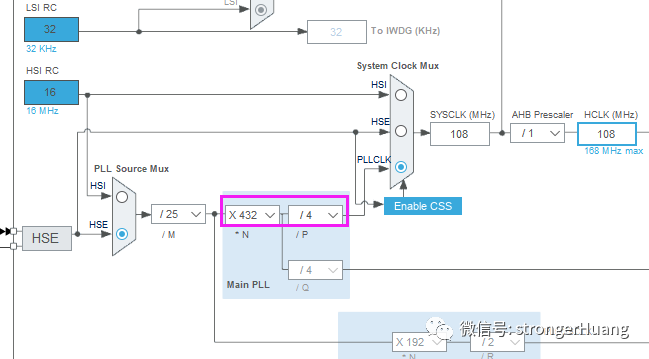

有人覺得前面倍頻N值很大(如下圖),這樣會不會出問題?

答案肯定是不會。但不建議將參數N設置為最大值。

特定時鐘頻率

有些時候,我們要求有特定時鐘頻率,比如USB,ETH等。這個時候PLL參數就需要合理才行。

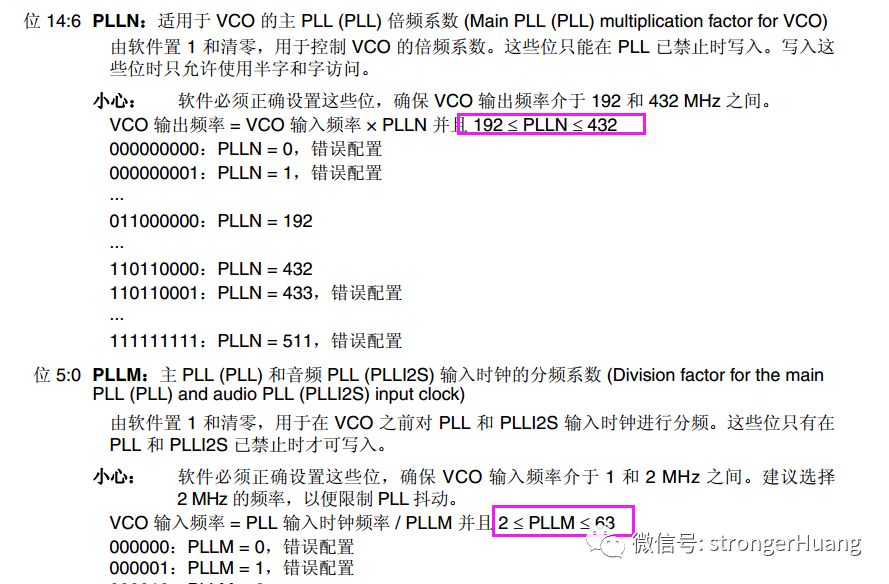

4STM32手冊可查看PLL參數范圍

STM32的時鐘,在之前使用標準庫,或者寄存器時,使用的晶振頻率不是官方推薦的,很多人就會搞暈。

那么,就只有參看對應手冊,手冊上是有明確說明的。比如F4手冊RCC章節,詳細說明的PLL各參數值范圍。

本文就寫到這里,希望對你有幫助。

-

mcu

+關注

關注

146文章

17317瀏覽量

352646 -

STM32

+關注

關注

2272文章

10923瀏覽量

357573 -

pll

+關注

關注

6文章

781瀏覽量

135332

發布評論請先 登錄

相關推薦

config37中根據DACCLK配置jesd clock,請問下jesd clock大小是跟之前配的serdes pll配置的line rate成40倍關系的嗎?

STM32F103×8/STM32F103×B MCU手冊

使用LMK04821芯片的單PLL模式,輸出的時鐘頻率基本上是對的,但PLL2不能lock,為什么?

TLV320ADC3101 pll_clk時鐘輸出,配置參數應該怎么配呢?

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

PLL1707/PLL1708 3.3V雙通道PLL多時鐘發生器數據表

紫光同創——PLL IP 的使用(Logos2)

LVDS用法:LVDS RX 時鐘選擇 LVDS的PLL的復位信號的處理

擔心STM32時鐘PLL各參數配錯嗎?

擔心STM32時鐘PLL各參數配錯嗎?

評論