本教程由作者strongerHuang于2019年09月原創(chuàng)發(fā)布。

版權所有:禁止商用

申明:該文檔僅供個人學習使用,轉載請公眾號聯(lián)系作者授權。

1寫在前面

SPI:Serial Peripheral Interface,是串行外設接口。

SPI是由摩托羅拉于 1985 年前后開發(fā),是一種適用于短距離、設備到設備通信的同步串行接口。

從那時起,這種接口就已成為許多半導體制造商,特別是微控制器(MCU)和微處理器(MPU)采用的事實標準。

2SPI接口

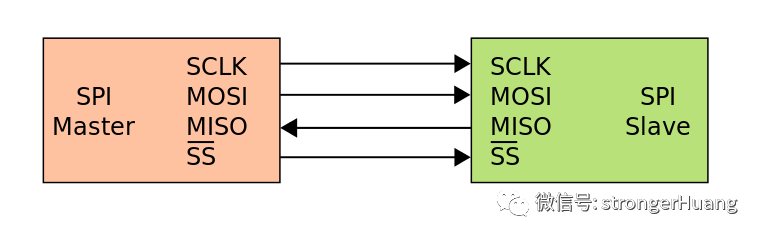

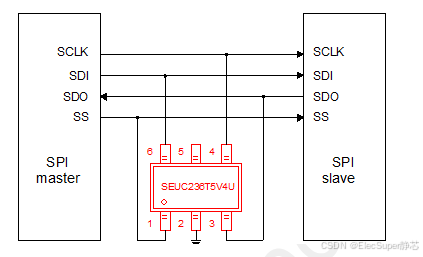

SPI總線是一種4線總線,通常有一個主設備和一個或多個從設備,需要至少4根線,事實上3根也可以。

MOSI:Master Output Slave Input,主設備數(shù)據(jù)輸出,從設備數(shù)據(jù)輸入;

MISO:Master Input Slave Output,主設備數(shù)據(jù)輸入,從設備數(shù)據(jù)輸出;

SCLK:Serial Clock,時鐘信號,由主設備產(chǎn)生;

SS:Slave Select,從設備選擇信號,由主設備控制;

上面的SS信號,也可以理解為CS信號,一般是低電平有效,所以也是NSS(非)信號;

CS:Chip Select,片選信號(從設備使能/選擇信號),由主設備控制;

2.1 一主一從

最基本的SPI通信就是一主一從,比如:一個STM32作為主機,一個W25Q16(SPI Flash)作為從機。還有兩個MCU之間進行SPI通信等。

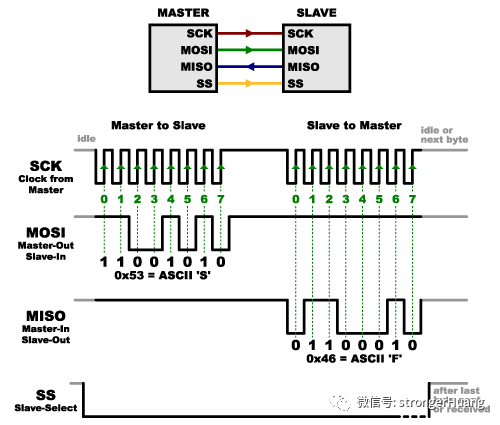

上圖例子是主機發(fā)送一個字節(jié)數(shù)據(jù)(0x53),從機應答一個字節(jié)數(shù)據(jù)(0x46)。

2.2 一主多從

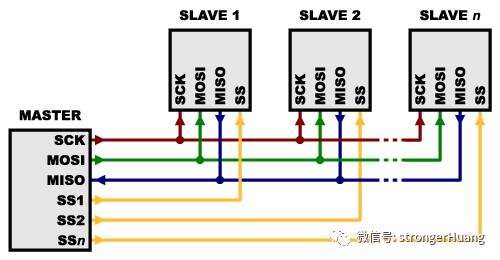

SPI可以一主一從(一個主機,一個從機),但也可以一主多從。一主多從常見有兩種連接方式。

A.常規(guī)

通常,每個從機都需要一條單獨的SS線,要與指定的從機通信,將該從機的SS線設為低電平,并將其余的保持為高電平即可。

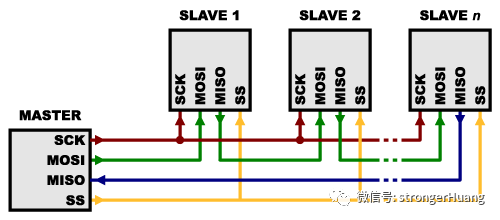

B.一條SS信號

某些應用只需要一條NSS即可(比如:移位寄存器),對于這種布局,數(shù)據(jù)從一個從設備移位到另一個從設備。

3SPI數(shù)據(jù)傳輸

SPI的通信比較簡單,一個時鐘傳輸一位數(shù)據(jù)(主機 -> 從機,或者從機 -> 主機)。

3.1 SPI時鐘

理論上SPI的時鐘頻率可以做到很大,一般幾MHz~幾百MHz,拿常見的W25Q16來說,SPI最高支持80MHz。

SPI通信速率要結合實際情況,不能超過主機或從機支持的最大時鐘頻率。

3.2 SPI數(shù)據(jù)

SPI的數(shù)據(jù)分兩個方向:

MOSI:主機 -> 從機

MISO:從機 -> 主機

SPI通信有一個“缺點”:沒有指定的流控制,沒有應答機制確認是否接收到數(shù)據(jù)。

可以理解為:不知道是什么時候主機發(fā)給從機,什么時候從機發(fā)給主機,到底該發(fā)多少字節(jié)數(shù)據(jù)等。

此時,需要通信的主機和從機達成約定,一般由主機進行控制讀寫的操作。

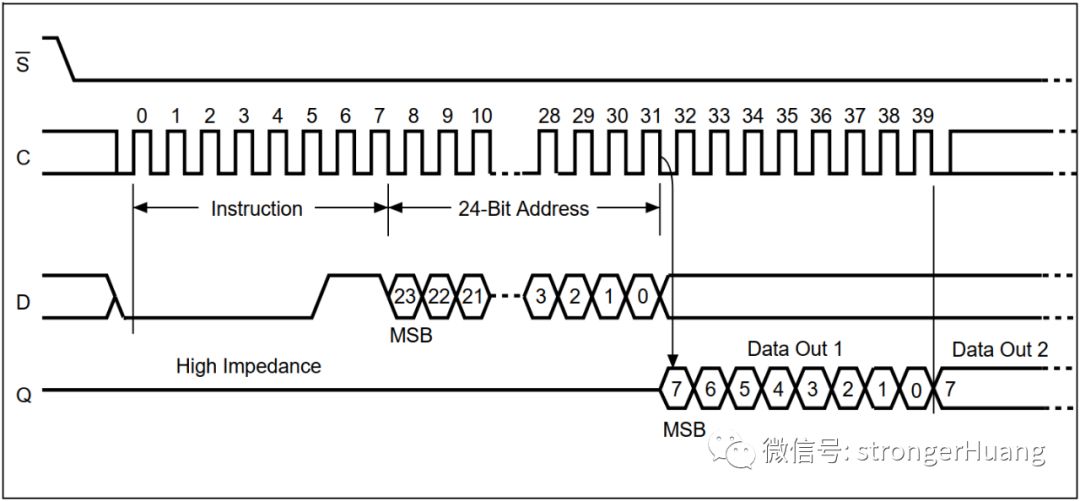

比如下面這個讀寫SPI Flash數(shù)據(jù)的操作:

前面1字節(jié)是指令,緊接著再3字節(jié)(24位)地址,都是由主機發(fā)送給從機。之后,主機讀取數(shù)據(jù)(由從機發(fā)送出來)。

3.3 時鐘極性和相位

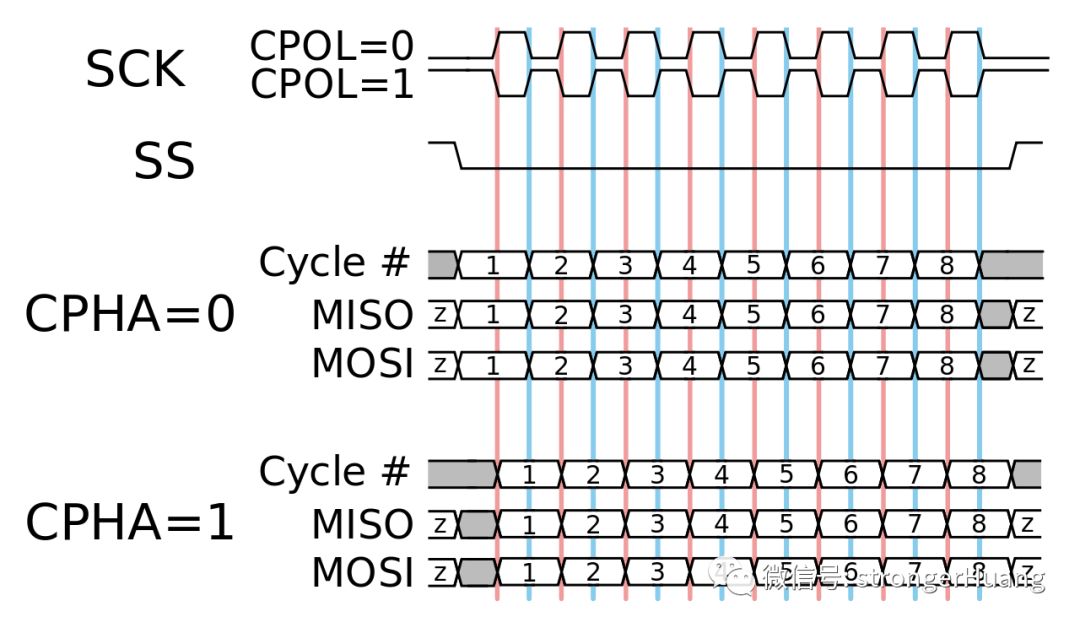

除了設置時鐘頻率外,主機還必須配置與數(shù)據(jù)有關的時鐘極性和相位。

CPOL確定時鐘的極性,極性可以通過簡單的逆變器進行轉換。

CPHA確定相對于時鐘脈沖的數(shù)據(jù)位的時序(即相位)。

一般集成有SPI外設的處理器,都有SPI相關的配置寄存器,拿STM32來說,參考手冊里面有詳細介紹SPI配置的信息。

建議大家結合時序圖理解,不能死記硬背。

5

說明

1.該文檔僅供個人學習使用,版權所有,禁止商用。

2.本文由我一個人編輯并整理,難免存在一些錯誤。

3.本文收錄于公眾號『嵌入式專欄』,關注微信公眾號回復【通信教程】即可查看全系列教程。

6最后

-

通信

+關注

關注

18文章

6072瀏覽量

136433 -

SPI接口

+關注

關注

0文章

259瀏覽量

34554

發(fā)布評論請先 登錄

相關推薦

DDC112U的數(shù)據(jù)輸出接口能否和MCU的SPI接口進行連接?

DAC7714的SPI直接接FPGA的3.3VIO,這樣用長時間會不會隨器件損耗接口通信出現(xiàn)不正常?

使用stm32的SPI5通信接口與DAC1282通信失敗了怎么解決?

ADS131B04-Q1 SPI通信時,為什么無法得到正常的CRC校驗?

spi master接口的fpga實現(xiàn)

SPI接口靜電放電防護方案

SPI通信協(xié)議的基本概念和工作模式

單片機SPI通信實現(xiàn)

請問可以用FX3作為SPI的Master,通過GPIF II接口實現(xiàn)SPI通信嗎?

想搞懂通信協(xié)議?先來看一篇SPI熱熱身

鴻蒙原生應用元服務開發(fā)-WebGL網(wǎng)頁圖形庫開發(fā)接口說明

超詳細的SPI原理和通信模式

通信教程的04_SPI接口說明及原理

通信教程的04_SPI接口說明及原理

評論