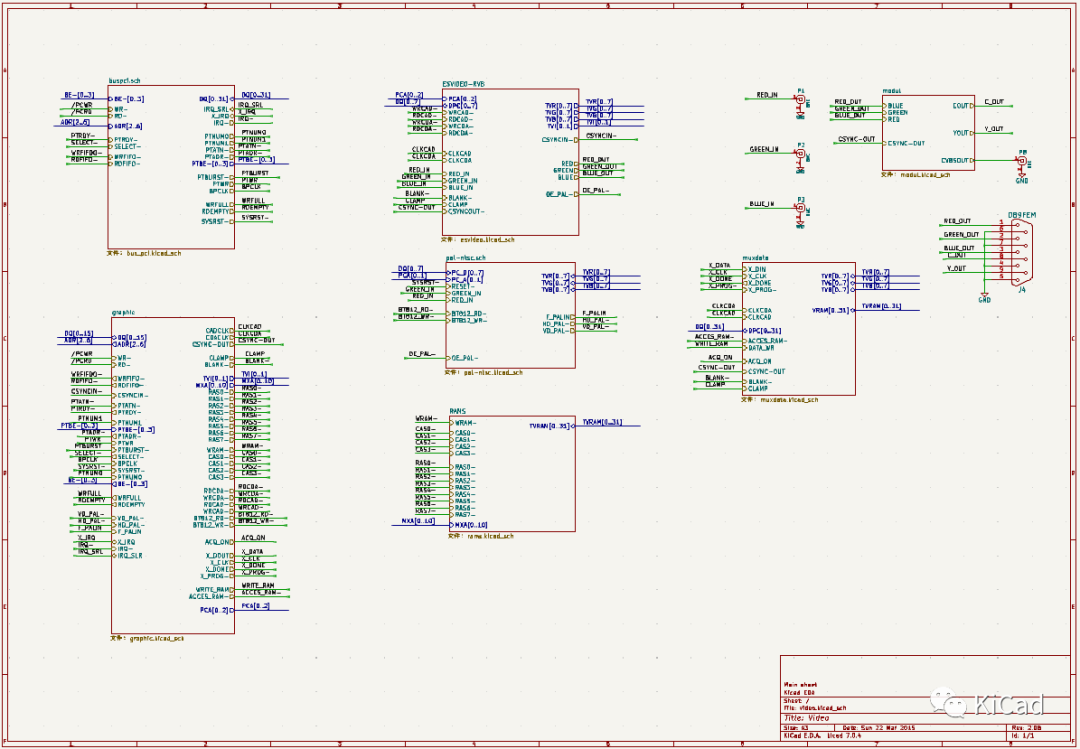

作為allegro專業layout的我們,由于設計軟件的限制,有時候客戶提供的原理圖可能是AD或Power Logic繪制的,而AD或Power Logic的原理圖轉成orcad原理圖后可能存在丟失網絡或器件的風險,無法直接用來輸出網表導入Allegro設計。 如果對轉換后的原理圖進行修正得整個原理圖從頭到尾徹底檢查一遍,這個工作量以及存在的風險對于我們layout工程師和硬件工程師來說可能都不太現實。 如果能將AD或Power Logic原理圖產生的網表轉成Allegro格式的網表,那就能導入Allegro里面設計了,就不需要轉換原理圖了,省事又省時,這是最為簡單方便又靠譜的方法了。

工程師的巨大福利,首款P_C_B分析軟件,點擊免費領取

Allegro網表的調法有兩種:

一種是第一方網表;

另一種是第三方網表。

第一方網表需要通過Orcad Capture來產生,也是絕大部分人使用的導入方法。 第三方網表可以通過各種原理圖設計軟件來產生(如protel、AD、Power Logic、DxDesigner、Eagle等)。 第一方網表的調入比較嚴謹,要求原理圖與PCB封裝必須完全一一對應,其網表格式也相對復雜。 但是第三方網表的調入就相對沒那么嚴謹,封裝的器件管腳只要不比原理圖器件管腳少就可以了,器件管腳數量可以不需要一樣多,其網表格式相對比較簡單有規律性。 因此,我們可以通過將AD或Power Logic原理圖產生的網表內容轉換成符合Allegro第三方網表的格式,然后導入Allegro即可!

Allegro第三方網表封裝定義的標準格式 其中,感嘆號和分號是分隔符,Value可有可無,給value添加單引號可屏蔽value值里面的一些非法字符,如下圖所示:

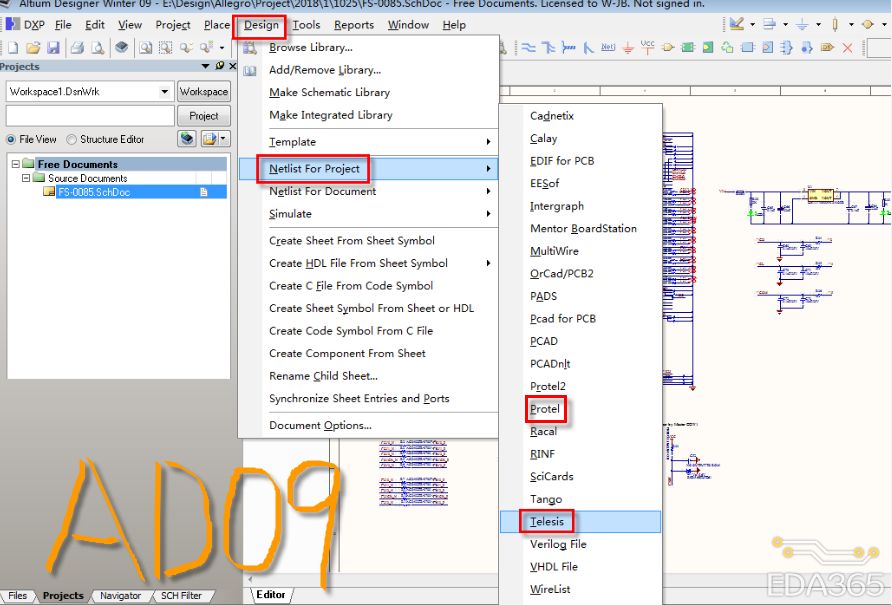

另一種格式的第三方網表 1、輸出網表:A. Protel或AD原理圖輸出的網表可以有兩種選擇:protel或telesis。

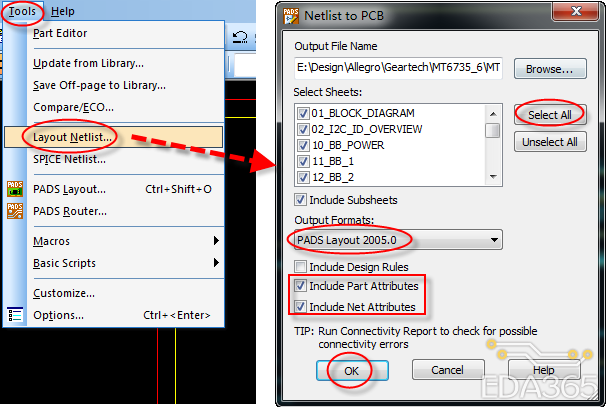

B. Power Logic原理圖輸出網表:

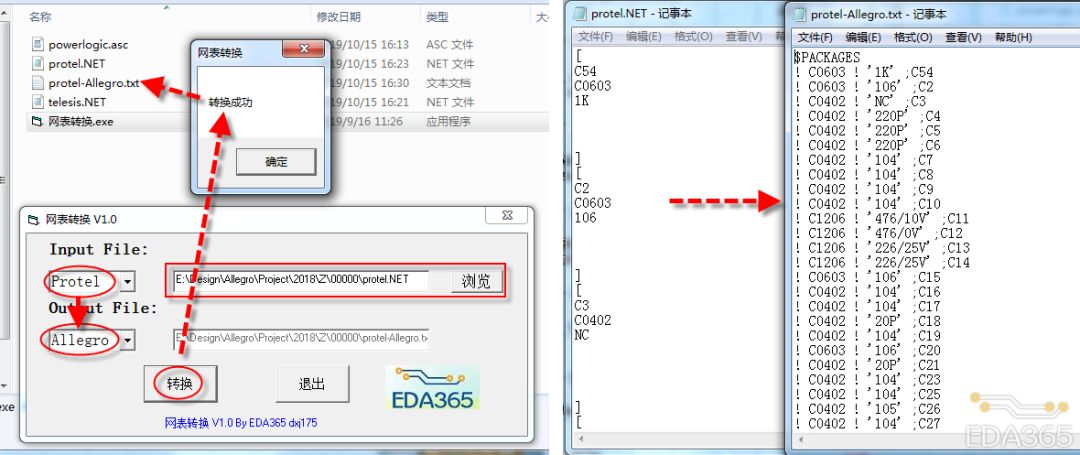

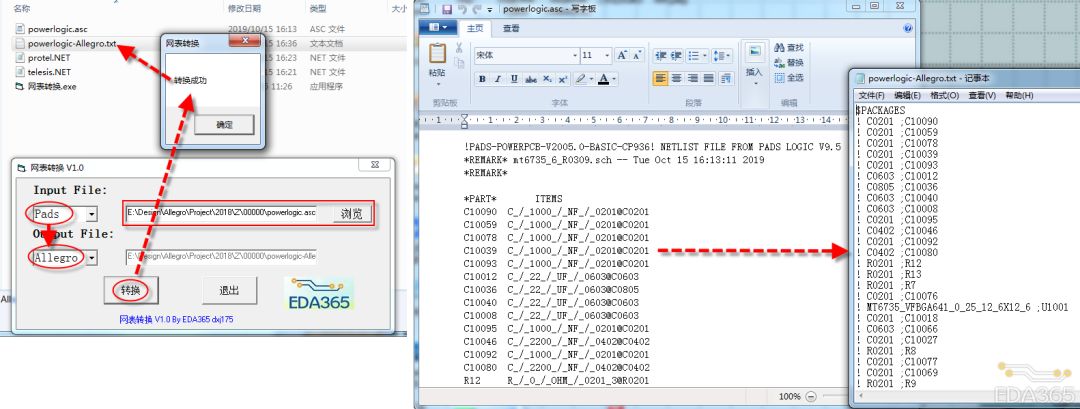

2、將AD或Power Logic輸出的網表轉換成Allegro格式的第三方網表:使用附件里面的“網表轉換.exe”工具將對應格式的網表轉成Allegro格式的第三方網表。

注意:“網表轉換.exe”工具如果對應網表的格式選擇不對,轉換出來的網表文件里面的內容是空的。該程序Protel轉Allegro網表會將器件的Value值帶入,而pads轉Allegro網表器件的Value值是不會帶入的。

如果是Telesis格式的網表,由于該程序里面沒有Telesis格式的網表轉Allegro第三方網表,我們可以到以下載一個skill加載使用即可。

注意:文末有下載方式,文章“Protel格式網表轉換Allegro格式網表的Skill程序”是一個對skill程序的講解。

3、Allegro的第三方網表調入與第一方網表調入不同,第三方網表調入還需要器件的device才行。因此我們還需要生成器件的device文件,也就是后綴為txt的封裝文件,加載附件里面的skill文件“auto_create_device.il”,然后隨便打開封裝庫里面的任意一個dra文件,在命令欄里面輸入命令“create_device_batch”即可將當前目錄下的所有dra自動生成psm,pad和txt文件;

skill的加載方法:

將附件里面的“auto_create_device.il.il”放到cadenceSPB_16.6sharelocalpcbskill目錄下,用記事本打開cadenceSPB_16.6sharelocalpcbskill目錄下的allegro.ilinit文件,(如果沒有這個文件就自己新建一個txt文本文檔,然后將文件名稱和后綴修改為allegro.ilinit即可),在里面獨立一行添加一行代碼:load("auto_create_device.il.il"),然后保存文件,再重啟軟件即可!

4、指定庫路徑:將下圖的三個庫路徑指定到封裝庫路徑下。

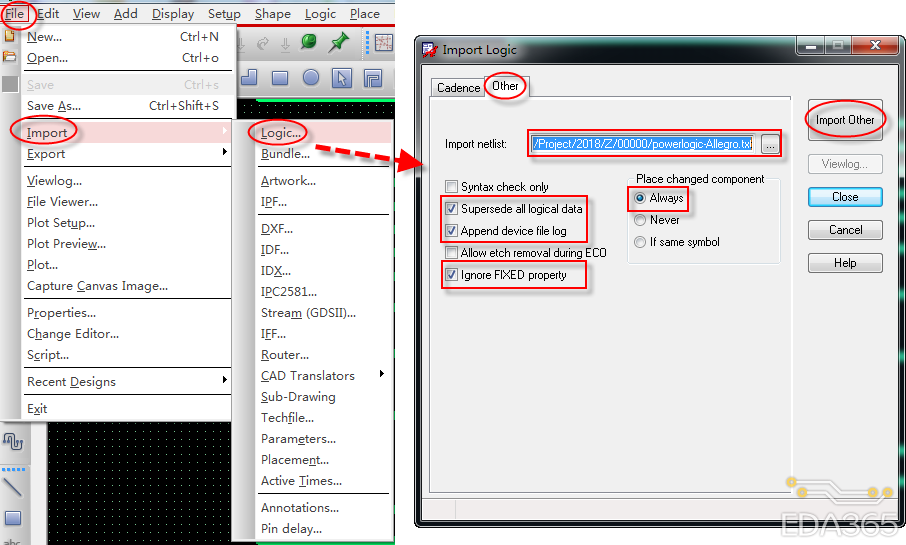

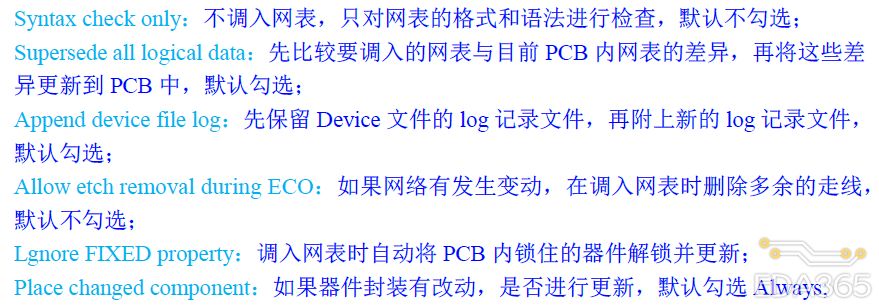

5、導入轉換后的第三方網表:按照下圖選擇轉換后的網表文件,并按下圖勾選對應的選項,然后導入即可。 如有報錯則根據當前目錄下生成的netin.log報表查找關鍵詞“error”,并根據error提示解決問題即可。

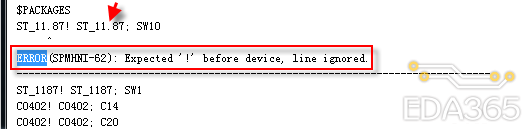

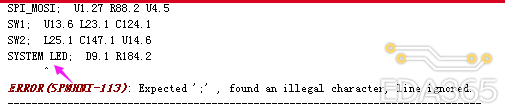

與第一方網表調入相比,第三方網表調入報錯的問題都比較清晰易懂,不難解決,以下是第三方網表調入報錯的一些常見問題類型和解決方法:A. 原理圖封裝名稱中帶有非法字符(如小數點、空格、@、#、¥、%、&、*、(、)、+等)。

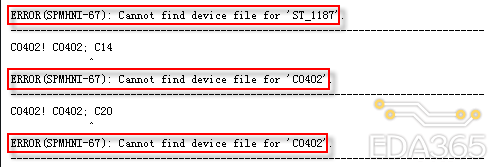

解決方法:根據提示的位號和封裝名稱將原理圖上對應器件的封裝名稱中的非法字符統一修改為下滑杠。B. 所有封裝都有了,但是導入還是報錯:沒有指定庫路徑。

解決方法:導入前先將devpath、padpath和psmpath三個庫路徑設置到封裝庫所在的目錄,再導入網表。C. 所有封裝都有了,庫路徑也指定了,但導入也還報錯:器件的封裝沒有生成device文件。解決方法:先將封裝庫生成device文件后再導入。D. 庫路徑里面帶有非法字符,軟件無法識別庫路徑。解決方法:將文件目錄里面的非法字符改掉。E. PCB封裝名稱中帶有非法字符,造成PCB封裝名稱與原理圖器件封裝名稱對不上。解決方法:將PCB封裝名稱修改為原理圖器件封裝的名稱,與之對應。

注意:C、D、E的報錯類型提示跟B是一樣的。

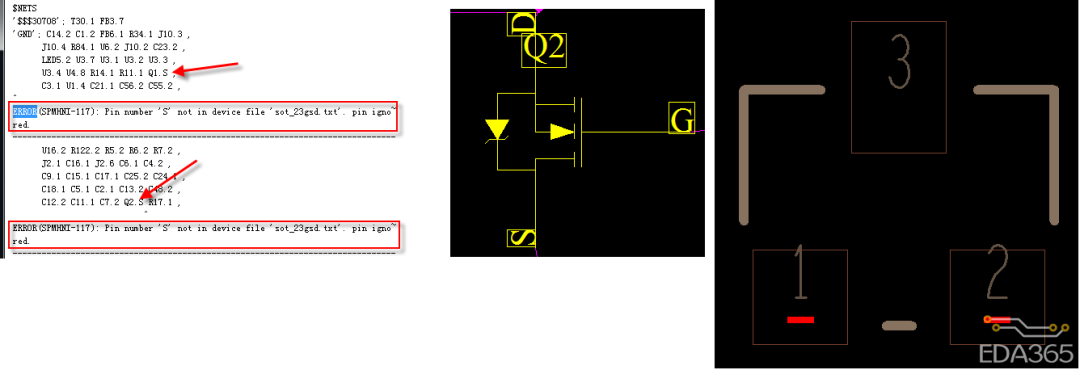

F. PCB封裝的pin number與原理圖器件的pin number不匹配(原理圖三極管使用的pin number是:GSD ,而PCB封裝是:123)。

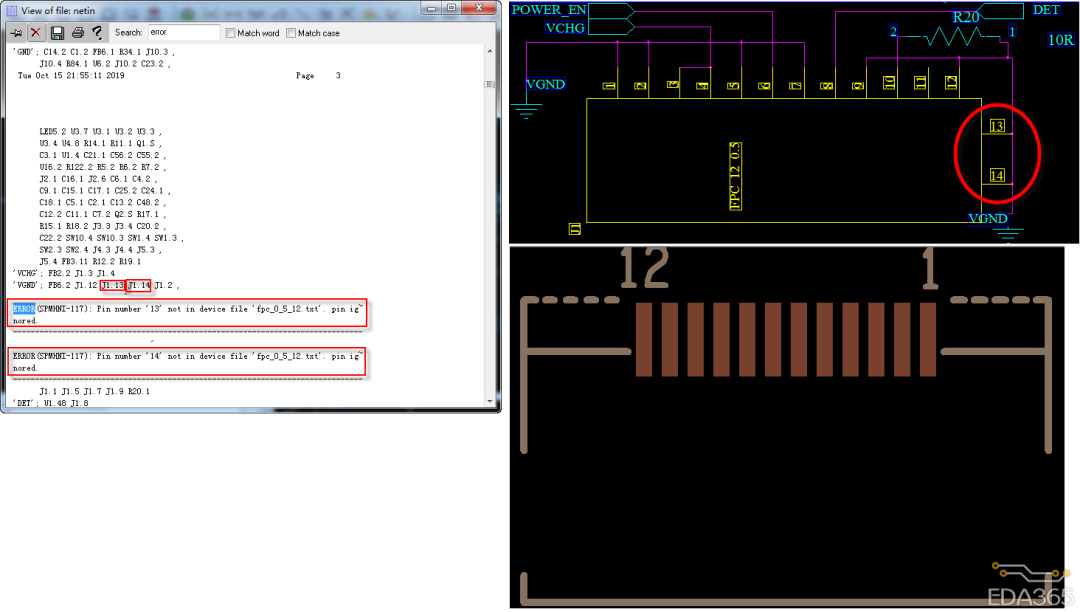

解決方法:修改原理圖或PCB封裝,使其pin number對應即可。G. PCB封裝的pin管腳比原理圖的少(如下圖原理圖多了13和14兩個固定腳,而PCB封裝則沒有)。

解決方法:檢查對應的封裝管腳,如少了則給PCB封裝加上。H. 原理圖網絡名稱帶有空格。

解決方法:將原理圖上帶有空格的網絡名稱中的空格去掉或修改為下滑桿。 以上為常見的第三方網表導入報錯問題,可以根據問題報錯提示進行排查。 另外,有時候由于AD或PADS原理圖封裝命名的不規范性造成網表里面帶有大量非法字符,修改原理圖太麻煩的話可以轉換網表后在第三方網表里面進行字符替換。 然后保存后再導入,不過這樣每次更新網表都得這樣替換一次,比較麻煩,建議有時間最好修改下原理圖與PCB對應比較好,這樣后續更新網表就可以轉換后直接導入了,而不需要每一次都要替換非法字符。

注意:第三方網表調入與第一方網表調入的區別:

1、第三方網表導入是需要器件的device文件的,如果沒有device文件是導入不了的,庫路徑里面的devpath也必須指定。

2、必須先解決所有的報錯問題才能成功導入;

3、第三方網表調入的PCB是不支持與Orcad原理圖直接交互的;

4、文件名稱和路徑中不要使用非法字符。Allegro中所說的非法字符就是除了數字、字母、中桿和下滑桿以外的其它所有字符,包括空格。

Allegro有些操作是不支持非法字符的,亂用非法字符有時候就是這么一個不起眼的壞習慣都能折騰你半天時間還找不到問題所在,養成良好的設計習慣能讓你少走彎路。

-

原理圖

+關注

關注

1301文章

6358瀏覽量

235221 -

封裝

+關注

關注

127文章

7997瀏覽量

143416 -

PCB設計

+關注

關注

394文章

4701瀏覽量

86360 -

allegro

+關注

關注

42文章

662瀏覽量

145557 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

15710 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4743 -

可制造性設計分析

+關注

關注

4文章

866瀏覽量

5810

原文標題:教你如何將 AD 或 PADS 的原理圖導入 Allegro 做 Layout

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

將測量的太陽光譜導入VirtualLab Fusion

PADS邏輯教程

PADS Layout版本,10度高速線怎么走

急!!!!求助大佬。PADS LAYOUT軟件BUG問題

立創商城導出來的CAE和PCB封裝用PADS導入遇到的問題

AD畫完原理圖后如何導入PCB

altium怎么把原理圖導入pcb

利用DX-BST原理圖智能工具實現原理圖對比的技術方法

TARGET3001!用法篇-如何將Altium文件導入到TARGET中

TARGET3001!用法篇-如何將Altium文件導入到TARGET中

如何將AD或PADS的原理圖導入Allegro做Layout

如何將AD或PADS的原理圖導入Allegro做Layout

評論