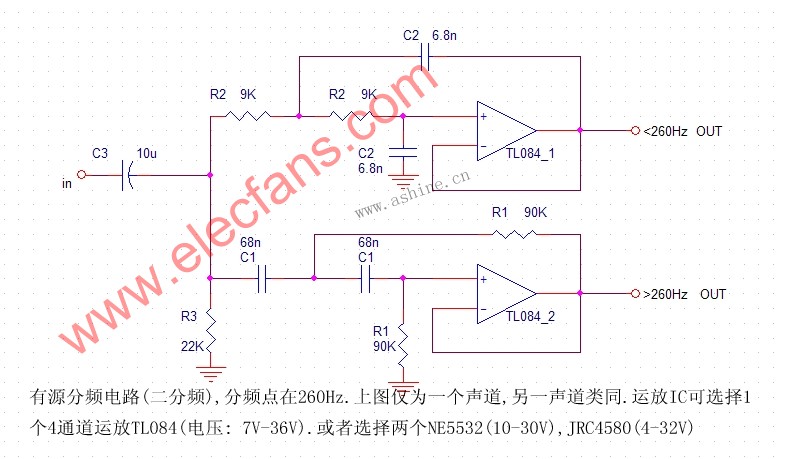

在一個揚聲器系統里,人們把箱體、分頻電路、揚聲器單元稱為揚聲器系統的三大件,而分頻電路對揚聲器系統能否高質量地還原電聲信號起著極其重要的作用。尤其在中、高頻部分,分頻電路所起到的作用就更為明顯。

分頻電路的作用

1、合理地分割各單元的工作頻段;

2、合理地進行各單元功率分配;

3、使各單元之間具有恰當的相位關系以減少各單元在工作中出現的聲干涉失真;

4、利用分頻電路的特性以彌補單元在某頻段里的聲缺陷;

5、將各頻段圓滑平順地對接起來。

顯然,分頻電路的這些作用已被人們所認識和接受。

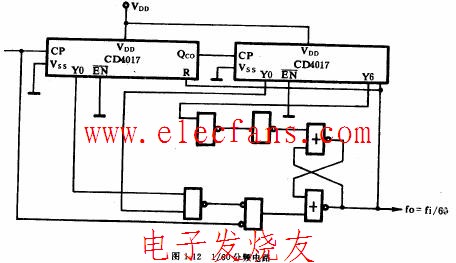

占空比為50%的3分頻電路

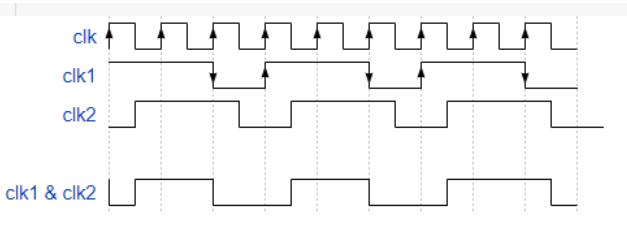

時序圖工具

{signal: [

{name: ‘clk’, wave: ‘P…P…’},

{name: ‘clk1’, wave: ‘H.LH.LH.L’},

{name: ‘clk2’, wave: ‘lh.lh.lh.l’,phase:0.5},

{},

{name: ‘clk1 & clk2’, wave: ‘nhlnhlnhp’}

]}

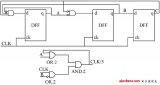

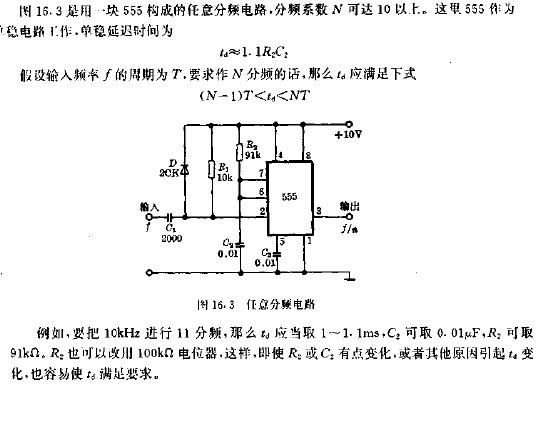

目前各個FPGA廠家一般都有集成的鎖相環資源,但在設計對于時鐘要求不高的基本設計,通過邏輯進行時鐘分頻依然有效,還可以節省芯片內部的鎖相環資源,其中分頻又分為,偶數分頻,奇數數分頻,小數分頻,此次主要涉及奇數分頻,設計一個占空比為50%的三分頻電路,仿真環境采用edaplayground.com.

奇數分頻原理

分別采用上升沿進行一個占空比為2/3的始終,在次用下降樣設計同樣的占空比,最后將兩者進行相與,得到占空比為50%的三分頻電路。

// Code your design here

`timescale 1ns/1ps

module div3_half(

input Sys_clk,

input Sys_reset,

output div3 ,

output clk1,

output clk2

);

reg clk1;//2/3 is high posedge

reg clk2;//2/3 is high negedge

//counter

reg [1:0]count;

always @ (posedge Sys_clk )

if(!Sys_reset)

count 《= 2‘b0;

else if(count ==2’d2)

count 《= 2‘b0;

else

count 《= count +1’b1;

always @(posedge Sys_clk )

if(!Sys_reset)

begin

clk1 《=1‘b1;

end

else if(count == 2’d1 | count == 2‘d2)

clk1 《= ~clk1;

always @(negedge Sys_clk )

if(!Sys_reset)

begin

clk2 《=1’b1;

end

else if(count == 2‘d2 | count ==2’d1)

clk2 《= ~clk2;

//------------------------------------------------

assign div3 =clk1 & clk2;

endmodule

// Code your testbench here

// or browse Examples

`timescale 1ns/1ps

module tset();

reg Sys_clk;

reg Sys_reset;

wire div3;

initial

begin

$dumpfile(“d.vcd”);

$dumpvars(1);

Sys_clk=0;

Sys_reset = 0;

#100

Sys_reset =1;

end

always #10 Sys_clk = ~Sys_clk;

div3_half div3_half_inst(Sys_clk,Sys_reset,div3,clk1,clk2);

endmodule

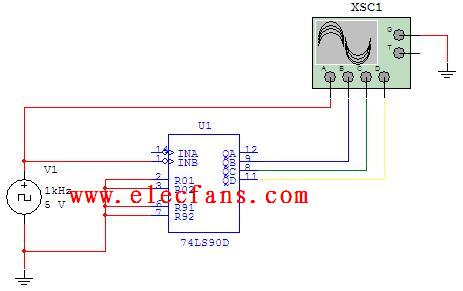

仿真結果

-

分頻

+關注

關注

0文章

241瀏覽量

24910 -

分頻電路

+關注

關注

7文章

45瀏覽量

35998

發布評論請先 登錄

相關推薦

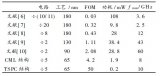

用VHDL語言實現3分頻電路

用VHDL語言實現3分頻電路(占空比為2比1)

基于65nm工藝的五分頻器設計方案

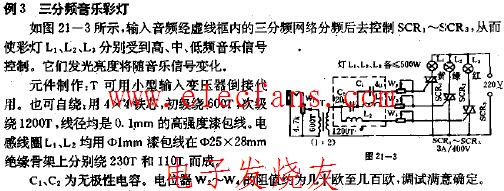

經典三分頻電路介紹(三款不同的三分頻電路)

占空比為50%的3分頻電路

占空比為50%的3分頻電路

評論