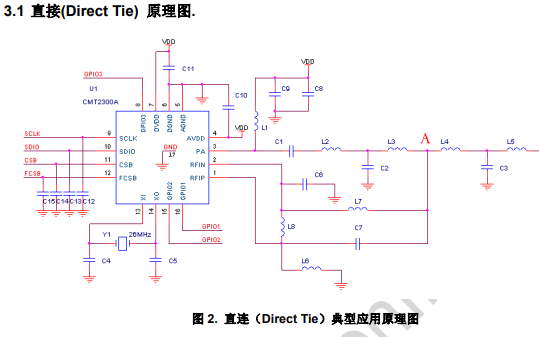

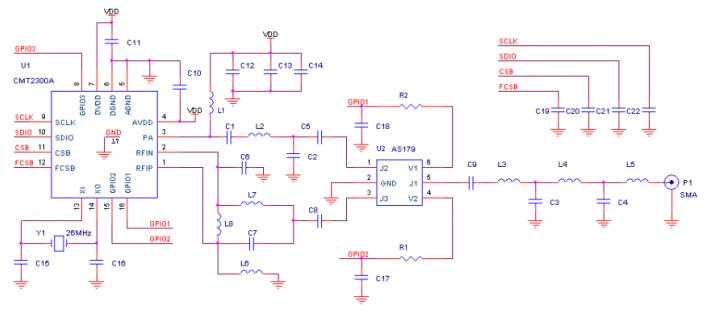

通常,在設計射頻匹配網絡時,需要兼顧幾個方面:端口的阻抗匹配必須一致,插入損耗盡可能小,帶外衰減盡可能大,PA功率與效率盡可能高,元件個數盡可能少。針對CMT2300A射頻匹配網絡設計,有DirectTie和SwitchType兩種匹配方法。

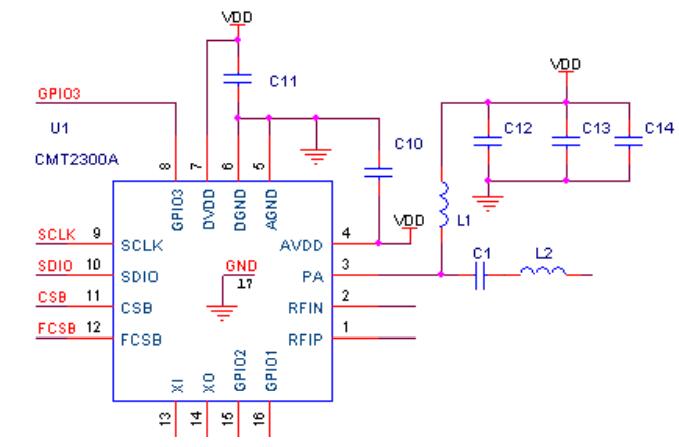

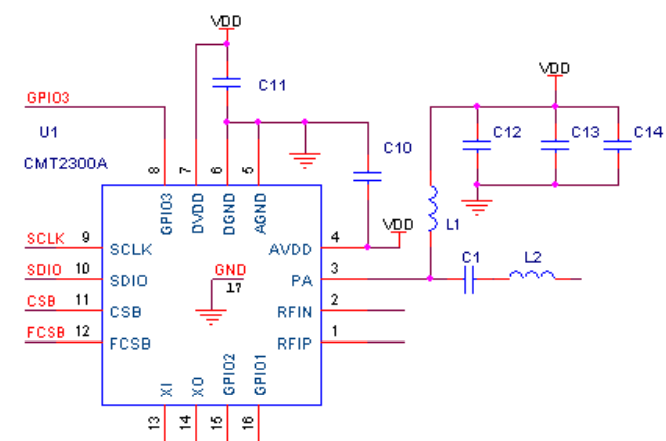

直連(DirectTie)匹配電路無需RF開關,TX和RX通路阻抗變換后直連到天線。CMOSTEKDirectTie匹配優化了電路結構,采用較少的元器件,既可滿足CE/FCC規范,又實現高接收靈敏度,高效率和大功率輸出。

1、L1是扼流電感。

2、C8-C11是電源退耦電容,用于減少PA輸出對電源的影響。根據實際的應用需求要做適當調整。

3、C1是隔直電容,并且與L2的部分電感在工作頻點形成諧振起到諧波抑制作用。

4、上圖標識的A點為直連點,該點的阻抗是50Ω。

5、L2,C2和L3組成TX匹配網絡,實現PA輸出和直連點阻抗匹配。

6、C6,L6,C7,L7,L8組成RX巴倫匹配網絡,實現接收機的輸入阻抗和直連點匹配,并使得接收信號到達差分輸入口RFIP,RFIN處時幅度相等,相位相差180度。

7、L4,C3,L5為50Ω到50Ω的T型低通濾波匹配網絡。

8、Y1推薦用頻率容差±20ppm的26MHz晶體,可接受的晶體頻率容差取決于用戶產品通訊系統的要求,如頻率,信道,帶寬等。

9、C4,C5為晶體負載電容(注意芯片內部已經集成了約4pF的負載電容,以CL=15pF的26MHz晶體為例,折合晶體相連走線分布電容2pF,C4和C5取值約15*2-4-2=24pF)。

10、C12-C15濾波電容,在布線不合理或走線太長情況下,串口CSB,FCSB,SDIO,SCLK管腳容易受到干擾,功率輸出(20dBm)越大,工作頻率越低,受干擾的概率越大,建議靠近四個管腳預留到地電容(27pF)濾除射頻干擾。

推薦客戶參考CMOSTEK直連(DirectTie)匹配的設計,TX和RX通路到直連點之間的網絡盡量采用官方推薦的相同值的元件。而天線匹配濾波網絡(L4,C3,L5),要根據天線阻抗,成本要求,是否要求滿足CE/FCC規范等因素,來調整濾波器的階數和元件值。如線路板面積受限,建議L1-L8,仍采用高Q值疊層0603電感(如SunlordSDCL1608系列),但電容都可采用0402封裝。

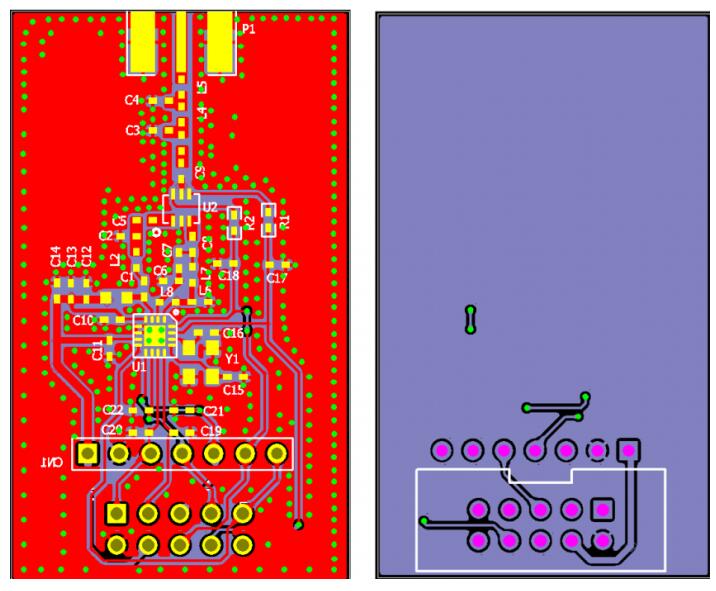

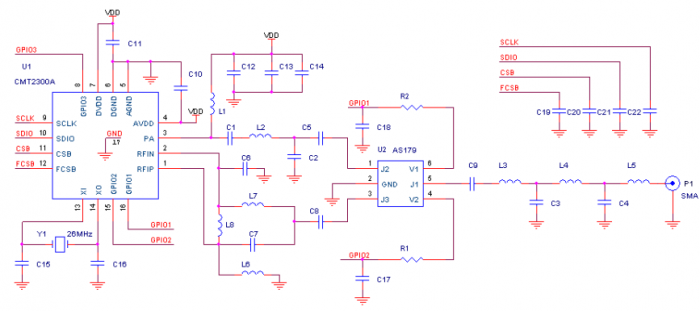

CMOSTEK直連(DirectTie)匹配PCBLayout為兩層布線設計。

說明如下

1、射頻信號路徑盡量的直且短,減小射頻信號輸入與輸出的的損耗。

2、射頻走線應該盡量平整,以減小傳輸線上的阻抗波動而產生反射。在上圖中L2到P1間走線為50Ω阻抗傳輸線。本參考設計中,雙面板為FR4板材,介電常數Er=4.6,銅皮厚1oz,PCB板厚0.8mm,當取傳輸線寬度為1mm左右,且傳輸線與包地(GND)的間隙設定為0.35mm時,就可得到阻抗為50歐姆的傳輸線。

3、盡量不要有絲印落在射頻路徑上,絲印會影響傳輸線阻抗。

4、L1離PA管腳盡量近。相鄰電感盡量正交擺放,可減少相互耦合。

5、直連結合點的分支網絡(上圖C2,L7和C7相連部分)要盡量短。

6、射頻通路,晶振電路和IC的下方相鄰層要有完整的鋪地(GND)。

7、TX和RX通路間要有GND網絡進行隔離。

-

射頻

+關注

關注

104文章

5618瀏覽量

168221 -

電路設計

+關注

關注

6677文章

2464瀏覽量

205336

發布評論請先 登錄

相關推薦

天線和射頻匹配電路設計-培訓教程下載

【下載】《射頻電路設計》——快速掌握射頻電路的基本設計方法和原則

差分匹配電路設計和雙頻匹配電路設計培訓教程

CMT2300A無線數據收發模塊資料

為什么說CMT2300A是Sub-1GHz超低功耗的射頻收發器

超低功耗Sub-1GHz性價比首選方案:CMT2300

超低功耗Sub-1GHz性價比首選方案:CMT2300

CMT2300A 超低功耗Sub-1GHz射頻收發器的詳細中文資料免費下載

使用CMT2300A芯片設計射頻匹配網絡的數字信號和電源濾波電路與鋪地

CMT2300A的開關射頻匹配網絡電路設計

射頻和天線匹配電路設計中LC器件選擇

CMT2300A 433MHz無線收發芯片

CMT2300A的直連射頻匹配網絡電路設計

CMT2300A的直連射頻匹配網絡電路設計

評論