作為商業(yè)上最成功的on-chip ESD 公司,從2002成立之初到現(xiàn)在經(jīng)歷了15年,員工也從1-2個(gè)人發(fā)展到目前的17個(gè)人。回顧這家從IMEC SPIN OFF的小而美的公司,總結(jié)起來(lái)有幾點(diǎn)是值得國(guó)內(nèi)公司借鑒的。

正確的切入點(diǎn):

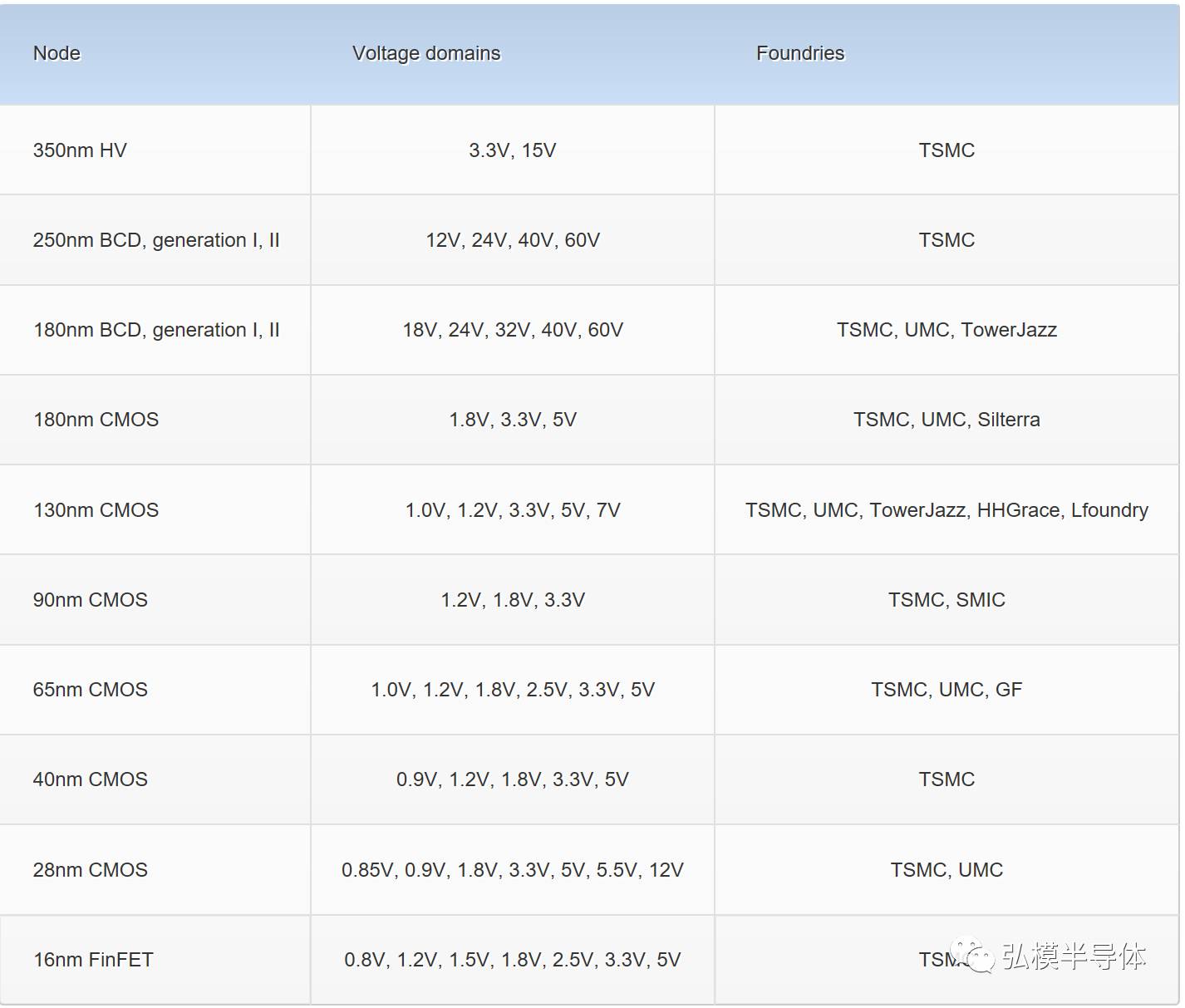

作為半導(dǎo)體廠,本身也有自身的ESD部門(mén),Sofics很好的避開(kāi)了和半導(dǎo)體廠的沖突,尋找更有特色的ESD解決方案,比如超低功耗,高速,超高壓方面的產(chǎn)品應(yīng)用,同時(shí)也選擇對(duì)ESD有特別要求的BCD工藝的設(shè)計(jì)下手,通過(guò)省MASK, 省ESD面積,提高性能和TIME TO MAREKT,YIELD讓客戶得益的同時(shí),自己在這個(gè)市場(chǎng)也獲得一席之地。經(jīng)過(guò)長(zhǎng)時(shí)間的客戶積累,on-Chip ESD 解決方案覆蓋了TSMC主流工藝, 也使得ESD IP轉(zhuǎn)移到任何T-LIKE的FAB非常迅速,成功率非常高(>95%). 如果看不清下面的圖片,請(qǐng)點(diǎn)擊放大

除了以上工藝,對(duì)于SOI, 3DIC,RAD-HARD 抗輻射等,Sofics 都有完整解決方案。 Sofics 也有ESD設(shè)計(jì)的EDA工具TAKE CHARGE 和 POWER QUBICS,分別覆蓋標(biāo)準(zhǔn)IO界面0-5V和5-100V的on-chip ESD 解決方案,讓設(shè)計(jì)公司對(duì)ESD設(shè)計(jì)興手拈來(lái)。 同時(shí),對(duì)于客戶的私人定制的高性能IO和特殊要求IO, Sofics也有自己的應(yīng)對(duì)方案,盡量滿足客戶需求,總的來(lái)說(shuō),在Sofics這邊,總能找到一款適合你的on-Chip ESD方案。

2. 核心技術(shù):

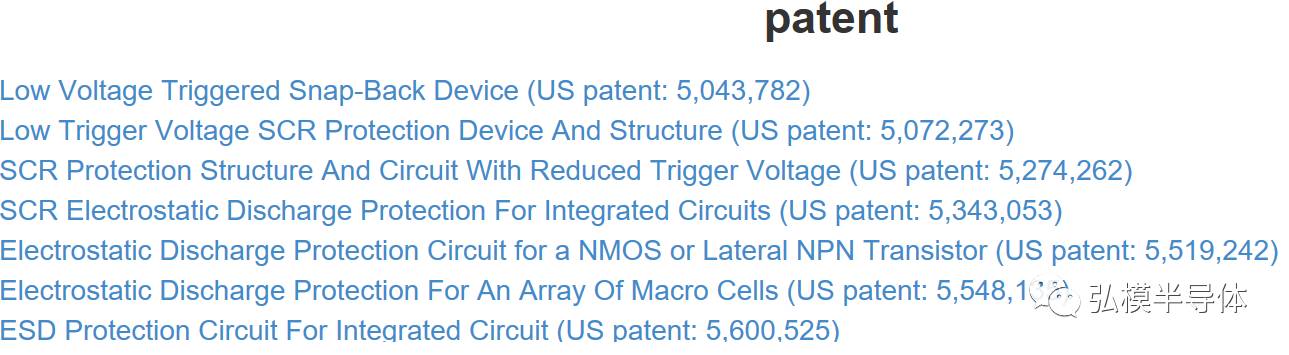

俗話說(shuō),打鐵還需自身硬,在這個(gè)方面,Sofics 是個(gè)典型的例子。 他們從不吝嗇用每年收入的10%左右來(lái)進(jìn)行技術(shù)開(kāi)發(fā),目前擁有在ESD方面的專利有75個(gè)之多,下面只是一些例子,這些專利成為了支持Sofics 快速成長(zhǎng)的堅(jiān)實(shí)基礎(chǔ)。

3. 商業(yè)模式:

Sofics 主要采用ESD IP,EDA SOFTWARE的授權(quán)模式。合作伙伴主要是半導(dǎo)體廠和設(shè)計(jì)公司。回顧半導(dǎo)體業(yè)界的高通,很多營(yíng)業(yè)收入也來(lái)自于IP的收入。這個(gè)在相當(dāng)長(zhǎng)的時(shí)間內(nèi),對(duì)公司的總體收入來(lái)說(shuō)是非常健康的模式,如果單純靠項(xiàng)目,或者服務(wù),自身成本會(huì)很高,同時(shí)受外來(lái)影響比較大。而IP一但在某個(gè)半導(dǎo)體廠被某個(gè)客戶成功應(yīng)用,接下來(lái)就可以給很多客戶應(yīng)用,屬于一段時(shí)間內(nèi)一勞永逸的事情。當(dāng)然,在國(guó)內(nèi)商業(yè)環(huán)境下,IP公司經(jīng)常碰到很多壁壘,因?yàn)樾袠I(yè)方面不是在市場(chǎng)選擇對(duì)的,而是更多偏向于選擇內(nèi)部自己圈子的資源。所以,打造健康商業(yè)環(huán)境,短期來(lái)看對(duì)國(guó)外的IP公司有利,長(zhǎng)期來(lái)看對(duì)國(guó)內(nèi)更多設(shè)計(jì)公司是件好事情,因?yàn)樗麄冇懈嗍杖雭?lái)支持科研開(kāi)發(fā),而不是面對(duì)抄襲,盜版讓公司面臨迅速衰落,生存的問(wèn)題。

4. 質(zhì)量體系和口碑:

在半導(dǎo)體產(chǎn)業(yè)界,口碑是一個(gè)企業(yè)的生命。Sofics 的客戶遍布世界各地,服務(wù)于各大半導(dǎo)體廠和設(shè)計(jì)公司,覆蓋了模擬設(shè)計(jì),數(shù)字設(shè)計(jì),汽車(chē)電子設(shè)計(jì),硅光電,高頻,高壓等各個(gè)方面。

我們來(lái)看看來(lái)自客戶們的評(píng)價(jià),也許這個(gè)很好解釋了Sofics 取得成功的真正原因:

eSiliconSofics: “delivered it in just two weeks” Sofics' PowerQubic technology offered a great solutionPowerQubic protects a 15V interface on a 0.18um high-voltage LDMOS chip2012: Sofics PowerQubic Technology Used by eSilicon to Protect High-Voltage Solar Panel IC from Electrical Overstress

Nvidia:Interface with legacy components in smartphones and tablets, such as SIM cards and memory cards.Sofics and ICsense came up with a solution that works at high voltages and provides good ESD protection.Enables off-chip interfaces (in 40nm and 28nm) of up to 3.6 volts.2012 press release with Nvidia and ICsense

RUAGESD: doctor gives clients access to our full range of expertise in identifying, diagnosing, and solving ESD and EOS (electrical overstress) problems quickly and definitively2012: Sofics ESDdoctor Debugging Improves ESD Protection on Rad-Hard Ics

ZMDI (now IDT):PowerQubic clamps were superior in the EMC test, as well as in parameters such as meeting flexible clamping voltage specifications.We selected Sofics to provide ESD/EOS protection for a new line of 0.18um devicesmeet our specifications, at a lower cost than building the clamps from scratch 2013: ZMDI Licenses Sofics PowerQubic ESD Clamps to Meet Automotive EMC Requirements on 0.18um 24V Chips

中國(guó)半導(dǎo)體產(chǎn)業(yè)如火如荼,每年都有很多新的企業(yè)加入,也許Sofics 的成功之路能給你帶來(lái)一些提示,公司不在于大,在于有自己的核心價(jià)值,在于健康的商業(yè)模式,在于合適的切入點(diǎn),那么你的公司離成功不遠(yuǎn)了。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27719瀏覽量

222699 -

模擬設(shè)計(jì)

+關(guān)注

關(guān)注

1文章

55瀏覽量

18482 -

數(shù)字設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

47瀏覽量

22324

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ESD對(duì)于電子器件的破壞機(jī)理分析

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(三)集成電路ESD 測(cè)試與分析

ESD測(cè)試|靜電放電抗擾度測(cè)試必備神器!#ESD測(cè)試 #靜電抗干擾測(cè)試 #電路知識(shí) #電子工程師

ESD二極管特點(diǎn)優(yōu)勢(shì)有哪些?

求助,關(guān)于LM386芯片內(nèi)ESD保護(hù)電路設(shè)計(jì)和引腳分配情況求解

ESD保護(hù)電路POWERclamp原理

Victor Labián Carro:以好奇心成就 RISC-V 職業(yè)成功之路

淺談半導(dǎo)體芯片失效分析Analysis of Semiconductor Chip Failure

如何將GPIO16連接到CHIP_PD以獲得深度睡眠模式?

ESD的3種模型和RF PA ESD保護(hù)方案介紹

關(guān)于On-chip ESD 公司的成功之路分析和介紹

關(guān)于On-chip ESD 公司的成功之路分析和介紹

評(píng)論