大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來聊一聊基于FPGA的異步FIFO的實(shí)現(xiàn)。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,它與普通

2018-06-21 11:15:25 6164

6164

FIFO是隊(duì)列機(jī)制中最簡單的,每個(gè)接口上只有一個(gè)FIFO隊(duì)列,表面上看FIFO隊(duì)列并沒有提供什么QoS保證,甚至很多人認(rèn)為FIFO嚴(yán)格意義上不算做一種隊(duì)列技術(shù),實(shí)則不然,FIFO是其它隊(duì)列的基礎(chǔ)

2022-07-10 09:22:00 1338

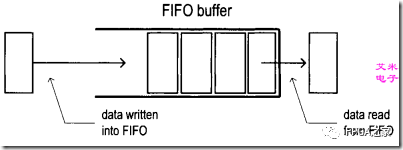

1338 FIFO緩存是介于兩個(gè)子系統(tǒng)之間的彈性存儲器,其概念圖如圖1所示。它有兩個(gè)控制信號,wr和rd,用于讀操作和寫操作。

2023-09-08 09:06:18 237

237

一種簡單有效的限流保護(hù)電路的設(shè)計(jì)

2012-08-20 16:00:03

前言:本文旨在介紹一種簡單的介質(zhì)波導(dǎo)雙模濾波器設(shè)計(jì)方法,用以指導(dǎo)濾波器工程師設(shè)計(jì)基站介質(zhì)波導(dǎo)濾波器。

2019-06-25 06:25:12

一種簡單的報(bào)錯(cuò)設(shè)計(jì),可在次基礎(chǔ)上增加。

沖突

阻擋

重復(fù)

不在工位

不在崗

計(jì)時(shí)不準(zhǔn)

范圍外

強(qiáng)停

其它

2023-05-20 20:07:57

一種簡單的激勵(lì)電壓放大電路的設(shè)計(jì)設(shè)計(jì)需求設(shè)計(jì)方案仿真結(jié)果設(shè)計(jì)需求設(shè)計(jì)方案仿真結(jié)果

2021-11-11 08:37:53

逆變器輸出直流分量會對逆變器本身和交流負(fù)載產(chǎn)生不利影響,必須消除直流分量來保障逆變器的可靠運(yùn)行。提出了一種簡單的消除輸出直流分量的方法,并在理論分析的基礎(chǔ)上,通過對1臺220V、1 kW的逆變器系統(tǒng)

2011-12-27 11:20:07

本帖最后由 病友來看病 于 2017-7-11 23:13 編輯

SRAM是各種memory(SDRAM,DDR1/2/3/4, LPDDR/2/3/4)中最昂貴的一種存儲方案, 高速SRAM

2017-07-05 22:08:17

摘要:本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統(tǒng)的硬件設(shè)計(jì)方案及設(shè)計(jì)要點(diǎn)的分析。該設(shè)計(jì)采用Altera公司的新一代FPGA芯片EP1C12和PCI IP核以及高速串行

2012-11-28 15:38:05

有效數(shù)據(jù)的條件下又必須控制電腦眼,會使得圖像的傳輸速率降。是一種可用但不最佳的方法。電腦眼基于外接RAM的單片方案,雖然在電路上比接FIFO稍顯復(fù)雜,但此方案解決了數(shù)據(jù)傳輸?shù)耐暾?而且能保持電腦眼

2019-06-17 05:00:02

描述直流到直流升壓轉(zhuǎn)換器版本 1它是一種直流到直流升壓轉(zhuǎn)換器。我聲明所有信息都是真實(shí)且可操作的。

2022-08-01 07:15:35

一種節(jié)省能源的簡單方法是在晚上關(guān)閉Mac。與不活動(dòng),空閑或睡眠的Mac相比,關(guān)機(jī)的Mac所消耗的能源更少。對于運(yùn)行大量Mac的組織,應(yīng)優(yōu)先考慮整夜關(guān)機(jī)。反對在夜間關(guān)閉的一個(gè)常見論點(diǎn)是關(guān)閉和啟動(dòng)所花

2021-12-29 08:20:46

【作者】:孟曉烜;司成祥;那文武;許魯;【來源】:《小型微型計(jì)算機(jī)系統(tǒng)》2010年03期【摘要】:針對存儲系統(tǒng)中的緩存管理單元設(shè)計(jì)一種區(qū)分應(yīng)用優(yōu)先級的緩存回收策略,簡稱PARP.該策略基于分區(qū)緩存

2010-04-24 09:43:47

使用ASP中的緩存技術(shù)可以很大程度上提高你的網(wǎng)站性能,其實(shí)這些實(shí)現(xiàn)方法是非常的簡單,它將說明如何在服務(wù)器上的緩存是如何工作以及你如何使用一種被稱為斷開連接的ADO連接技術(shù)。在介紹這些技術(shù)之前

2011-11-21 10:53:41

跪求MSP430F5229控制OV7670帶FIFO緩存的程序

2021-04-26 23:20:21

Linux下DNS緩存實(shí)現(xiàn)通常有兩種方式:一種是用DNS緩存程序NSCD(name service cache daemon)負(fù)責(zé)管理DNS緩存。

2019-07-25 07:53:46

還是可行的,在這里發(fā)出來跟大家討論一下,本人水平有限,錯(cuò)誤不當(dāng)之處在所難免,歡迎大家拍磚{:soso_e113:} 首先將芯片UART的FIFO啟用,并將其設(shè)置為最大14個(gè)字節(jié)(最大只能設(shè)置為14個(gè)字

2011-11-24 20:35:32

為什么要選擇一種相位序列指示器?求解

2021-06-08 10:43:29

時(shí)序一 什么是FIFOFirst In First Out ,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其

2021-12-27 08:05:35

入的指令先完成并引退,跟著才執(zhí)行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動(dòng)加1完成

2022-02-16 06:55:41

本設(shè)計(jì)實(shí)例介紹的是一種簡單的雙芯片CMOS電路。

2021-05-10 06:48:22

JSON。? 下面我將介紹一種簡單的數(shù)據(jù)解析方法,通過編寫函數(shù),將字符串解析取得目標(biāo)數(shù)據(jù)。解析字符型數(shù)據(jù)函數(shù)原型/*** @brief從一段字符串中解析期望的字符串* @parampBuff: 要解析的字符串地址* @parampLeft: 目標(biāo)字符串左邊的字符串* @

2022-02-28 06:15:11

本文介紹一種基于FIFO結(jié)構(gòu)的優(yōu)化端點(diǎn)設(shè)計(jì)方案。

2021-05-31 06:31:35

通過之前有關(guān)LSTM的8遍基礎(chǔ)教程和10篇處理時(shí)間序列預(yù)測任務(wù)的教程介紹,使用簡單的序列數(shù)據(jù)示例,已經(jīng)把LSTM的原理,數(shù)據(jù)處理流程,模型架構(gòu),Keras實(shí)現(xiàn)都講清楚了。從這篇文章開始,將介紹有關(guān)

2021-07-12 09:18:48

異步fifo是用于跨時(shí)域時(shí)鐘傳輸?shù)模峭?b class="flag-6" style="color: red">fifo做緩存我就不是很理解了,到底這個(gè)緩存是什么意思,這樣一進(jìn)一出,不是數(shù)據(jù)的傳輸嗎,為什么加個(gè)fifo,還有,如果是兩組視頻流傳輸,在切換的過程中如何能保證無縫切換?希望哪位好心人幫我解答一下

2013-08-27 19:23:36

本文介紹了nRF401的特點(diǎn),提出了一種將其應(yīng)用于無線集群語音傳輸系統(tǒng)的實(shí)現(xiàn)方案。此方案硬件電路簡單,易于調(diào)試,軟件編程也不復(fù)雜,是一種較好的設(shè)計(jì)思路。

2021-05-31 06:36:14

的一種基于大RAM的系統(tǒng)設(shè)計(jì):系統(tǒng)自舉是用簡單的明碼,其它代碼是加密后存儲在flash中。當(dāng)系統(tǒng)運(yùn)行時(shí),F(xiàn)lash中的數(shù)據(jù),解密后轉(zhuǎn)存到PSRAM中,程序從PSRAM中運(yùn)行,當(dāng)程序(或函數(shù))運(yùn)行結(jié)束時(shí)

2022-02-14 07:31:10

for循環(huán)中這樣做,但我想知道是否有一種更簡單(更快)的方法來清除RX FIFO中的數(shù)據(jù)。有一件事我還沒有測試是什么發(fā)生在FIFOS中的數(shù)據(jù)時(shí),SPI外圍設(shè)備被禁用,然后重新啟用。不幸的是,關(guān)于增強(qiáng)緩沖模式的文檔不是很廣泛…謝謝!

2019-09-16 10:00:09

如何去實(shí)現(xiàn)一種LED流水燈來回循環(huán)點(diǎn)亮的設(shè)計(jì)?其程序代碼該怎樣去寫?

2021-07-14 08:44:54

如何去實(shí)現(xiàn)一種基于AT89C51單片機(jī)的數(shù)碼管循環(huán)點(diǎn)亮0到9設(shè)計(jì)?

2021-10-19 08:54:07

如何去實(shí)現(xiàn)一種基于STM32f103的簡單自平衡小車設(shè)計(jì)呢?有哪些實(shí)現(xiàn)步驟?

2021-12-14 07:02:10

FCSR產(chǎn)生原理和序列特性是什么?如何去設(shè)計(jì)一種FCSR序列發(fā)生器?

2021-05-06 07:52:22

地SR只能容納8位(每個(gè)緩沖區(qū)的1個(gè)必要的結(jié)果),這意味著我必須將其中的4個(gè)鏈接以獲得必要的存儲……這實(shí)質(zhì)上導(dǎo)致3個(gè)額外的數(shù)據(jù)路徑組件無用-有一種方法可以將比較操作的布爾輸出存儲到FIFO1利用32位

2019-10-18 08:54:59

保持導(dǎo)通;當(dāng)信號消失,計(jì)時(shí)OP后斷開繼電器;計(jì)時(shí)期間,再有信號,計(jì)時(shí)清零;上面是網(wǎng)上的一種一路繼電器,可以不可以實(shí)現(xiàn)通電30秒后,吸合0.5秒再釋放,無需循環(huán)。這樣的一種操作是代替手指按一下按鈕的動(dòng)作。

2018-08-27 21:57:11

結(jié)合高速嵌入式數(shù)據(jù)采集系統(tǒng),提出一種基于CvcloneⅢ FPGA實(shí)現(xiàn)的異步FIFO和鎖相環(huán)(PLL)結(jié)構(gòu)來實(shí)現(xiàn)高速緩存,該結(jié)構(gòu)可成倍提高數(shù)據(jù)流通速率,增加數(shù)據(jù)采集系統(tǒng)的實(shí)時(shí)性。采用FPGA設(shè)計(jì)高速緩存,能針對外部硬件系統(tǒng)的改變,通過修改片內(nèi)程序以應(yīng)用于不同的硬件環(huán)境。

2021-04-30 06:19:52

想將一個(gè)序列循環(huán)輸出在波形圖中,類似于我的序列是123,波形圖就輸出123123123123~~~~~

2015-04-11 13:44:17

構(gòu)成高速緩存的方案有哪幾種?如何去實(shí)現(xiàn)一種海量緩存的設(shè)計(jì)?怎樣去實(shí)現(xiàn)一種基于DSP和ADC技術(shù)高速緩存和海量緩存?

2021-06-26 07:50:30

怎樣去搭建一種簡單的ESP-IDF環(huán)境呢?怎樣使用VSCODE進(jìn)行編譯Python呢?

2022-01-18 07:17:32

DNA計(jì)算模型可劃分為幾類?在DNA計(jì)算中的編碼問題是什么?怎樣去設(shè)計(jì)一種基于隨機(jī)產(chǎn)生實(shí)時(shí)過濾算法的DNA編碼序列?

2021-09-06 06:54:07

FIFO隊(duì)列是什么?怎樣去設(shè)計(jì)一種采用覆蓋機(jī)制的FIFO隊(duì)列模型呢?

2021-12-08 06:07:14

TMC5160芯片的特點(diǎn)是什么?TMC5160芯片有哪些優(yōu)勢?求一種基于STM32實(shí)現(xiàn)TMC5160簡單轉(zhuǎn)動(dòng)的方案

2021-07-06 06:56:26

求一種最簡單的無線充電發(fā)射端設(shè)計(jì)方案?有沒有大神分享一下這方面的相關(guān)資料啊

2021-07-21 08:15:55

求一種最簡單的電路,通電即導(dǎo)通,延時(shí)0.5秒左右后斷開。輸入電壓是AC220V,一通電就能使一個(gè)固態(tài)繼電器導(dǎo)通,延時(shí)約0.5秒左右后,再使固態(tài)繼電器斷開。最好是分立元件,越簡單越好。

2017-05-05 08:40:25

怎樣去設(shè)計(jì)一種基于單片機(jī)的簡單流水燈?如何編寫其程序?如何對基于單片機(jī)的簡單流水燈進(jìn)行Proteus仿真?

2021-07-19 09:05:19

本文介紹一種簡單易行的可編程振蕩器構(gòu)建方法,其中,振蕩頻率和幅度可以通過使用digiPOT來彼此獨(dú)立地調(diào)節(jié)。

2021-06-17 06:03:39

等等,認(rèn)為我在造謠言,可惜的我是農(nóng)民,沒資金沒人脈關(guān)系,要不然展示給你看,證明高手在民間。我說過一種電子加速器表面看簡單,如果你在一種電子加速器再纏繞一層結(jié)果毫無效果,所以一種電子加速器的山寨版是很難

2016-10-09 20:48:47

萌新求助,求一種簡單的MOS管直流電機(jī)驅(qū)動(dòng)電路

2021-10-19 06:49:59

萌新求助,求分享一種簡單的的H橋電路

2021-10-15 08:58:04

我現(xiàn)在就想實(shí)現(xiàn)往SCITXBUF里面寫一字節(jié),然后數(shù)據(jù)立馬發(fā)送出去,不需要觸發(fā)發(fā)送中斷。請問發(fā)送緩存FIFO里面應(yīng)該怎么設(shè)置?EALLOW; // Init_Bauud // Note

2018-09-19 09:39:02

本文僅使用一個(gè)D觸發(fā)器設(shè)計(jì)了一種結(jié)構(gòu)簡單,使用方便可靠的開/關(guān)機(jī)電路。

2021-04-12 06:48:36

為什么要設(shè)計(jì)一種異步FIFO?異步FIFO的設(shè)計(jì)原理是什么?怎樣去設(shè)計(jì)一種異步FIFO?

2021-06-18 09:20:29

數(shù)據(jù)采集板并行采樣0.1s將產(chǎn)生32MB的數(shù)據(jù)量,所以,通常需要海量緩存來存儲采樣數(shù)據(jù)。 2、高速緩存的實(shí)現(xiàn) 通常構(gòu)成高速緩存的方案有三種: 第一種是FIFO(先進(jìn)先出)方式。FIFO存儲器就象

2020-12-04 15:59:14

1.什么是FIFO?FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)

2009-07-22 16:00:48 0

0 該文提出一種新的最佳相關(guān)信號,即偽隨機(jī)屏蔽序列偶,研究了其變換性質(zhì)和組合允許條件,運(yùn)用這些性質(zhì)和條件可以縮小偽隨機(jī)屏蔽序列偶的搜索范圍,提高計(jì)算機(jī)搜索的效率。

2009-11-19 16:43:48 9

9 摘要:使用FIFO同步源自不同時(shí)鐘域的數(shù)據(jù)是在數(shù)字IC設(shè)計(jì)中經(jīng)常使用的方法,設(shè)計(jì)功能正確的FUFO會遇到很多問題,探討了兩種不同的異步FIFO的設(shè)計(jì)思路。兩種思路

2006-03-24 12:58:33 680

680

什么是fifo (First Input First Output,先入先出隊(duì)列)這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。1.什么是FIFO

2007-12-20 13:51:59 11835

11835 1 FIFO概述

FIFO芯片是一種具有存儲功能的高速邏輯芯片,可在高速數(shù)字系統(tǒng)中用作數(shù)據(jù)緩存。FIFO通常利用雙口RAM和讀寫地址產(chǎn)生模塊來實(shí)現(xiàn)其功能。FIFO的接口信號包括異步

2010-08-06 10:22:04 5019

5019

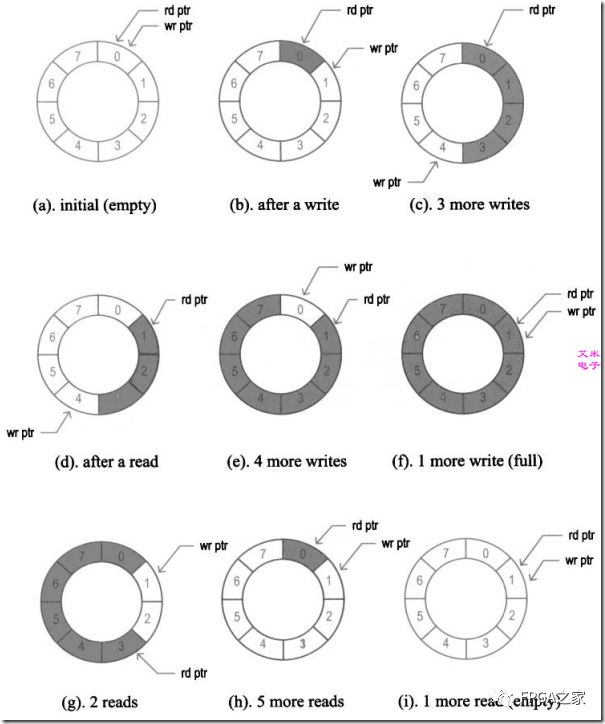

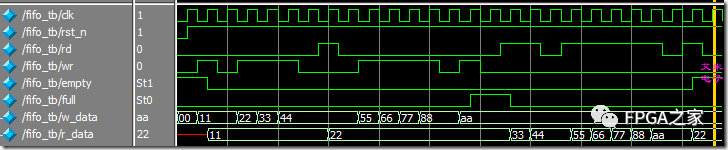

本文首先對異步 FIFO 設(shè)計(jì)的重點(diǎn)難點(diǎn)進(jìn)行分析,最后給出詳細(xì)代碼。 一、FIFO簡單講解 FIFO的本質(zhì)是RAM, 先進(jìn)先出 重要參數(shù):fifo深度(簡單來說就是需要存多少個(gè)數(shù)據(jù)) fifo

2017-11-15 12:52:41 7993

7993

Redis是一個(gè)key?value存儲系統(tǒng),通過對Redis高速緩存系統(tǒng)的序列化算法優(yōu)化,可提高緩存讀取的效率和存儲容量。引入現(xiàn)代統(tǒng)計(jì)學(xué)中Bootstrap理論,提出基于隨機(jī)相位高斯偽隨機(jī)數(shù)重排

2017-11-23 16:07:53 0

0 )片上集成的高速FIFO實(shí)現(xiàn)采集數(shù)據(jù)的高速緩存并通過對高速FIFO的讀寫操作實(shí)現(xiàn)總線同步數(shù)據(jù)傳輸,提高數(shù)據(jù)的傳輸速率。

2018-07-12 09:06:00 4707

4707

FIFO( First In First Out)簡單說就是指先進(jìn)先出。由于微電子技術(shù)的飛速發(fā)展,新一代FIFO芯片容量越來越大,體積越來越小,價(jià)格越來越便宜。作為一種新型大規(guī)模集成電路,FIFO芯片以其靈活、方便、高效的特性。

2017-12-06 14:29:31 10173

10173

。 循環(huán)碼是線性碼中的一類,在電子產(chǎn)品、數(shù)據(jù)傳輸技術(shù)、廣播系統(tǒng)有著廣泛的應(yīng)用。由于他們有著高效的編碼和解碼算法,在計(jì)算機(jī)中也有著廣泛的應(yīng)用。本文中,首先構(gòu)造了在GF (q)上周期為素?cái)?shù)胛的六階分圓序列,并且給出了序列的線性復(fù)

2017-12-12 19:13:15 0

0 渲染涉及大量的緩存,這里緩存只是一個(gè)簡單的存有像素?cái)?shù)據(jù)的矩形內(nèi)存塊,最重要緩存是幀緩存和深度緩存。

2018-05-14 11:44:45 5584

5584

FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動(dòng)加1完成,不能像普通存儲器那樣可以由地址線決定讀取或?qū)懭肽硞€(gè)指定的地址。

2018-07-20 08:00:00 22

22 配置FIFO的方法有兩種:

一種是通過QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中選擇FIFO參數(shù)編輯器來搭建自己需要的FIFO,這是自動(dòng)生成FIFO的方法

2018-07-20 08:00:00 17

17 1、初始化時(shí)開啟串口的空閑中斷,并且初始化為循環(huán)DMA。2、觸發(fā)空閑中斷時(shí),更新索引,這個(gè)索引表示當(dāng)前寫入索引值,用于上層判斷緩存空間已寫入的數(shù)據(jù)(魚鷹前面寫了關(guān)于循環(huán)FIFO的筆記,可自行查看

2020-06-24 11:28:59 3575

3575 FIFO是FPGA處理跨時(shí)鐘和數(shù)據(jù)緩存的必要IP,可以這么說,只要是任意一個(gè)成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時(shí)候,碰見幾個(gè)大坑,這里總結(jié)如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 多數(shù) NDMANET緩存策略研究未考慮內(nèi)容的優(yōu)先級,從而降低了重要內(nèi)容在節(jié)點(diǎn)移動(dòng)環(huán)境下的可用性。針對該問題,提出一種基于內(nèi)容優(yōu)先級的緩存替換策略PFC。根據(jù)節(jié)點(diǎn)內(nèi)容對可用性的不同需求劃分內(nèi)容優(yōu)先級

2021-03-24 14:48:43 9

9 1.定義 FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序

2021-04-09 17:31:42 4697

4697

數(shù)據(jù)緩存下來,那么我們需要開多大的空間緩存這些數(shù)據(jù)呢?緩存開大了會浪費(fèi)資源,開小了會丟失數(shù)據(jù),如何去計(jì)算最小FIFO深度是本文的重點(diǎn)。 本文涵蓋了FIFO最小深度計(jì)算所有情況: 假如模塊A不間斷的往FIFO中寫數(shù)據(jù),模塊B同樣不間斷的從FIFO中讀數(shù)據(jù)

2021-05-11 14:37:08 1950

1950

對時(shí)間序列和相關(guān)距離信息進(jìn)行建模,提取用戶訪問興趣點(diǎn)的偏好特征,并基于該特征對用戶進(jìn)行興趣點(diǎn)推薦。在真實(shí)數(shù)據(jù)集上進(jìn)行的實(shí)驗(yàn)結(jié)果表明,與傳統(tǒng)循環(huán)神經(jīng)網(wǎng)絡(luò)算法相比,該算法能夠覆蓋用戶訪問興趣點(diǎn)的長序列,推薦結(jié)果更

2021-05-13 16:19:36 6

6 First Input First Output的縮寫,先入先出隊(duì)列,這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令。是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別

2021-05-29 09:10:49 24294

24294 入的指令先完成并引退,跟著才執(zhí)行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,他與普通存儲器的區(qū)別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點(diǎn)就是只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動(dòng)加1完成

2021-12-17 18:29:31 10

10 FIFO最常被用來解決寫、讀不匹配的問題(時(shí)鐘、位寬),總結(jié)下來,其實(shí)FIFO最大的作用就是緩沖。既然是緩沖,那么就要知道這個(gè)緩存的空間到底需要多大。接下來的討論,都建立在滿足一次FIFO突發(fā)傳輸

2022-02-26 17:41:52 3045

3045

在FPGA中對圖像的一行數(shù)據(jù)進(jìn)行緩存時(shí),可以采用FIFO這一結(jié)構(gòu),如上圖所示,新一行圖像數(shù)據(jù)流入到FIFO1中,FIFO1中會對圖像數(shù)據(jù)進(jìn)行緩存,當(dāng)FIFO1中緩存有一行圖像數(shù)據(jù)時(shí),在下一行圖像數(shù)據(jù)來臨的時(shí)候,將FIFO1中緩存的圖像數(shù)據(jù)讀出,并傳遞給下一個(gè)FIFO

2022-05-10 09:59:29 3056

3056 我們即將學(xué)習(xí)的是:在Python中實(shí)現(xiàn)更簡單好用的函數(shù)運(yùn)算緩存。 函數(shù)運(yùn)算緩存,顧名思義就是我們可以針對指定的函數(shù),讓其記住過往參數(shù)輸入和返回結(jié)果,使得后續(xù)接收到相同的參數(shù)時(shí)跳過函數(shù)運(yùn)算,直接返回已緩存的結(jié)果值。

2022-08-05 11:05:34 722

722 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡稱,是一種先進(jìn)先出的數(shù)據(jù)緩存器,與普通存儲器的區(qū)別在于沒有外部讀寫的地址線,缺點(diǎn)是只能順序的讀取

2022-12-12 14:17:41 2790

2790 在 Python 中,for 循環(huán)是一種常用的結(jié)構(gòu),用于遍歷序列(如列表、元組、字符串)中的元素。

2023-04-19 15:45:51 1409

1409 今天咱們開始聊聊FIFO的設(shè)計(jì)。FIFO是一個(gè)數(shù)字電路中常見的模塊,主要作用是數(shù)據(jù)產(chǎn)生端和接受端在短期內(nèi)速率不匹配時(shí)作為數(shù)據(jù)緩存。FIFO是指First In, First Out,即先進(jìn)先出,跟大家排隊(duì)一樣。越早排隊(duì)的人排在越前面,輪到他的次序也越早,所以FIFO有些時(shí)候也被稱為隊(duì)列queue。

2023-05-04 15:48:20 544

544 FIFO 是FPGA設(shè)計(jì)中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機(jī)制,是設(shè)計(jì)人員將數(shù)據(jù)從一個(gè)模塊傳輸?shù)搅硪粋€(gè)模塊的常用選擇。

2023-06-14 08:59:29 223

223 FIFO(First In First Out)是一種先進(jìn)先出的存儲結(jié)構(gòu),經(jīng)常被用來在FPGA設(shè)計(jì)中進(jìn)行數(shù)據(jù)緩存或者匹配傳輸速率。

2023-08-07 15:39:50 446

446 FIFO緩存是介于兩個(gè)子系統(tǒng)之間的彈性存儲器,其概念圖如圖1所示。它有兩個(gè)控制信號,wr和rd,用于讀操作和寫操作。當(dāng)wr被插入時(shí),輸入的數(shù)據(jù)被寫入緩存,此時(shí)讀操作被忽視。FIFO緩存的head一般

2023-09-11 10:12:39 376

376

簡單的一種,其特點(diǎn)是輸入和輸出都與時(shí)鐘信號同步,當(dāng)時(shí)鐘到來時(shí),數(shù)據(jù)總是處于穩(wěn)定狀態(tài),因此容易實(shí)現(xiàn)數(shù)據(jù)的傳輸和存儲。 而異步FIFO則是在波形的上升沿和下降沿上進(jìn)行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數(shù)據(jù)的讀寫。異步FIFO的輸入和輸出可同時(shí)進(jìn)行,中間可以

2023-10-18 15:23:58 790

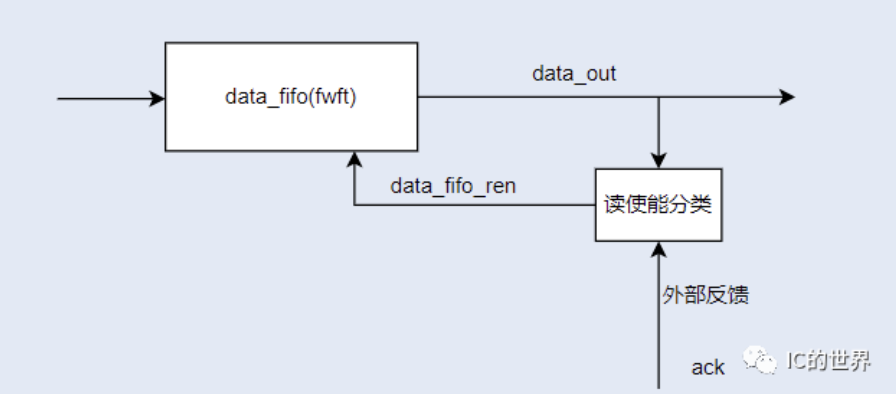

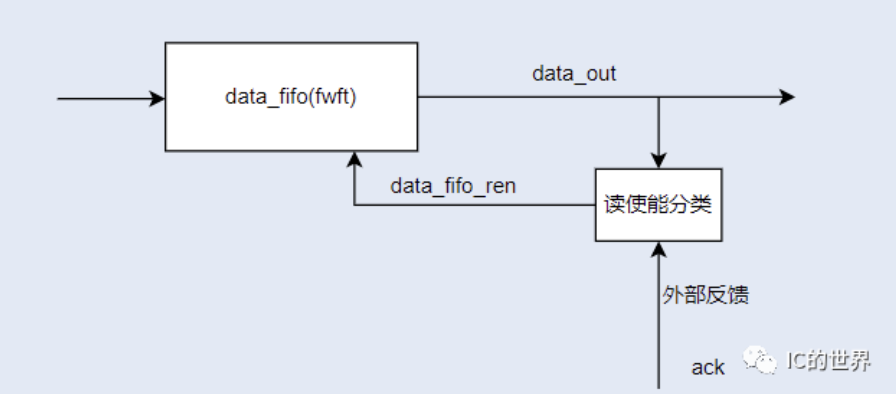

790 本文將簡述一種fifo讀控制的不合理設(shè)計(jì)案例,在此案例中,異常報(bào)文將會堵在fifo中,造成頭阻塞。

2023-10-30 14:25:34 159

159

Python是一種簡單而又強(qiáng)大的編程語言,通過其清晰的語法和豐富的功能庫,我們可以實(shí)現(xiàn)各種各樣的任務(wù)。其中一個(gè)最基本的語法結(jié)構(gòu)就是for循環(huán),讓我們來看一下如何使用for循環(huán)來編寫一個(gè)最簡單的例子

2023-11-21 14:53:39 352

352

電子發(fā)燒友App

電子發(fā)燒友App

評論