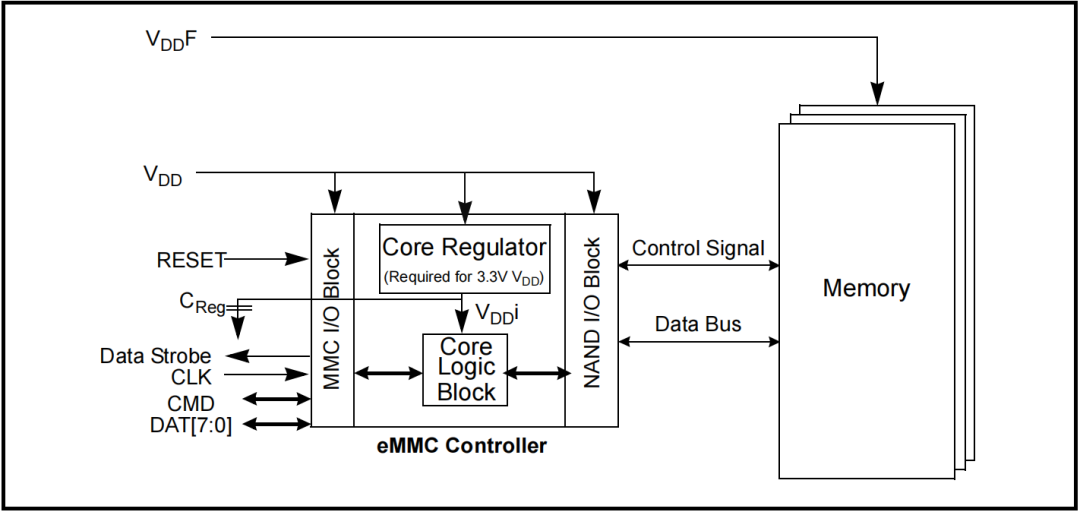

引言:因為MMC接口允許輕松地與任何微處理器與MMC主機集成,并且嵌入式MMC控制器將Nand技術與主機隔離,所以對Nand的任何修訂或修改對主機來說都是不可見的,也不需要關注,所有這些都實現了更快的產品開發和更快的上市時間。但要想實現eMMC的高可靠性,需要嚴格測試eMMC的信號質量,并滿足JEDEC發布的標準。

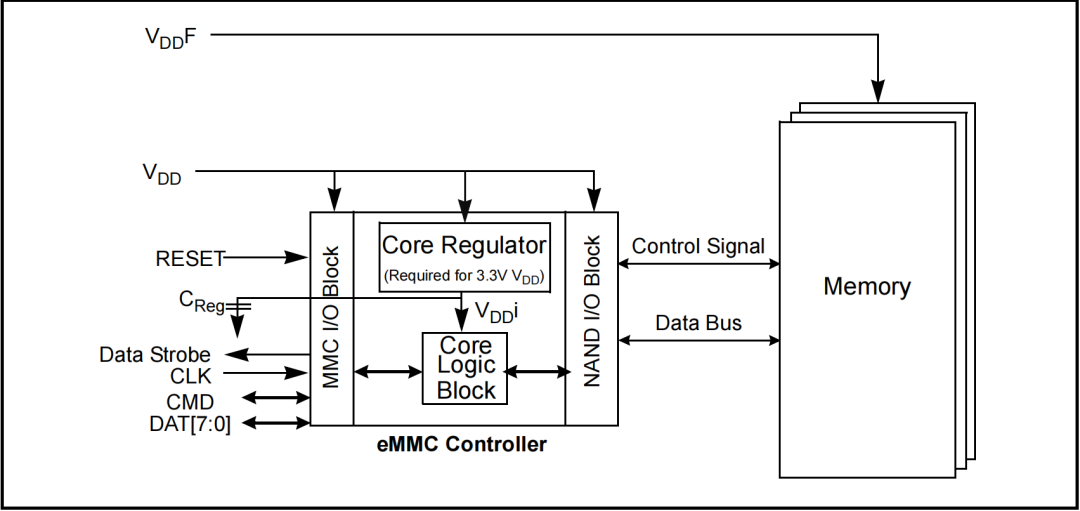

1.引腳

數據總線寬度:1位(默認)、4位和8位

MMC I/F 時鐘頻率:0 ~ 200MHz

MMC I/F 啟動頻率:0 ~ 52MHz

CLK:時鐘輸入

Data Strobe:HS400模式的新配值引腳,數據選通從eMMC生成到主機。在HS400模式下,讀取數據和CRC響應與數據選通同步

CMD:用于設備初始化和命令傳輸的雙向信號,命令操作有兩種模式,開漏進行初始化和推拉快速傳輸命令

DAT0-7:雙向數據通道,它以推拉模式運行

RST_N:H/W復位信號引腳

VDDF(VCC):提供閃存存儲器的電源電壓

VDD(VCCQ):存儲器控制器的電源電壓

VDDI:內部功率節點,以穩定調節器輸出到控制器的核心邏輯

VSS:接地連接

RFU:保留供將來使用,不要用作任何用途

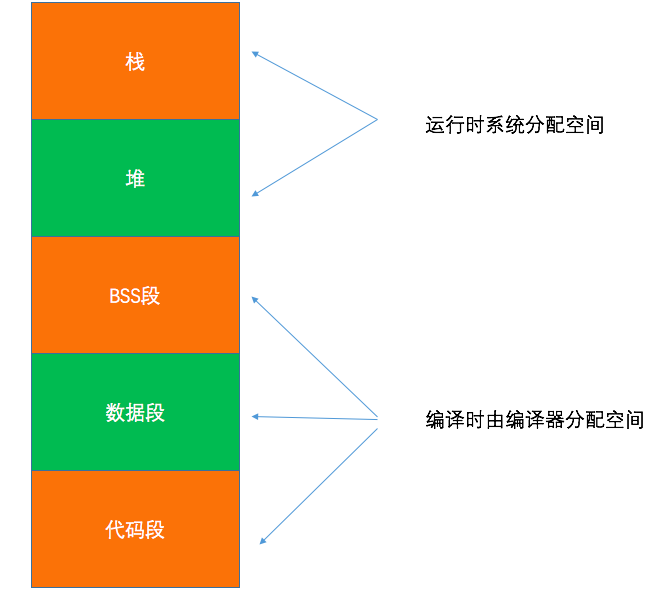

圖8-1:eMMC結構

2.傳輸模式和HS400 MODE

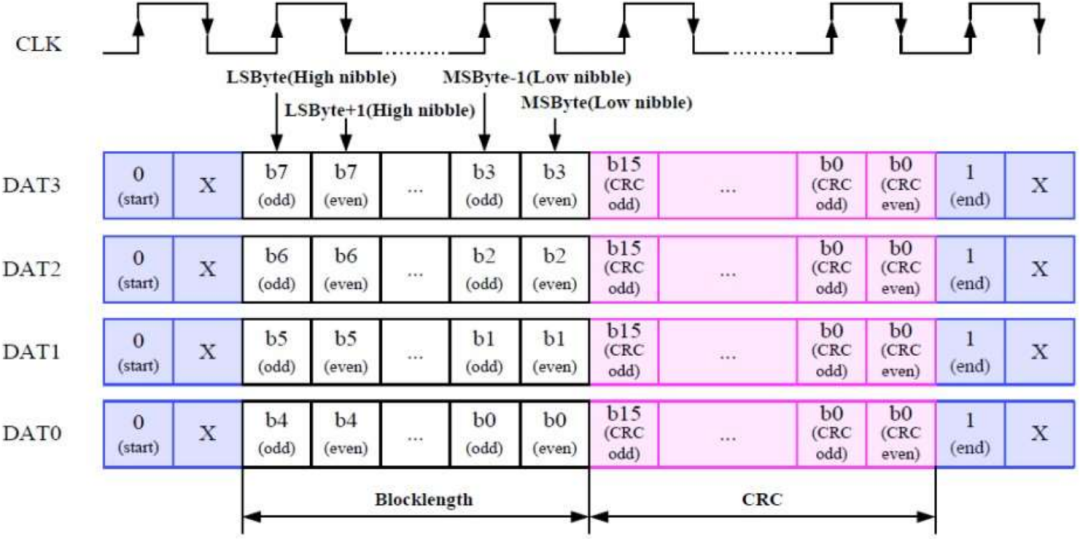

在時鐘的每個周期都會指示傳輸:在命令線上每個時鐘周期進行1位傳輸;在數據線上,SDR模式下所有數據線傳輸1位,DDR模式下所有數據線傳輸2位(分別在上升沿和下降沿),時鐘頻率可在最小和最大時鐘頻率之間變化(0-200MHZ)。

圖8-2:DDR狀態下的4-data-wire模式

HS400模式提高順序帶寬,特別是順序讀取性能,支持DDR數據采樣方法,CLK頻率最高可達200MHz,但只有8位的總線寬度可用,信號電平1.8V,理論上,讀取高達400MB/s,寫入200MB/s。

圖8-3:eMMC的總線速度模式

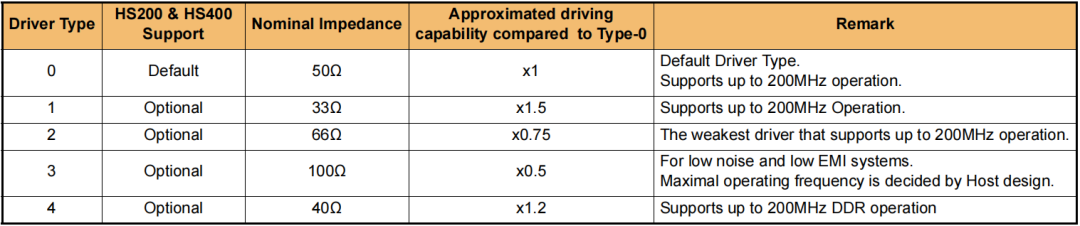

圖8-4表示I/O驅動程序強度類型(EXT_CSD寄存器:DRIVER_STRENGTH [197])

圖8-4:eMMC的HS400模式五種驅動強度

1#:HS200和HS400設備必須支持0型驅動程序。

2#:當VCCQ=1.8 V時,標稱阻抗由輸出驅動器在0.9 V時的I-V特性定義。

3#:當VCCQ=1.2 V時,標稱阻抗由0.6 V時輸出驅動器的I-V特性定義。

0型驅動程序被定義為eMMC HS200和HS400設備的強制性驅動程序,另有四個驅動程序類型(1、2、3和4)被定義為可選,以允許支持更廣泛的主機負載。主機可以選擇設備的最合適的驅動器類型(如果支持)以實現最佳信號完整性性能。

注:1.8V信號電平和1.2V信號電平的驅動強度定義相同。

0型驅動器適用于傳輸線,基于50Ω標稱線路的分布式系統阻抗,因此,它被定義為50Ω標稱驅動器。

對于HS200,當使用CL=15pF驅動器進行測試時,0型驅動器應滿足所有交流特性

對于HS400,當使用JESD84-B51中定義的參考負載、驅動器類型0或驅動器類型1或4型驅動器應滿足所有交流特性和HS400設備輸出。

如果設備支持可選的驅動程序類型,主機可以使用它們來優化其系統,因此主機設計者可以使用設備驅動程序模型來模擬其特定系統。主機可以選擇最佳驅動程序類型,該類型可以以所需的操作頻率驅動主機系統負載產生最小的噪聲,這一點在優化信號質量和EMC方面特別有效。

Driver_STRENGTH[197]中指出了設備支持的驅動程序類型級別擴展CSD寄存器的字段。主機通過將(通過CMD6)寫入擴展CSD寄存器的HS_TIMING[185]字節中的“選定驅動器強度”字段。

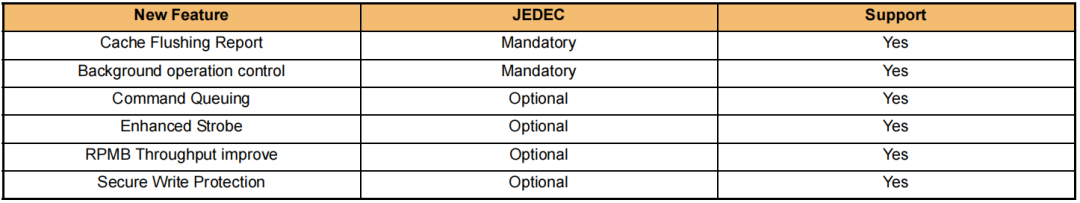

圖8-5列舉了eMMC5.1新功能:

圖8-5:eMMC5.1功能

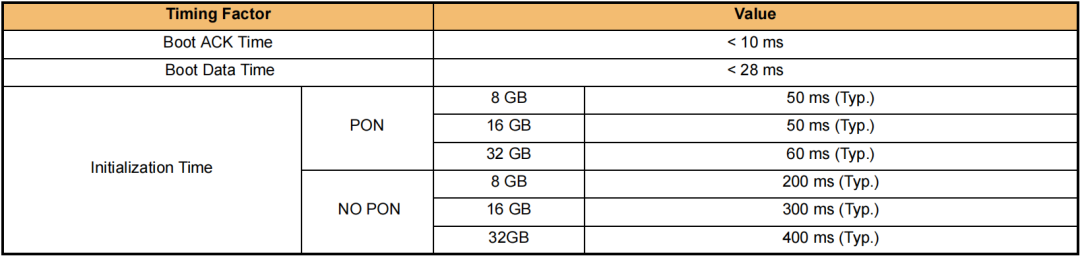

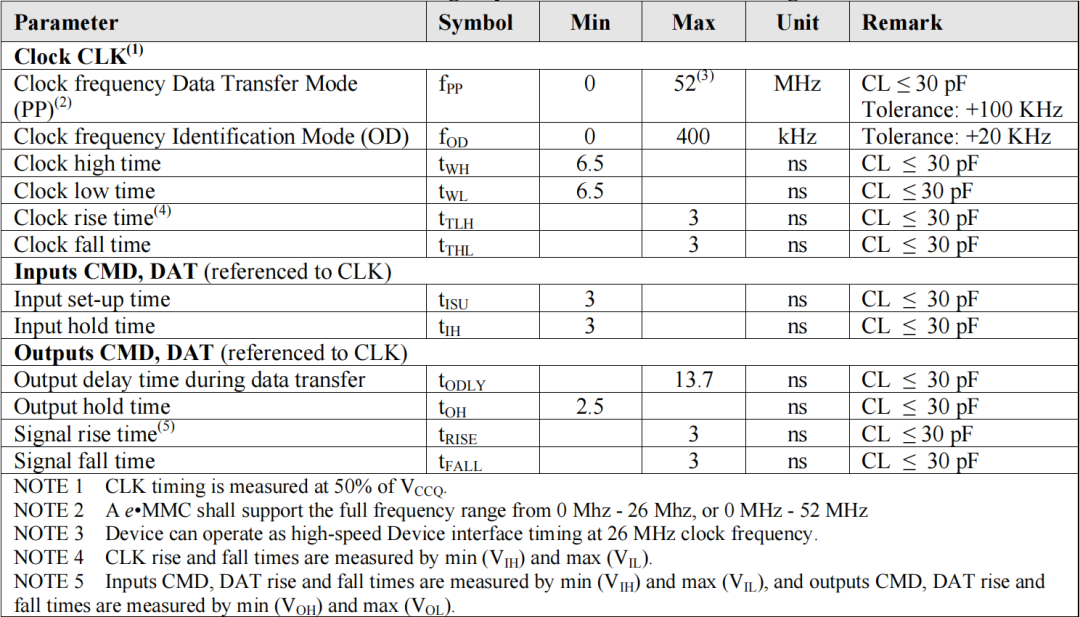

3.啟動時長

eMMC不僅支持引導模式,而且還支持替代引導模式,支持高速定時和雙數據速率。eMMC啟動時間軸回看:Digital series-Storage-7:eMMC基礎知識-2。

圖8-6:啟動程序、啟動數據和初始化時間

圖8-7:eMMC的性能指標

圖8-7是在測試條件:總線寬度x8,HS400,512KB數據包傳輸下實測的eMMC順序讀取和順序寫入的速度。

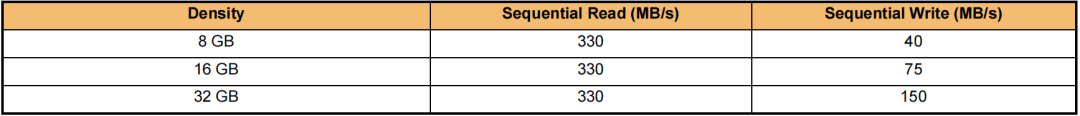

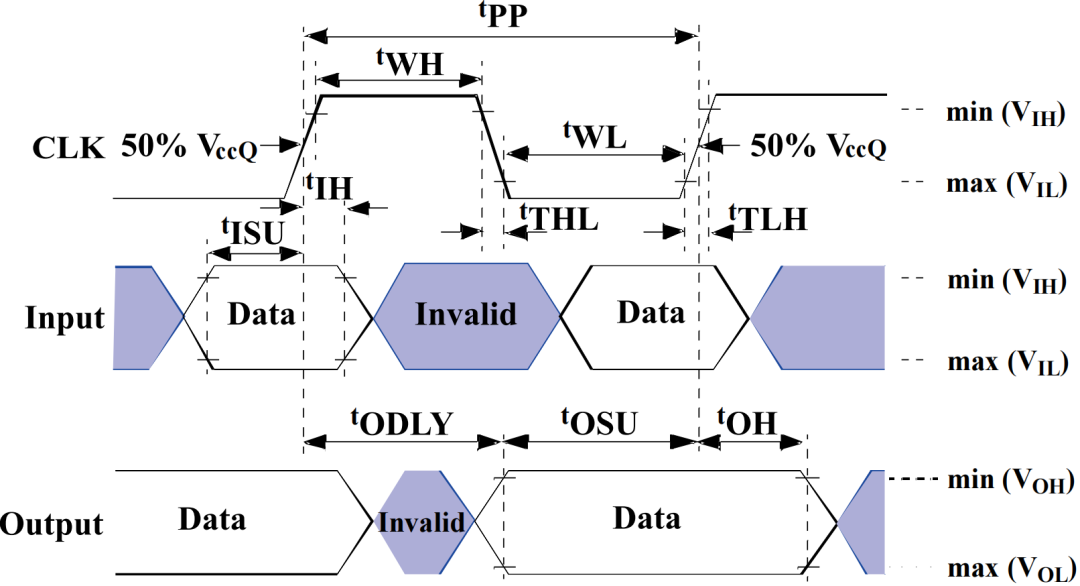

4.時序

圖8-8:總線SDR時序---數據必須始終在時鐘的上升邊緣進行采樣

圖8-9:總線SDR時序參數要求

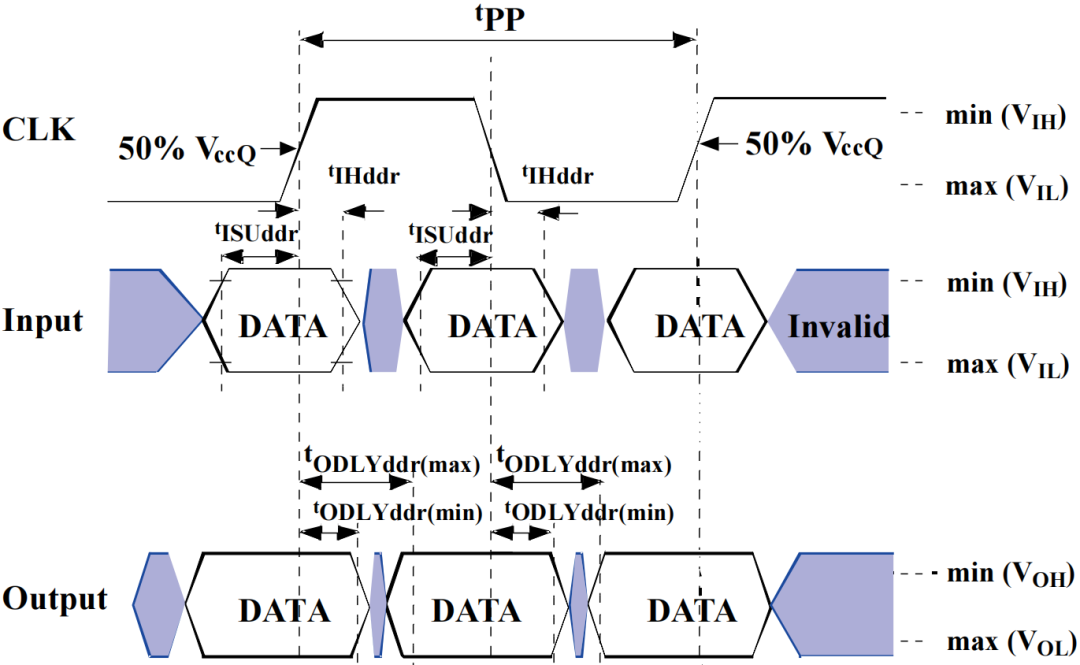

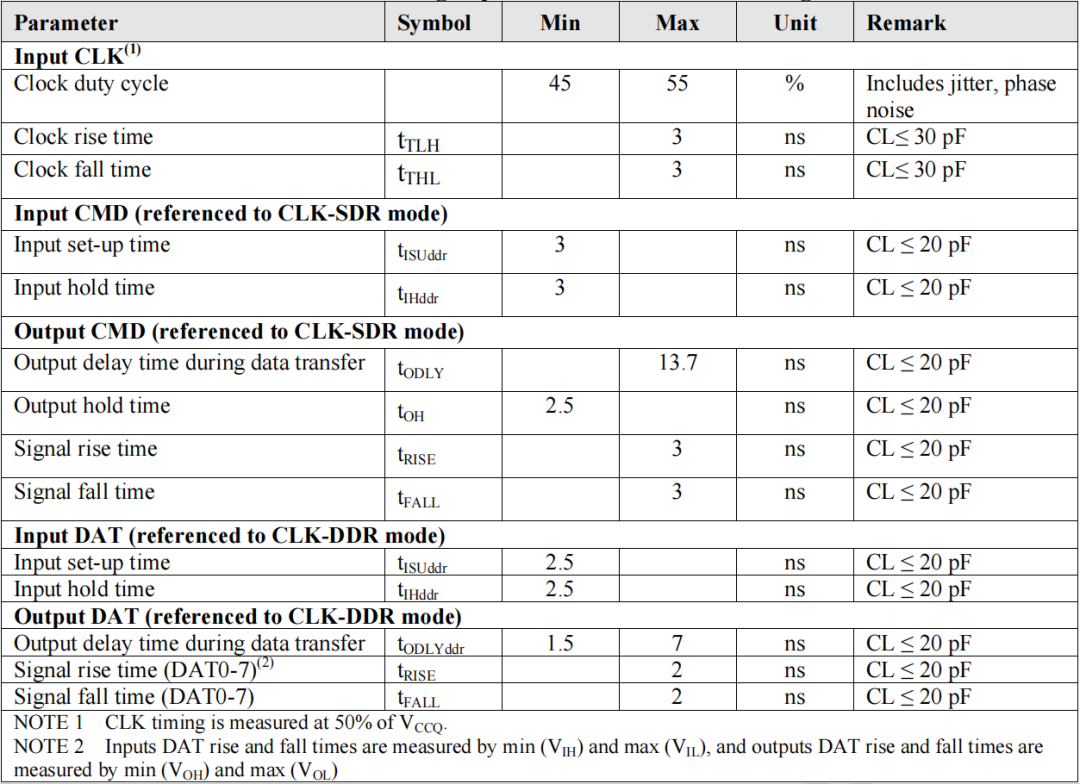

在配置為雙數據模式操作時的DAT[7:0]信號,DAT信號與CLK的上升邊緣和下降邊緣同步運行。CMD信號仍然與CLK的上升邊緣同步運行,因此CMD信號沒有定時變化。

圖8-10:總線DDR時序---DAT[7:0]行上的數據在時鐘的兩邊進行采樣

圖8-11:總線DDR時序參數要求

如上只是SDR/DDR時序,關于HS400等等模式下的總線定時規范,可以參閱eMMC v5.1的JEDEC官方權威文檔JESD84-B51。

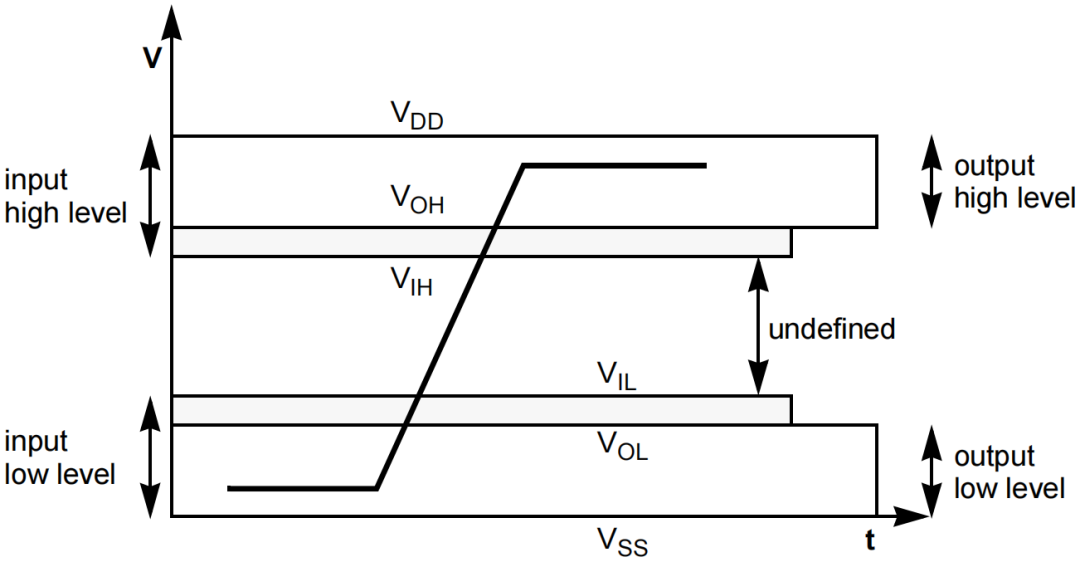

5.總線電平

總線信號電平,部分器件總線供電支持3.3V或者1.8V,因此所有的信號電平都與電源電壓有關。

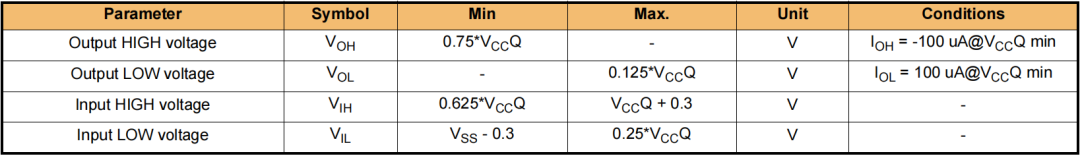

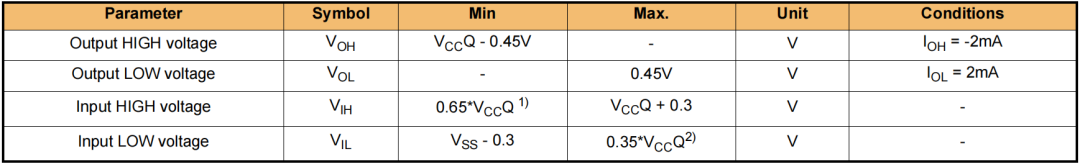

圖8-12:總線信號電平上下閾值

圖8-13:開漏模式總線信號電平

由于Voh取決于外部電阻值(包括軟件包外部),因此此值不適用于設備規范。主機負責選擇外部上拉和開漏電阻值,以滿足Voh最小值。

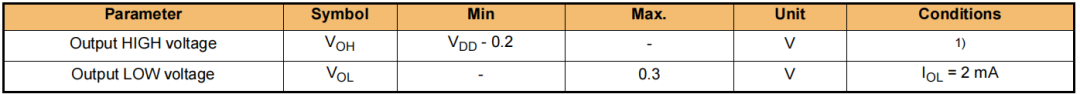

eMMC輸入和輸出電壓的允許電壓范圍應在以下規定范圍內:

圖8-14:推拉信號電平-3.3V eMMC

圖8-15:推拉信號電平-1.70-1.95 VCCQ電壓范圍

其中0.7×VCCQ,適用于MMC4.3及更舊版本,0.3×適用于MMC4.3及更舊版本的0.3×VCCQ。

6.功耗

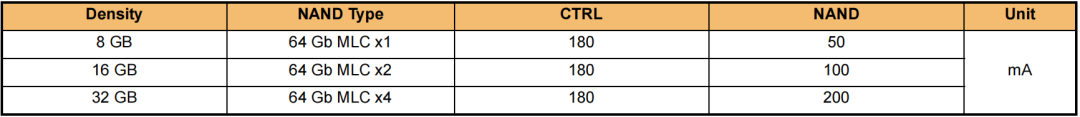

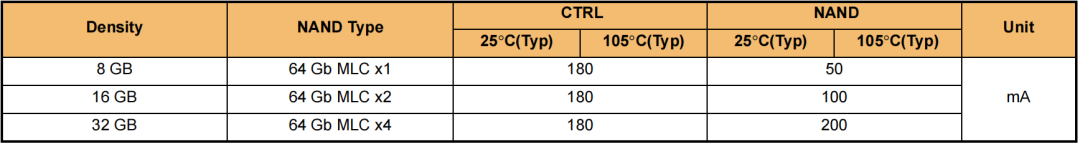

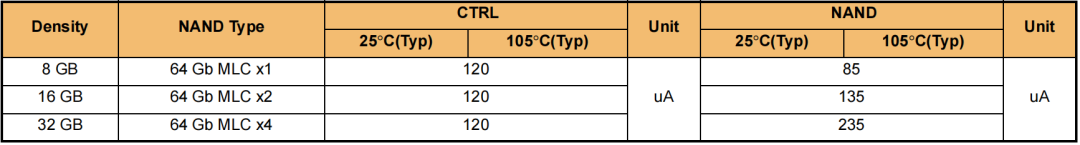

在配置系統電源樹時,eMMC的功耗是一個需要考慮的點,在功率測量條件:總線配置=x8@200MHz DDR最大RMS電流的測量為100ms周期內的平均RMS電流消耗下,eMMC各種狀態下的功耗如下:

圖8-16:不同容量eMMC運行期間的典型功耗

從圖8-16可知,eMMC容量越大,運行功耗越高,一個32GB的eMMC,考慮3.3V供電,則功耗P=3.3×0.38=1.254W,那么就需要選擇滿足可以持續輸出400mA的電源IC。

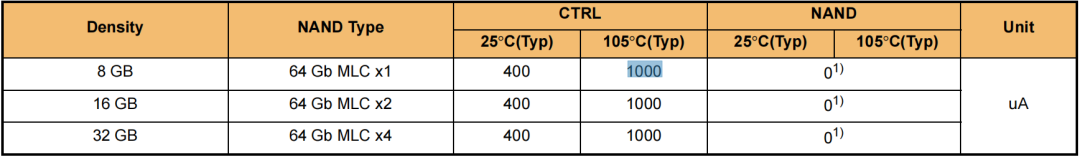

圖8-17:不同容量eMMC待機狀態下的典型功耗(巡檢讀取激活)

圖8-18:不同容量eMMC待機狀態下的典型功耗(巡檢讀取失能)

圖8-19:不同容量eMMC睡眠狀態下的睡眠功耗

注意在睡眠模式下,Nand電源可以關閉,如果Nand電源被激活,則Nand電源與待機狀態相同。

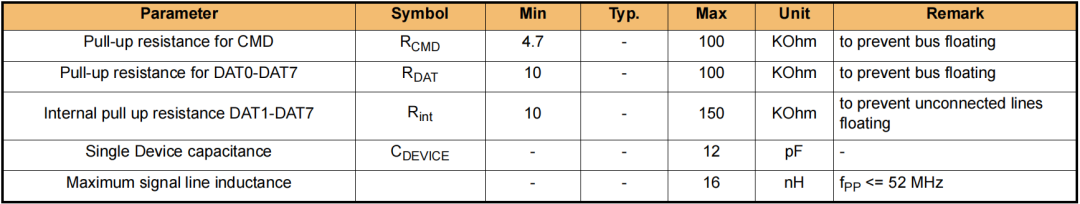

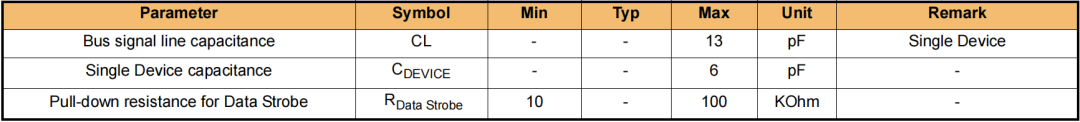

7.總線信號線負載

eMMC總線的每條線路的總電容CL為總線主電容CHOST、總線電容CBUS本身和與該線路連接的eMMC的電容器件之和:

主機和總線電容之和應在20pF以下,這幾個參數對eMMC的Layout有比較嚴格的要求。

圖8-20:eMMC關鍵R/C參數

圖8-21:HS400模式下的電容和電阻

8.如何在系統板上連接eMMC

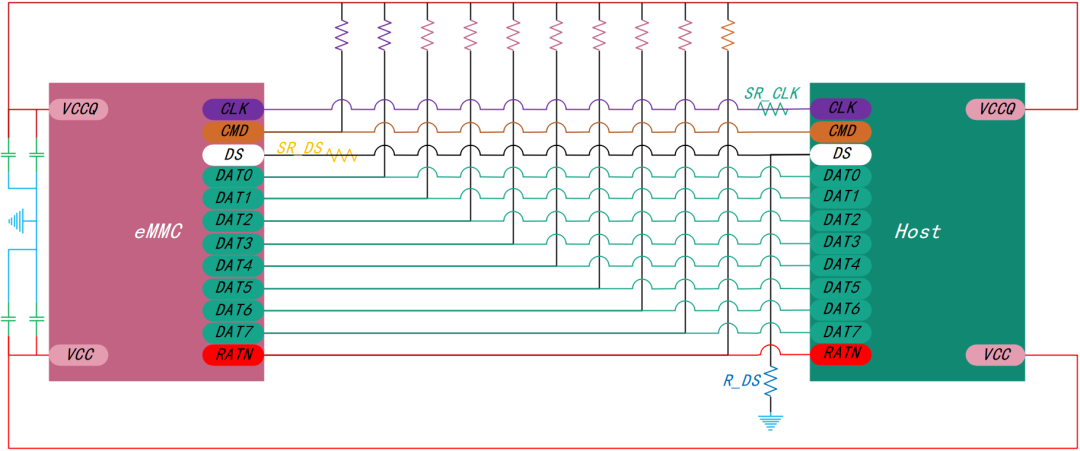

圖8-22:eMMC互連示例

1#:利用去耦電容濾除VCC/VCCQ電源噪聲

2#:CMD和DATA[7:0]始終通過系統板上的電阻進行上拉,以防止總線浮動

3#:如果總線使用H/W復位,RSTN也上拉

4#:SR_DS和SR_CLK采用串聯電阻穩定信號

電子發燒友App

電子發燒友App

評論