在高速電路設計中,中國設計工程師通常不是特別了解連接器的互感特性在改進信號完整性設計中的作用,本文將探討連接器設計和選擇中最難解決的問題:并發開關噪聲,并且揭示并發開關噪聲對高性能系統中使用的連接器和封裝規格指標的影響。

人們總是認為系統中所有的工作都是由IC來完成的,當然也包括相應的軟件。而類似于IC封裝、電路板、連接器、電纜以及其它的離散元器件等無源器件只會降低系統性能,擴大系統尺寸和增加系統成本。所以,系統中互連以及元器件的選擇和設計實際上就是將這些成分對系統造成的影響降到最低。因此大多數的IC 設計師通常將系統中不連接的所有部分(這通常是PCB設計師所涉及的內容)歸結為寄生成分這樣一個籠統的范疇。

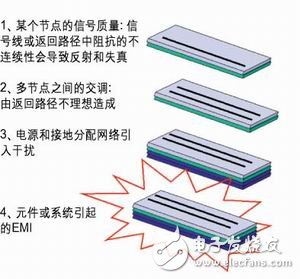

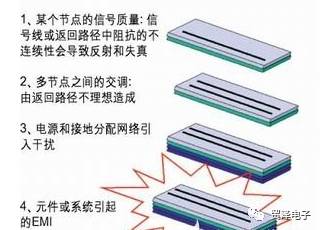

圖1:四種最主要的高速電路問題

選擇IC器件時,除了選擇合適的元器件以外,后續的電路板布局布線工作還要符合下列設計規則:

1. 受控阻抗的PCB線;

2.分支線上的信號延時小于最快信號上升時間的20%;

3. 不連續性時間延時小于最快信號上升時間的20%;

4.相鄰PCB線具有足夠的間距,確保信號串擾控制在可以接受的電平上;

5. 合理的PCB分層設計確保相鄰的電源和地平面層之間的介質很薄;

6.每一個信號線下面都有連續的信號返回路徑。

即便PCB的布局布線做得非常好,事情仍然沒有那么簡單。高性能系統中的每一個成分都需要優化,確保符合整個系統在成本、性能和開發進度等方面的要求。高性能的系統設計是一個環環相扣的鏈,每一個環節都必須符合要求,方能保證整個系統符合產品性能規范。

系統中的其它因素將如何影響系統性能?可能的問題通常可以歸結為兩種類型:時序問題和噪聲問題。信號完整性既包括時序問題也包括噪聲問題,然而噪聲問題更顯突出。

圖1所示為互連和元器件導致的信號完整性問題的四種類型:

1. 單根網絡的信號質量;

2. 兩根或者更多網絡之間的信號串擾;

3. 電源分布系統中的噪聲;

4. 系統中元器件對外的電磁輻射。

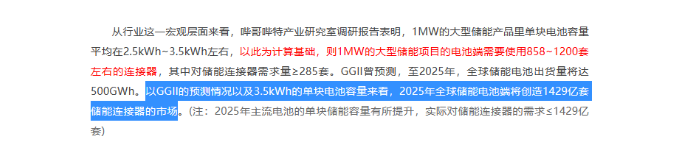

除非特別關注,并且項目一開始就著手考慮了這些問題,否則上述四種類型的問題就會出現在高速產品中。本文將探討連接器(也包括IC封裝)的設計和選擇中最難解決的問題:并發開關噪聲(simultaneously switchingnoise),并且揭示并發開關噪聲對高性能系統中使用的連接器和封裝規格指標的影響。并發開關噪聲

對連接器和IC封裝來說,開關噪聲方面的高速性能要求是最難滿足的。開關噪聲屬于信號串擾,主要是由于連接器和IC封裝中相鄰環路(由信號與返回路徑構成)之間的互感導致的。要使開關噪聲幅度最小,必須確保相鄰的信號路徑環路之間的互感小于一個允許的最大值。

圖2:測量BGA封裝中的并發開關噪聲。

當信號通過連接器或者IC封裝傳播時,信號的波前(信號波形中跳變的成分)通過信號管腳構成一個電流環路,就會耦合并且返回到信號的返回管腳上。每一個信號和對應的返回路徑都可以構成一個相似的環路。在任何兩個信號及其返回路徑構成的環路之間都存在一個環路互感。

一個環路中的電流發生變化時,就會在另外一個靜止(信號電流沒有變化)的環路中感應出信號噪聲。而當多個變化的信號線并發開關時,通過互感耦合到靜止環路的噪聲就會互相累計,因此稱為“并發開關噪聲”。圖2所示為五個數據線并發開關時測量到的一個靜止信號線上的并發開關噪聲。在這個實例里,靜止信號線上的噪聲是由該靜止環路與所有五個變化的環路之間的互感而造成的。

互感的計算

采用簡單的模型可以很方便地估算出兩個信號環路之間允許的最大互感值。進一步討論如何計算實際連接器中相鄰環路之間的互感。

當信號通過連接器的一個管腳對時,在變化的信號通路上,信號的波前處會出現信號電流的突然變化。變化的電流會導致電壓噪聲并且感應到相鄰的靜止信號環路上,這種感應是由于兩個環路之間存在的互感引起的。這種靜止信號線上感應出來的噪聲稱之為開關噪聲,這是由于這種噪聲只有當電壓或者電流處于開關狀態時才會出現。

在靜止環路中感應出的電壓噪聲可以近似為:

表達式各項的意義為:Vn,靜止環路中的噪聲;Lab,變化環路和靜止環路之間的互感;△Ia,變化環路中的電流變化;Za,在變化環路與靜止環路的視在阻抗;Va,變化環路中的信號電壓;△t是信號的上升時間,表明電流開關的快慢。

選擇連接器或者IC封裝唯一可以影響的就是環路之間的互感,而環路中信號視在阻抗通常都在50歐姆左右,該阻抗值與上升時間及信號電壓一樣都是系統規范的一部分。

允許的開關噪聲幅度取決于噪聲分配。開關噪聲通常應該小于信號擺幅的5%到10%,當然噪聲的分配也取決于工程師的設計技巧,以及由誰來負責選擇連接器或者IC封裝。優秀的信號完整性工程師的談判代表非常清楚:要找到一個具有足夠低互感的連接器或封裝將是多么的困難,所以他會盡可能地爭取一個更寬松的互感指標,這樣做的結果勢必導致系統中其它部分的規格更加嚴格。

首先可以使用如下的值來開始這種估算:

首先可以使用如下的值來開始這種估算:Vn/Va =5%,Za=50歐姆,t=0.5ns,由上述公式可計算出允許的最大互感值是1.2n

圖3:連接器管腳的三維實體模型

確定上述應用假設條件后,就相當于對連接器或封裝的信號路徑之間允許的互感值施加了約束條件。當然,在時間、成本費用以及產品風險之間權衡并且實施資源分配之前,優秀的設計工程師應該運用更加完善而全面的系統級仿真來考察究竟多大的互感可以確保設計成功,并且不會對系統造成過多的負擔。因此,上面的估算僅僅是一個最初的預期值

事實上,上述估算過高地估計了允許的互感值,這是因為假設靜止信號線上的噪聲僅僅是由一根相鄰的變化信號路徑的信號變化造成的。實際的情況下,通常可能有多個信號路徑并發變化,其中每一個開關的信號路徑都會對靜止信號線產生并發開關噪聲。根據連接器的設計,信號管腳之間實際允許的互感值通常只有上面估算值的一半到五分之一左右。

連接器管腳對之間或封裝引線對之間的互感值為1.2nH是不是太大?我們來看一個具體的實例,就會發現1.2nH實際上是一個很小的值,而對于實際的連接器或封裝需要做許多艱苦的工作才有可能減小該數值。

電子發燒友App

電子發燒友App

評論