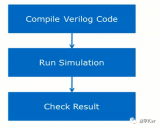

下圖是一個典型的EDA仿真驗證環境,其中主要的組件就是激勵生成、檢查和覆蓋率收集。

2023-04-13 09:27:33 1440

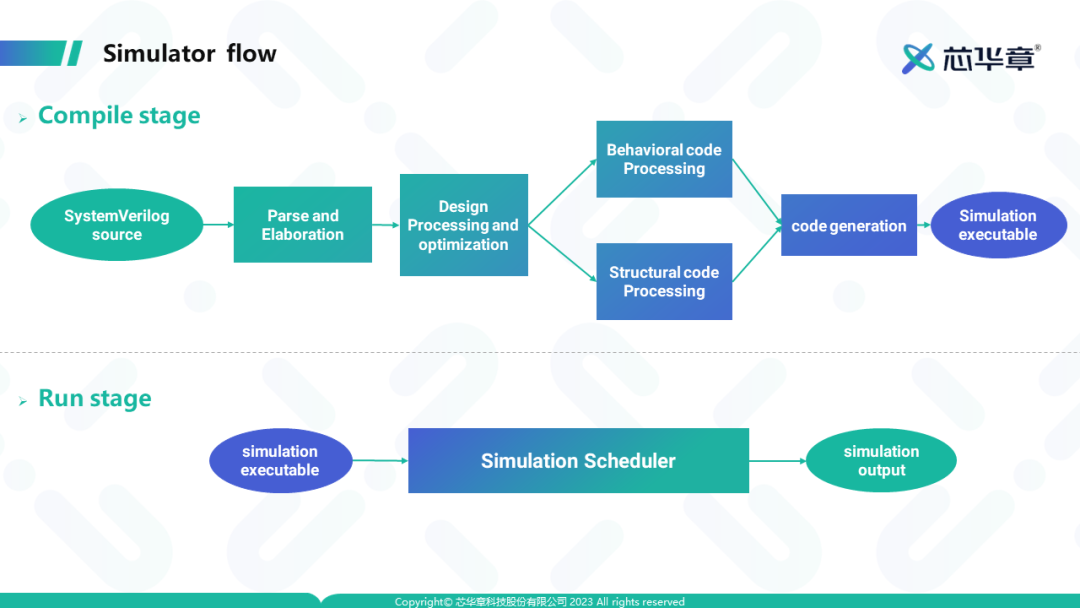

1440 VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2023-10-25 17:22:28 491

491

EDA仿真與虛擬儀器技術

2020-03-06 16:06:40

EDA仿真怎么回事? 沒看到有仿真界面??????

2017-09-06 23:34:23

VCS是Synopsys公司的數字邏輯仿真工具,DVE是一個圖形界面,便于調試RTL代碼,查看波形。本視頻簡要介紹VCS的常用概念。 歡迎大家加入啟芯SoC QQ群: 275855756。共同交流和學習SoC芯片設計技術。

2013-10-04 13:07:00

在make com編譯成功后,terminal卡住了一直沒有反應,這是什么情況有大佬知道嗎?VCS仿真卡住,為什么無法生成verdi波形文件呢?

2021-06-21 08:14:57

VCS-verilog compiled simulator是synopsys公司的產品.其仿真速度相當快,而且支持多種調用方式;使用的步驟和modelsim類似,都要先做編譯,再調用仿真.Vcs

2011-12-15 10:27:10

是把xilinx含有RAMB的仿真庫添加進VCS compile,并且庫中的RAMB也是有INIT的,但是vcs結果好像對INIT不敏感,即使我把INIT值改成別的,vcs也是正確的 {:10:}向各樓求助,如果vcs的確對RAMB的INIT初值不敏感,還有什么辦法可以驗證的,謝謝!

2015-03-05 11:22:05

本帖最后由 eehome 于 2013-1-5 10:08 編輯

Xilinx Fpga前仿真后仿真

2012-08-17 08:50:07

Xilinx Fpga前仿真后仿真

2012-08-15 18:49:38

,幾次出現the design unit was not found,modelsim已經編譯好xilinx的仿真文件了,不知道為什么還出現這樣的錯誤,請大家討論下。

2016-01-21 10:12:40

在FPGA開發過程中需要利用Modelsim對設計進行仿真,在不同階段需要用到不同的庫文件,這里把Xinlinx庫文件的編譯過程說一下。常用有三個庫xinlixcorelib,unisims

2012-02-27 15:16:55

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

ATK-USB Blaster仿真器 BURNER 5V

2023-03-28 13:05:53

編譯好,可以提高仿真效率,下面整理了Altera 和Xilinx器件需要的庫,希望能方便大家使用。如何建立仿真庫請查閱其他資料,

2012-08-10 18:31:02

DAP仿真器 BURNER

2023-03-28 13:06:20

設計中用到了GTP_DUAL,利用questasim仿真。Simulation時報錯,說找不到GTP_DUAL_fast.v這個文件。在xilinx的安裝目錄下mti文件中搜索到

2016-08-30 16:04:52

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

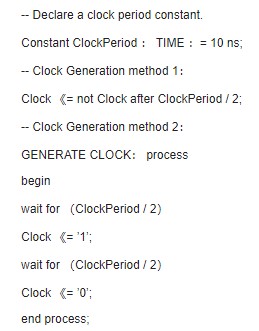

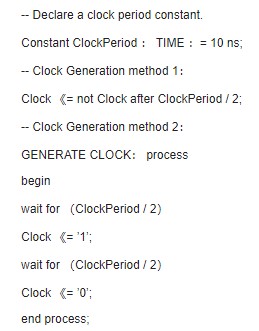

VHDL特點是什么VHDL語言在EDA仿真中的應用

2021-04-29 06:01:15

所用Linux系統為openSUSE64位,軟件為VCS2012在Linux下對verilogHDL進行功能仿真時非常必要的,下面提供兩種常見方式。1.腳本方式1)建立工作文件夾pre_sim,并將

2019-07-09 08:10:24

nanosim和vcs為什么可以聯合起來進行數字模擬混合仿真?nanosim和vcs混合仿真的過程是怎樣的?

2021-06-18 08:28:30

分析電路結構,通過電路仿真得到準確的非連續模式S參數。這些EDA仿真軟件與電磁場的數值解法密切相關的,不同的仿真軟件是根據不同的數值分析方法來進行仿真的。通常,數值解法分為顯示和隱示算法,隱示算法(包括

2019-07-30 07:27:53

怎樣通過Makefile腳本進行編譯和仿真?Makefile腳本是如何簡化VCS中仿真設計的?

2021-06-18 10:03:17

請教大神,我在Linux上用vcs+verdi對demo_nice進行仿真,但是沒有成功

我是用hibrd.sdk把demo_nice編譯成.verilog文件的,其內容如下

另外我還對tb

2023-08-12 08:07:30

在ModelSim中添加xilinx仿真庫的具體步驟

2018-09-12 14:58:15

代碼如下:頂層模塊代碼:波特率產生模塊接收模塊代碼:發送數據模塊一、VCS仿真下面開始進行VCS仿真。VCS要使用圖形化界面,必須得先編譯得到vpd文件,才能用圖形化界面看波形。首先是編譯verilog

2022-07-18 16:18:48

先編譯Xilinx的仿真庫,否則就會產生無法加載simprim,unisim等庫文件的錯誤。在許多論壇上都提到了使用compxlib命令來編譯Xilinx的仿真庫,如使用compxlib -s

2012-02-24 21:40:17

仿真技術去分析電路結構,通過電路仿真得到準確的非連續模式S參數。這些EDA仿真軟件與電磁場的數值解法密切相關的,不同的仿真軟件是根據不同的數值分析方法來進行仿真的。通常,數值解法分為顯示和隱示算法,隱示

2019-06-27 07:06:05

,通過電路仿真得到準確的非連續模式S參數。這些EDA仿真軟件與電磁場的數值解法密切相關的,不同的仿真軟件是根據不同的數值分析方法來進行仿真的。通常,數值解法分為顯示和隱示算法,隱示算法(包括所有的頻域

2019-06-19 07:13:37

基于矩量法仿真的微波EDA仿真軟件基于時域有限差分的微波仿真軟件基于有限元的微波EDA仿真軟件

2021-05-25 06:19:18

用VCS仿真沒問題,用vivado仿真時添加rtl時就出現錯誤;

出錯在rtl里斷言語法上(assert property),這會導致編譯不通過;該如何解決?

2023-08-16 07:47:06

VCS有哪幾種調試模式?萌新求助關于VCS仿真指南

2021-04-29 06:52:26

請問VCS+HSIM混合仿真怎么提速,實在跑的太慢了

2021-06-25 07:09:49

仿真工具的使用方法,它們是Modelsim,VCS和NCsim,分別是Mentor,Synoposys和Cadence的產品。這也是XILINX提供這些工具的原型庫,以及技術支持。不過如果需要仿真

2013-03-14 11:49:58

高速DAP仿真器 BURNER

2023-03-28 13:06:20

基于公共數據結構的EDA仿真波形分析技術:現有的EDA仿真工具缺乏對仿真數據的分析處理功能,影響了仿真分析的效率。本文提出一種基于公共波形數據結構的仿真波形自動分析技

2009-10-23 16:49:51 21

21 電基于公共數據結構的EDA仿真波形分析技術

摘要: 現有的EDA仿真工具缺乏對仿真數據的分析處理功能,影響了仿真分析的效率。本文提出一種基于公共波形數

2009-12-07 13:54:16 12

12 應用EDA 技術仿真電子線路分析

摘 要 介紹了電子電路仿真軟件Elect ronicsWo rkbench 在EDA 中的應用, 給出了仿真實例, 并結合實例介紹了該軟件對電子線路進行仿

2009-12-07 13:59:39 0

0 摘要:本文通過幾個實例來介紹如何用EDA(Electronics Design Automation)軟件Multisim進行三相電路特性仿真實驗的方法。關鍵詞:EDA軟件;Multisim;

2010-04-13 22:23:05 121

121 應用EDA技術仿真電子線路摘要開拓了電子電路仿真軟件Elect ronjcsWorkbench 4KEDA 中的應用,培出了仿真實例t井結合實例舟紹了誼軟件對電子線路進行仿真的方法,給

2010-05-14 17:29:53 11

11 摘要:介紹了電子電路仿真軟件Electronjcs Workbench 在EDA中的應用,培出了仿真實例,并結合實例介紹了該軟件對電子線路進行仿真的方法,給出的仿真結果表明該軟件應用于電子線路

2010-05-20 11:32:11 73

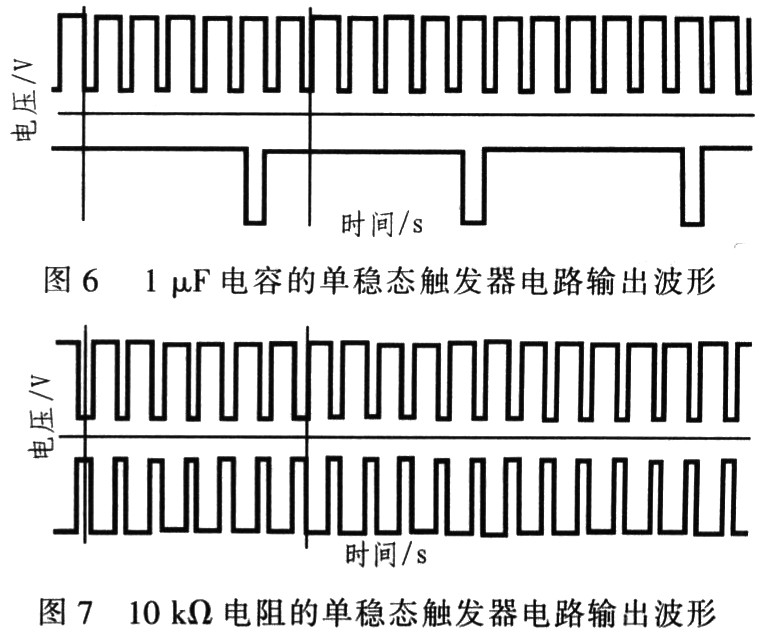

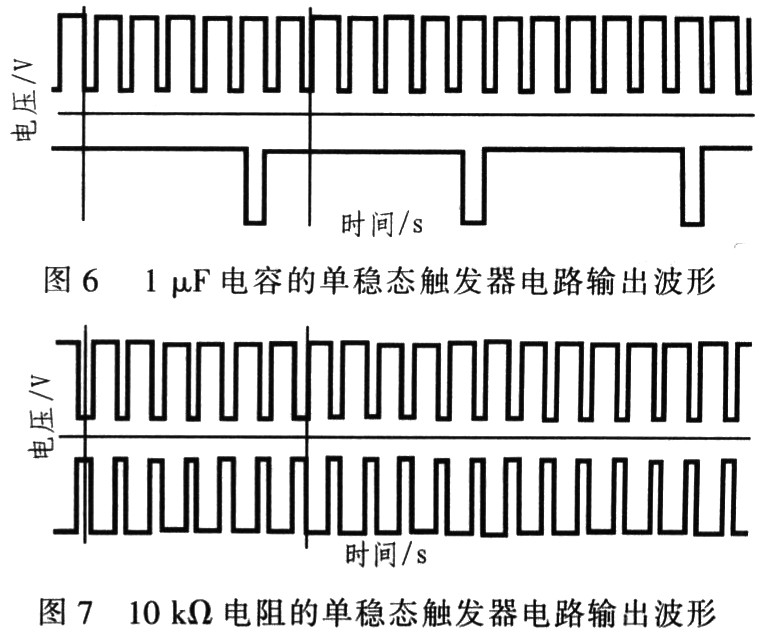

73 基于EDA技術的555單穩態觸發器設計與仿真

當前電子線路已大量采用計算機輔助仿真設計,尤其是電子設計EDA仿真技術。EDA仿真軟件中Electronics Workbench仿真設計分析軟件

2009-10-23 08:50:05 1621

1621

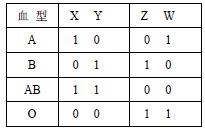

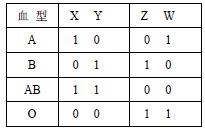

譯碼器及多路選擇器的使用( EDA 仿真) 實驗

一、實驗目的1. 掌握Multisim電子電路仿真軟件的使用,并能進行

2010-02-06 14:11:30 5856

5856

VCS-verilog compiled simulator是synopsys公司的產品.其仿真速度相當快,而且支持多種調用方式;使用的步驟和modelsim類似,都要先做

2010-10-09 16:59:08 5110

5110 Power Expert是一套可以支持Xilinx FPGA設計的最新設計工具,設計數字系統的工程師只要利用這套工具,便可解決仿真電路的設計問題。這個設計工具網頁詳列Xilinx各種不同的FPGA產品以供工程師挑

2011-03-16 14:48:58 137

137 電子發燒友網站提供《EDA_Proteus_HA_proteuse仿真軟件.rar》資料免費下載

2013-01-10 13:27:10 45

45 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 SST89E516仿真芯片的仿真操作步驟.SST89E516仿真芯片的仿真操作步驟-

2015-12-28 14:25:34 0

0 我們經常使用Xilinx Ise與Modelsim聯合仿真,但是經常出現一些由于庫沒有編譯而出現的錯誤!下面是我總結的方法:

2017-02-11 13:43:06 1348

1348

當ISE調用ModelSim進行仿真的時候,如果在FPGA設計中使用了Xilinx提供的的IP core或者其他的原語語句,ModelSim不添加Xilinx相應的庫文件的話,是無法仿真的。

2017-02-11 15:22:37 1274

1274

在我們用ModelSim仿真的時候經常是修改一點一點修改代碼,這樣會造成一個無奈的操作循環:修改代碼--->編譯代碼--->仿真設置--->進入仿真頁面--->添加需要觀察的波形--->運行仿真

2017-02-11 15:25:07 10139

10139

allegro的PI仿真電源平面完整性的操作步驟解析

2017-03-14 15:50:06 49

49 VCS-MX的版本,可以混合編譯Verilog和VHDL語言 由于在linux系統中個人用戶各種權限被限制,導致很多地方無法正常使用軟件之間的協調工作。 為了以防萬一,在此以個人用戶去實現vivado調用VCS仿真。

2018-07-05 03:30:00 10733

10733

STM32編譯開發環境及仿真調試篇-----野馬學習筆記

2017-10-27 09:13:44 26

26 modelsim仿真詳細過程(功能仿真與時序仿真).ModelSim不僅可以用于數字電路系統設計的功能仿真,還可以應用于數字電路系統設計的時序仿真。 ModelSim的使用中,最基本的步驟包括創建工程、編寫源代碼、編譯、啟動仿真器和運行仿真五個步驟。

2017-12-19 11:14:11 63886

63886

IARMSP430項目編譯與JTAG仿真調試步驟。

2018-04-19 08:29:09 5

5 (1)交互式仿真方法:利用EDA工具的仿真器進行仿真,使用方便,但輸入輸出不便于記錄規檔,當輸入量較多時不便于觀察和比較。

2019-04-25 08:00:00 9300

9300

Xilinx針對Zynq 7000,Zynq Ultrascale + MPSoC和Microblaze的QEMU簡介。

了解如何使用Xilinx的開源強大仿真平臺加速您的開發。

2018-11-21 06:33:00 3325

3325 Xilinx合作伙伴和客戶展示了他們如何使用Zynq仿真平臺。

2019-01-03 13:14:43 4329

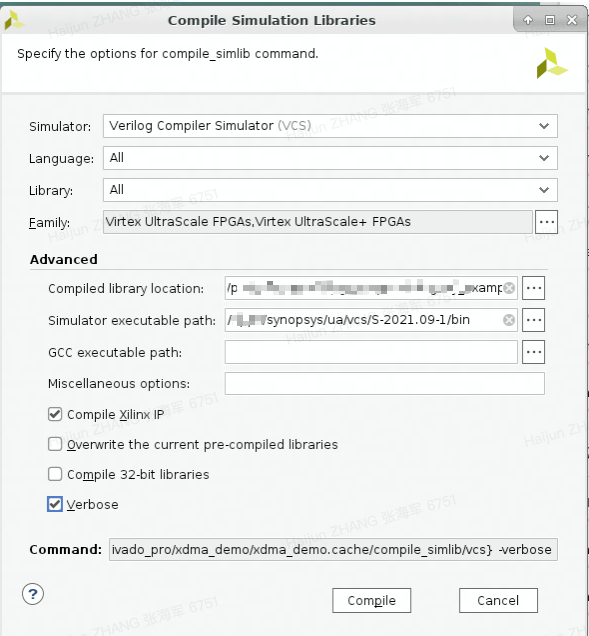

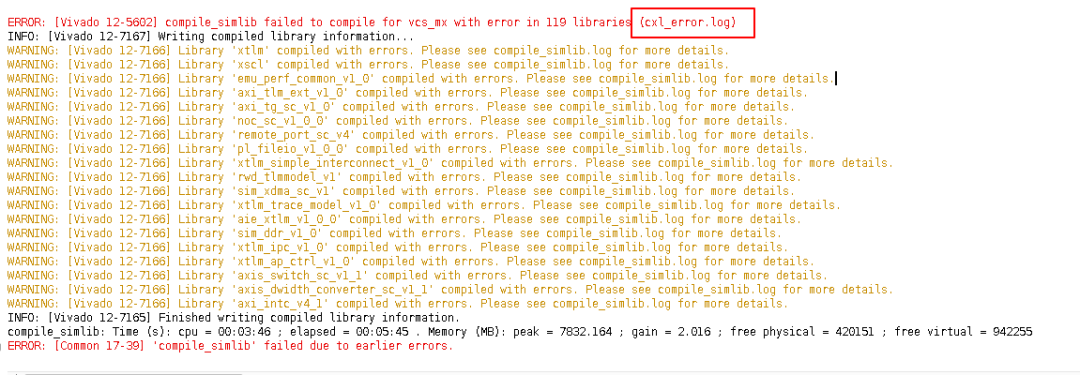

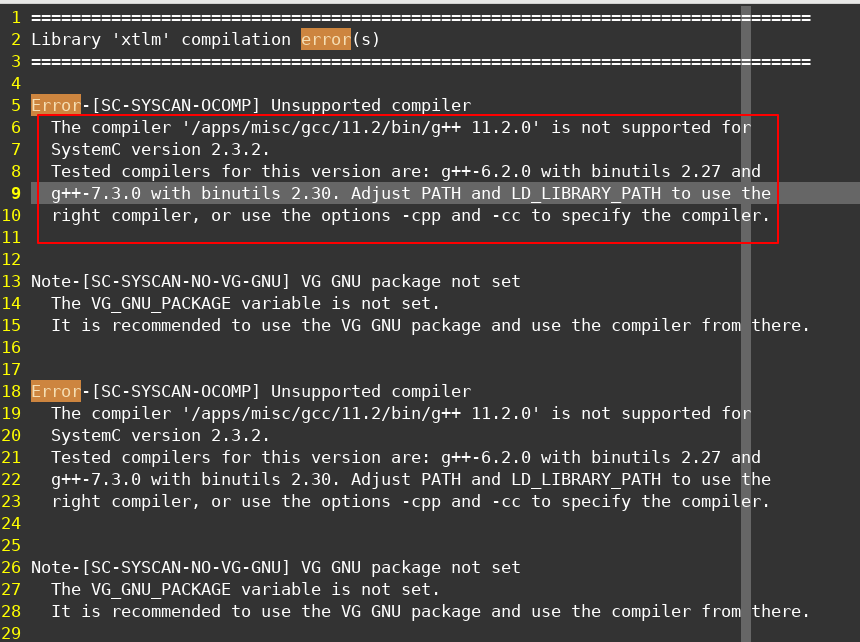

4329 了解如何使用Vivado中的Synopsys VCS仿真器使用ZYNQ BFM IPI設計運行仿真。

我們將演示如何編譯仿真庫,為IP或整個項目生成仿真腳本,然后運行仿真。

2018-11-29 06:59:00 4558

4558 了解如何使用Vivado中的Synopsys VCS仿真器使用MicrBlaze IPI設計運行仿真。

我們將演示如何編譯仿真庫,為IP或整個項目生成仿真腳本,然后運行仿真。

2018-11-29 06:57:00 6822

6822 ModelSim不僅可以用于數字電路系統設計的功能仿真,還可以應用于數字電路系統設計的時序仿真。 ModelSim的使用中,最基本的步驟包括創建工程、編寫源代碼、編譯、啟動仿真器和運行仿真五個步驟,仿真流程如圖1所示:

2018-12-29 11:35:14 9227

9227 若想用Verdi觀察波形,需要在仿真時生成fsdb文件,而fsdb在vcs或者modelsim中的生成是通過兩個系統調用$fsdbDumpfile $fsdbDumpvars來實現的。

2020-09-22 15:01:55 7809

7809 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有

2021-03-22 10:31:16 3409

3409 stm32簡單程序編譯及完成51程序設計與仿真

2021-11-21 16:36:03 3

3 VCS是一個高性能、高容量的編譯代碼仿真器,它將高級抽象的驗證技術集成到一個開放的本地平臺中。它能夠分析、編譯和編譯Verilog、VHDL、SystemVerilog和OpenVera所描述

2022-05-07 14:20:57 3907

3907 VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2022-05-23 16:04:45 7605

7605 本篇文章來源于微信群中的網友,分享下在SpinalHDL里如何絲滑的運行VCS跑Vivado相關仿真。自此仿真設計一體化不是問題。

2022-08-10 09:15:17 2038

2038 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有些許改進,所以寫這篇文章補充下。

2022-08-29 14:41:55 1549

1549 電子發燒友網站提供《Anlogic器件仿真庫快速編譯與使用.pdf》資料免費下載

2022-09-27 11:05:41 2

2 開源RISC-V Hummingbird E203(蜂鳥E203)的仿真工具是開源的iverilog,這里利用vcs+verdi仿真工具進行仿真;

2022-11-17 10:28:36 2023

2023 Xilinx-vivado的網表形式有edf和dcp兩個方式,兩個方式各有不同。對于仿真來說,兩者均需轉換為verilog的形式進行仿真,只是使用的命令不同。

2022-12-20 10:06:39 3117

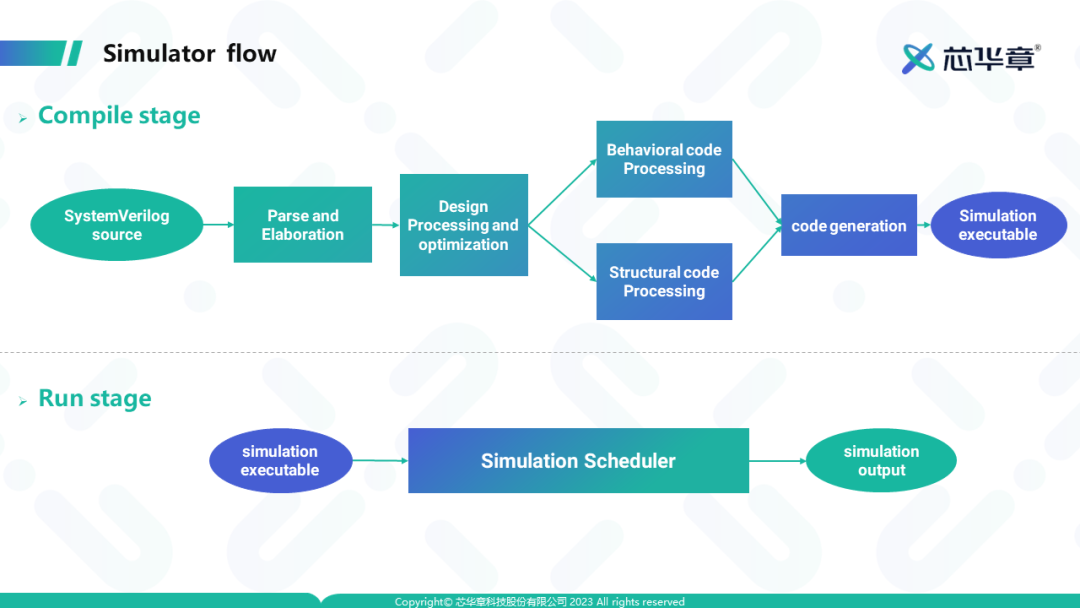

3117 幾乎所有的芯片設計、芯片驗證工程師,每天都在和VCS打交道,但是由于驗證環境的統一化管理,一般將不同的編譯仿真選項集成在一個文件里,只需要一兩個人維護即可。所以大部分人比較少有機會去深入地學習VCS的仿真flow。基于此,本文將介紹VCS仿真的 兩種flow ,概述這兩種flow分別做了哪些事!

2023-01-10 11:20:38 2280

2280 的。可以說,EDA軟件從誕生之日起,就帶著強烈的仿真基因。因此,如果沒有一款獨立自主的數字仿真器,國產EDA實現對國外工具壟斷的打破就無從談起。 目前,行業主流的仿真器,諸如VCS,Xcelium, Questa等,都是國外EDA大廠花了數十年的時間開發、迭代而來的。這些軟件內部設計極其復

2023-03-21 13:35:24 745

745

下圖是一個典型的EDA仿真驗證環境,其中主要的組件就是激勵生成、檢查和覆蓋率收集。

2023-04-15 10:13:06 1231

1231 EDA技術的核心并不是仿真,仿真只是EDA技術的一個重要環節。EDA技術的核心是利用計算機輔助設計(CAD)工具,將電路設計自動化,實現從電路設計到制造的全流程自動化。仿真只是在這一流程中的重要一環,用于驗證設計的正確性、可靠性和穩定性等方面。

2023-04-24 18:22:15 1875

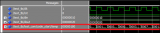

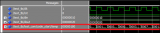

1875 我們以一個簡單的加法器為例,來看下如何用vcs+verdi仿真Verilog文件并查看波形。

2023-05-08 16:00:57 4238

4238

我們以一個簡單的加法器為例,來看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件內容如下:

2023-05-11 17:03:36 1268

1268

VCS是一款常見的Verilog編譯工具,它提供很多編譯選項來控制編譯過程及其輸出。本文主要介紹以下兩個編譯選項。

2023-05-29 14:46:39 6967

6967 VCS是編譯型verilog仿真器,VCS先將verilog/systemverilog文件轉化為C文件,在linux下編譯生成的可執行文./simv即可得到仿真結果。

2023-05-30 09:26:05 807

807

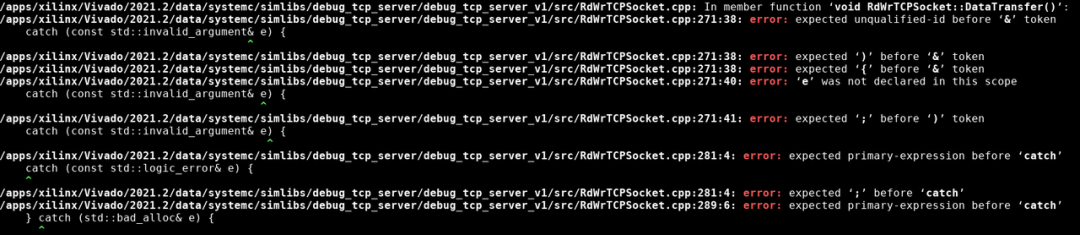

最近,需要使用VCS仿真一個高速并串轉換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 1597

1597

使用VCS仿真Vivado里面的IP核時,如果Vivado的IP核的仿真文件只有VHDL時,仿真將變得有些困難,VCS不能直接仿真VHDL

2023-06-06 11:15:35 1328

1328

電子發燒友網站提供《Xilinx快速仿真器:用戶指南.pdf》資料免費下載

2023-09-15 14:54:25 0

0 Cadence仿真步驟

2022-12-30 09:19:47 13

13 Calibre是一種先進的電子設計自動化(EDA)工具,用于電子電路的設計和仿真。它為工程師提供了一個強大的平臺,可以進行多個級別的仿真,包括電路級仿真、行為級仿真和系統級仿真。在使用Calibre

2024-01-04 17:24:59 301

301 VCS的仿真選項分編譯(compile-time)選項和運行(run-time)選項。編譯選項用于RTL/TB的編譯,一遍是編譯了就定了,不能在仿真中更改其特性,例如define等等。

2024-01-06 10:19:49 347

347

電子發燒友App

電子發燒友App

評論