allegro PCB制作異性焊盤,如圖,是一個空心的矩形環(huán),四角倒角。畫好銅皮層shape,各邊增加0.1mm畫好soldermask的shape,在PAD_DESIGNED中選中各層shape

2019-04-04 23:06:59

工作中將用ALLEGRO檢查其他人設(shè)計的PCB是否合理,元器件選擇及元件焊盤是否合適等,請教哪些資料有相關(guān)知識?

2021-02-04 16:33:40

Allegro 17.2過孔直接打到焊盤中心,怎么設(shè)置都沒有效果。除非焊盤出線后走一個角度,在其它軟件中沒有碰到。

2019-07-06 22:12:36

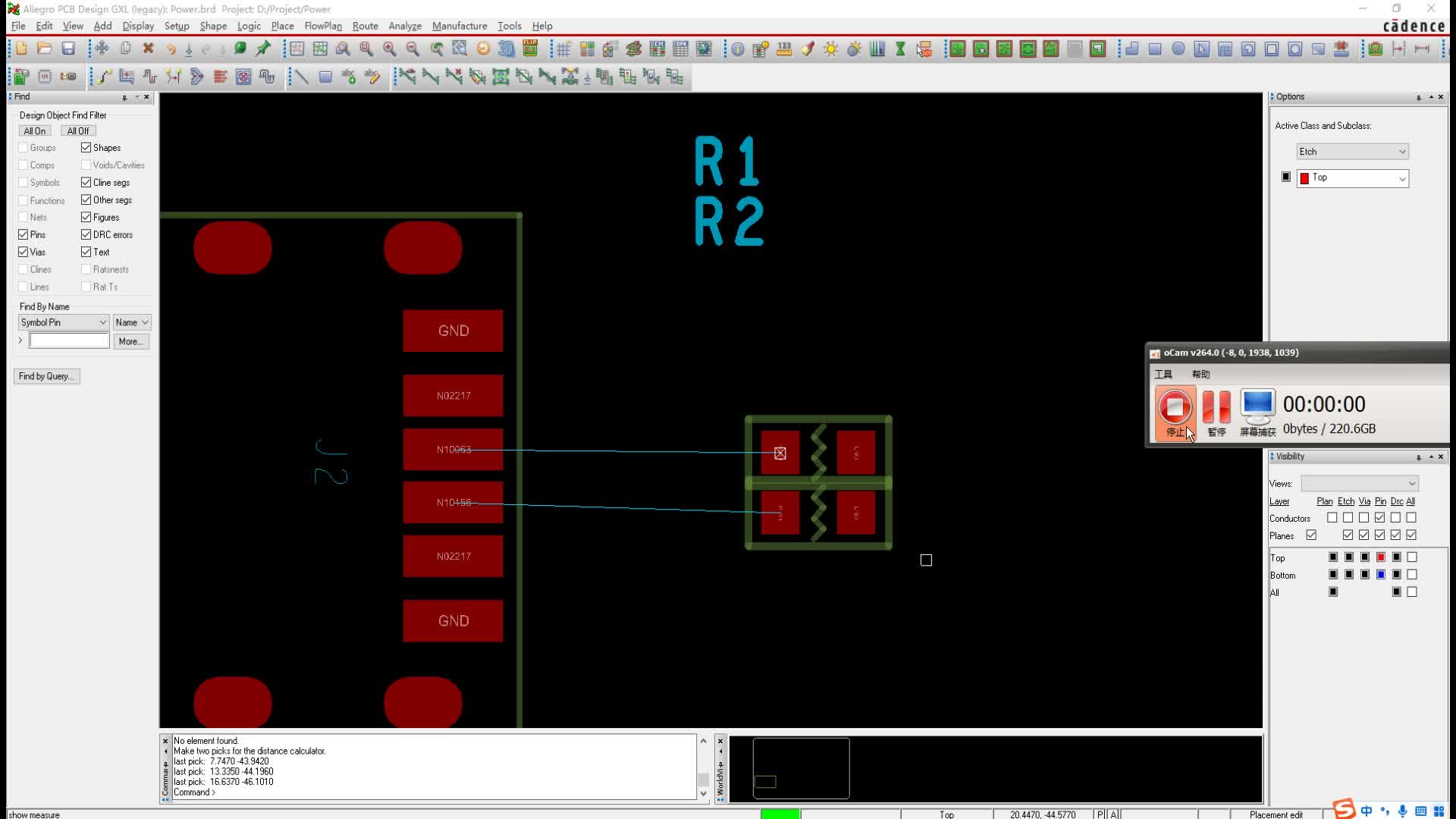

的操作步驟如下所示:貼片類型封裝制作過程可按以下步驟:第一步,需要制作貼片焊盤,打開焊盤設(shè)計組件Pad Designer,如圖4-2所示,選擇到Parameters,是鉆孔信息參數(shù);如圖4-3所示,選擇

2020-07-19 07:27:48

詳細介紹了Allegro中如何進行焊盤的設(shè)計

2018-06-08 16:12:56

Allegro焊盤和封裝制作.pdf ... Allegro焊盤和封裝制作.pdf ...

2013-05-13 23:13:53

請問下,為什么我放置焊盤的時候,捨取點一直是在焊盤的邊緣的,而不是在焊盤的中心的,我的焊盤是不規(guī)則焊盤,D-shape就是有矩形跟圓構(gòu)成的,請問怎么破?

2016-08-12 15:50:09

Allegro中焊盤命名規(guī)則說明

2011-04-08 12:37:42

Allegro中建立異形焊盤Allegro中可以建立異形焊盤.異形PAD是通過畫Shape來實現(xiàn)的.在PADS中建立異形PAD,需要借助一個PAD和Shape相結(jié)合(Associate),即可建立

2019-01-19 11:24:13

Allegro建立焊盤教程。

2018-10-23 15:09:20

Allegro建立異形焊盤,對如何利用Allegro設(shè)計異形pad做了簡要介紹,歡迎拍磚:lol

2011-05-25 11:06:08

各位壇友,最近用Allegro做封裝時,需要用到含有過孔的散熱焊盤,我的一個思路是:用Pad Designer建立一個焊盤,焊盤上打幾列過孔,如圖所示:因為矩形焊盤是表貼式焊盤,我不知道焊盤各層

2017-06-16 23:44:49

請問下,Allegro怎樣讓打印出來的焊盤空心就像AD里面的把焊盤孔給打印出來那樣,便于人工鉆孔。

2016-08-05 21:07:51

Allegro怎樣讓打印出來的焊盤空心,也就是像AD那樣打印出來方便人工鉆孔。求救求救,謝謝各位...

2016-08-05 20:47:12

各位大神們請教個問題,帶散熱孔的熱風(fēng)焊盤怎么制作,求方法,謝謝!如圖

2018-06-19 15:31:12

本人小菜鳥一個,用FPM0.0.8.0做的封裝SOT23-3 , 在allegro打開修改了一下焊盤編號順序(例如將1-2-3改為1-3-2)保存時總提示錯誤,不知道什么原因? 9 F, o9

2014-10-20 17:03:06

本帖最后由 dplion 于 2010-12-9 22:03 編輯

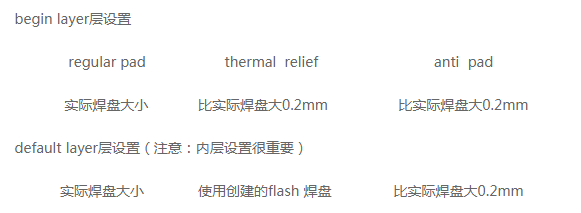

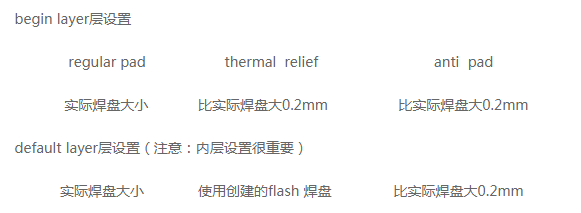

一:焊盤的制作 首先,對于焊盤的命名中,要注意通常規(guī)范的命名采用下劃線_,而非減號線-。① 通常regular pad的尺寸

2010-12-09 22:01:05

`求大神幫忙解答,allegro中焊盤如何設(shè)置成第二張圖中的效果,版本16.5,謝謝。`

2013-08-30 14:23:54

使用Anti-pad。具體使用由Allegro決定。(由于你在做焊盤的時候,不能判斷你的焊盤是用在正片還是負片,所以在做焊盤的時候,盡可能的把焊盤的三個類型全部添加進去)。關(guān)于焊盤的制作,應(yīng)注意一下幾點: 首先

2013-04-30 20:33:18

怎樣在allegro16.5中查看沒有定義的焊盤是否被添加了信號?如何避免?急急急!

2016-08-19 19:14:11

求助各位大神,安裝了Cadence之后,orcad,allegroPCB都可以可以正常使用。但是就是allegro里面設(shè)計焊盤的pad_designer沒有菜單欄是因為什么???求助,各位,小弟感激不盡!~

2015-11-26 09:47:39

在焊盤制作時候,Pad Designer 默認的保存路徑是C:\SPB_Data,于是在Layers標簽頁參數(shù)設(shè)置時,出現(xiàn)下圖示情況(可見附件)。請問如何導(dǎo)入其他路徑的參數(shù)?

2013-08-10 18:07:44

焊盤命名規(guī)范 通常我們的焊盤分為通過孔(THP)焊盤和表貼(SMD)焊盤兩種形式。但這兩種形式當(dāng)中,又有多種形狀。所以我們要有一個統(tǒng)一的命名規(guī)范,以方便以后調(diào)用。一、THP焊盤命名規(guī)范圓形通孔焊盤

2011-12-31 17:27:28

` 誰來闡述一下焊盤是什么?`

2020-01-14 15:29:27

本帖最后由 iamstrongman 于 2012-2-16 22:44 編輯

大家好偶是初學(xué)者,想請教下焊盤的畫法1.我們普通放置焊盤一般頂層和低層都會有焊盤;并且頂層和底層焊盤間中間的通孔

2012-02-16 22:32:40

本帖最后由 huangshun2016 于 2017-4-14 09:47 編輯

ALTIUM09制作異形焊盤的方法

2016-05-28 08:05:55

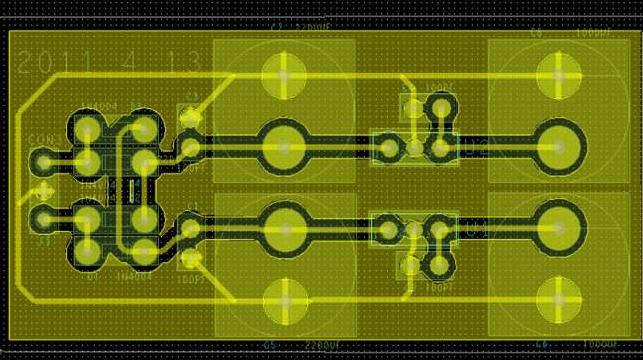

先看幾個異形焊盤想必日常中上面的都見過吧,計算器、遙控器等會用到按鍵那種,黃色的那個或許在顯示屏的排線上能看到不少。大家都知道的應(yīng)該就是SOT-89這個封裝了吧。這些封裝的異形焊盤是怎么畫出來的呢

2017-12-11 23:01:02

我在制作flash焊盤時,打開PAD Designer時,顯示有自己制作的.fsm文件,顯示 NO preview,并且選中沒有建立的.fsm文件的尺寸,這是為什么,求大神指教。

2018-11-05 13:20:06

焊接固定在PCB上,印制導(dǎo)線把焊盤連接起來,實現(xiàn)元件在電路中的電氣連接。在焊錫的過程中如果對這方面不懂的人就很容易把PCB上的焊盤破壞,嚴重導(dǎo)致整塊電路板報廢,下面小編就和大家來說說關(guān)于焊盤的一些

2020-06-01 17:19:10

一.PCB加工中的孔盤設(shè)計 孔盤設(shè)計,包括金屬化孔、非金屬化孔的各類盤的設(shè)計,這些設(shè)計與PCB的加工能力有關(guān)。 PCB制作時菲林與材料的漲縮、壓合時不同材料的漲縮、圖形轉(zhuǎn)移與鉆孔的位置精度等都會帶來

2018-06-05 13:59:38

本文以藍牙音箱為案例詳細講解PCB設(shè)計中焊盤設(shè)計和放置建封裝步驟:確定封裝類型-焊盤設(shè)計-放置焊盤-添加安裝外框-添加絲印-添加器件擺放區(qū)域-添加文字信息一、確定封裝類型根據(jù)提供規(guī)格書和器件規(guī)格型號

2018-07-06 09:33:44

PCB設(shè)計中焊盤孔徑與焊盤寬度設(shè)置多少?

2023-04-12 11:34:11

目前在自學(xué)cadence軟件,在制作熱風(fēng)焊盤的時候,跟著書本上的步驟,設(shè)置參數(shù),為什么點OK生成時,不顯示圖形?報錯顯示no element found

2017-07-27 10:35:31

使用cadence自帶的XILINX的fpga的PCB封裝,其焊盤不是表貼焊盤而是通孔焊盤,這是為什么?所用FPGA型號為spartan6系列xc6slx150csg484,圖一是封裝的top層

2020-08-05 16:08:22

orCAD怎么畫圓孔方形焊盤?我將PROTEL的圓孔方形焊盤,導(dǎo)入orCAD后,變成方孔圓形焊盤了,大小也變了。求助高手指點!

2012-08-17 09:58:23

TSOP48封裝的芯片,其Datasheet中,芯片左列管腳外端到右列管腳外端之間的距離是787密耳,我做了個PCB封裝,管腳焊盤尺寸是65X10密耳,左列管腳焊盤中心到右列管腳焊盤中心之間的距離是不是應(yīng)該也是787密耳?

2009-10-13 13:29:36

本帖最后由 萆嶶锝承鍩じ☆ve 于 2018-6-4 19:31 編輯

新手初學(xué)allegro,有很多不懂的地方,前兩天制作通孔焊盤,對里面尺寸有很多疑問,所以記錄下來。有大神看到也請多多幫忙

2018-06-04 18:09:07

焊盤與過孔設(shè)計元器件在印制板上的固定,是靠引線焊接在焊盤上實現(xiàn)的。過孔的作用是連接不同層面的電氣連線。(1)焊盤的尺寸焊盤的尺寸與引線孔、最小孔環(huán)寬度等因素有關(guān)。應(yīng)盡量增大焊盤的尺寸,但同時還要考慮

2018-12-05 22:40:12

異型焊盤的技術(shù)特點、對PCB制程中關(guān)鍵工序焊盤的制作精度及電測工藝展開研究,確保與阻焊等大的“D”字型異型焊盤PCB像常規(guī)方型或圓型焊盤PCB一樣具有優(yōu)良的電接觸性能及焊接性能。

2019-08-08 11:04:53

在使用allegro繪制蛇形天線封裝的時候,天線本體是焊盤1,饋點是焊盤2疊加在焊盤1上,導(dǎo)致報錯無法生成PSM文件,請問怎么解決呢?

2019-09-25 05:35:28

,是如何將全部焊盤導(dǎo)出呢?回到步驟4,勾選“No libraries dependencies”,含義為“不依賴庫文件”,這時再次點擊Export,就會發(fā)現(xiàn)D:TempLib目錄多出了很多.pad文件。這時,將Allegro的psm及pad目錄指向D:TempLib,就可以正常使用這里的封裝。采集

2014-11-12 17:51:40

大家好! 使用LP Wizard制作Allegro插件封裝,在批處理生成焊盤時報錯,并停止封裝建立。Pad_Allegro報錯如下:PADS TACK ERRORS and WARNINGS

2014-07-17 11:29:28

通孔焊盤制作,比如插針封裝實際孔徑大小是0.64mm,那么在做通孔焊盤時鉆孔直徑0.64+0.3(12mil)=0.94mm,焊盤大小= 0.94 + 0.8 = 1.74mm。在做Flash

2015-01-09 10:20:34

昨天晚上做了一個51單片機最小系統(tǒng)的PCB,打印出來后發(fā)現(xiàn)焊盤很小,特別是IC引腳的焊盤,如果一打孔,恐怕焊盤就沒了,在此請教各位大俠,如何批量修改較小的焊盤?先謝謝了。

2012-11-05 17:55:01

怎么設(shè)置焊盤外徑與焊盤外徑之間的距離規(guī)則

2019-09-03 22:57:43

怎么樣,不同元件類型,焊盤間快速對齊,怎么樣,不同元件類型,焊盤間快速對齊,是盤焊,不是元件

2019-08-07 22:24:04

焊盤的清理分為兩個步驟,首先清理殘留的底部填充材料,然后再清理焊盤上多余的焊料,獲得平整的焊 盤表面,最后用IPA清潔焊盤區(qū)域。殘留填充材料的清除可以利用可以旋轉(zhuǎn)的拋光刷來清理,如圖1所示。但

2018-09-06 16:33:15

新手 請教ALLegro走線時 連到焊盤的 總有角度 和中心成 45或 90用slide移線命令 總是拉不直想設(shè)置成 與焊盤可任意角連接 怎么設(shè)置請高手幫忙 。。

2014-06-03 16:12:38

1、用allegro生成的Gerber文件后,TOP.art文件中為什么會丟失了一部分焊盤和走線?2、截圖如圖片3:我嘗試過的方法a:首先檢查了生成Gerber文件的格式、參數(shù)發(fā)現(xiàn)設(shè)置正確;b:重新覆銅再次生成Gerber文件,結(jié)果仍然是top層丟失部分焊盤、走線和覆銅;有沒有其它解決方案,謝謝!

2021-08-29 11:45:28

您好,用allegro畫板子的時候,由于0201封裝的電阻電容全連接會出現(xiàn)立碑的現(xiàn)象,因此需要將接地的那個焊盤進行單連接,請問一下可以批量將所有的0201的焊盤都改成單連接 嗎、?謝謝

2019-04-03 07:35:14

1.我安裝的版本是16.52.制作焊盤時有個選項叫做Single layer mode,我查到的資料都說,如果要制作貼片焊盤則勾選此項。這時候DEFAULT INTERNAL層和End LAYER層

2017-09-11 09:11:23

我是Allegro的新手,也學(xué)習(xí)了Allegro的教程,在教程里,我看到每次做封裝時都要先做焊盤,那我能不能不做焊盤而直接用Allegro中自帶的焊盤來元件的封裝嗎?有請高人請教。

2013-01-16 08:43:48

自己手動制作過孔(VIA)時,需要添加隔離焊盤(Anti Pad)嗎?

2016-11-30 21:37:18

本帖最后由 feiniao_chh 于 2010-12-9 21:29 編輯

請教高手,我的allegro為什么不能建立焊盤? 情況如下:運行Pad Designer工具時OK,但在建立焊盤

2010-12-09 21:27:50

allegro更改焊盤大小后如何更新焊盤?

2019-05-17 03:38:36

表貼的阻焊跟實際焊盤一樣可以? 為何要大一點?

2019-08-09 05:35:22

請問allegro中添加焊盤,怎么添加?我能在界面上tools==〉padstack==〉modify Design padstack或modify library padstack,看見我需要的焊

2014-07-31 10:55:43

在allegro制作插件通孔封裝時,只設(shè)置正焊盤,不設(shè)置熱風(fēng)焊盤和隔離焊盤,對多層pcb板有影響嗎?

2019-09-16 10:27:51

allegro走線的時候如何不捕捉焊盤中心,有的時候自動捕捉焊盤中心在布線的時候很不方便

2019-02-26 10:44:47

請問在allegro中鼠標移動到焊盤可以像AD中那樣,與這個焊盤所連接的所有線高亮嗎?如圖鼠標移動到一個焊盤,與他所連接的飛線可以高亮嗎?多謝解答!

2019-06-21 00:22:38

SMD焊盤的過孔和布線區(qū)域布線的空間計算,以1.0mm間距的NSMD焊盤為例,NSMD焊盤到焊盤之間的中心間距距離為1.0mm,NSMD焊盤的直徑為0.47mm,焊盤之間焊盤平行布線空間為

2020-07-06 16:06:12

Allegro手動做封裝的操作步驟

雖然向?qū)Ш芎糜?但有些封裝必須手動做,以下為本人學(xué)習(xí)別人的教程后自己在實踐中的總結(jié),如有不當(dāng)請指正:1.File/New 在dr

2008-03-22 16:50:50 3527

3527 Allegro生成鉆孔文件的步驟

生成鉆孔文件的步驟:ALLEGRO TO NC DRILL

1. Manufacture -> NC -> Dr

2010-03-21 18:11:19 4569

4569

Artwork 是製造PCB所需要用的一組影像底稿,PCB Layout完成後,將圖形製作成Artwork檔,提供給PCB(或Substrate)製造廠商,這個步驟我們稱為製作Artwork (Artwork process)。 Artwork可以為正片格式或負片格式,正片格式-將有圖形的部份如( connect lines, pa

2011-03-09 18:04:51 0

0 Altium板轉(zhuǎn)換為Allegro板步驟 不收積分,需要的看下

2015-11-23 17:45:43 0

0 Allegro的一份比較詳盡的有關(guān)焊盤和封裝制作的資料

2015-12-15 18:41:15 7

7 Allegro焊盤制作,有需要的下來看看。

2016-02-22 15:40:38 17

17 Allegro封裝制作,適合layout工程師學(xué)習(xí)

2016-06-06 10:29:29 0

0 本文檔內(nèi)容接受啊了基于ALLEGRO導(dǎo)出PROE文件步驟,供參考。

2018-02-08 11:43:15 18

18 是不是還在對allegro建立焊盤的一些方法和規(guī)則模糊不清,這里就對大家進行詳細的介紹,希望能幫助到大家。 詳細說明下,allegro軟件中,制作通孔焊盤的方法步驟: 對pcb設(shè)計來說,通孔類的元件

2018-04-25 15:01:00 12991

12991

allegro與PADS的區(qū)別及創(chuàng)建PCB封裝的步驟

2021-03-27 10:56:29 63

63 電子發(fā)燒友網(wǎng)為你提供ALLEGRO 焊盤制作步驟資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-23 08:46:48 11

11 ALLEGRO約束規(guī)則設(shè)置步驟(以DDR為例)

2022-12-30 09:19:29 10

10 Altium板轉(zhuǎn)換為Allegro板步驟

2022-12-30 09:19:43 2

2 電子發(fā)燒友網(wǎng)站提供《Allegro16.6光繪生成步驟.pdf》資料免費下載

2024-03-07 14:22:01 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論