度、精度和易用性都是設(shè)計者使用仿真時的關(guān)鍵需求,他們要用仿真將自己的模擬、RF和混合信號設(shè)備推向市場。廣受尊重的Spice仿真器仍是模擬仿真工具的選擇,而EDA供應(yīng)商正在通過創(chuàng)新技術(shù)改進自己工具的速度與精度,如使它們適合于多核處理器或多CPU系統(tǒng)的運行。其它公

模擬與RF仿真工具提供各種仿真速度的選擇,并支持分層的設(shè)計策略。

要點

??在將設(shè)計交付硬件實現(xiàn)以前,應(yīng)采用能夠使用矩量法和有限元分析技術(shù)的EM(電磁)域工具,解決鄰近效應(yīng)和轉(zhuǎn)換效應(yīng)問題。

??快速Spice工具偏向于用精度換取速度,但制造商經(jīng)常聲稱這些工具有“Spice級精度”。

??傳統(tǒng)的Spice仿真器在十萬個元件時就無能為力了,哪怕采用并行處理也不能提高容量。

??隨著消費產(chǎn)品的制造商們努力以更低成本提供更高的功能密度,他們要在小體積內(nèi)塞進數(shù)字、模擬和RF功能,這就產(chǎn)生了芯片、封裝和電路板的協(xié)同設(shè)計與仿真需求。

速度、精度和易用性都是設(shè)計者使用仿真時的關(guān)鍵需求,他們要用仿真將自己的模擬、RF和混合信號設(shè)備推向市場。廣受尊重的Spice仿真器仍是模擬仿真工具的選擇,而EDA供應(yīng)商正在通過創(chuàng)新技術(shù)改進自己工具的速度與精度,如使它們適合于多核處理器或多CPU系統(tǒng)的運行。其它公司則正在重新編寫Spice算法,以加快仿真速度。當(dāng)然也有一些公司關(guān)注自頂向下的設(shè)計。

但當(dāng)設(shè)計者為越來越多的產(chǎn)品增加RF/無線通信功能時,Spice只是仿真場景中的一部分。隨著工藝尺度的縮小、數(shù)字電路速度的增加以及高速串行I/O端口的增多,不提供RF/無線功能的產(chǎn)品也正在具備RF性能。此外,在很多情況下,隨著頻率的上升以及設(shè)計者在越來越小的空間中塞入更多功能,芯片與電路板的設(shè)計也不能獨善其身;必須對芯片、芯片封裝和電路板采取協(xié)同設(shè)計和仿真。

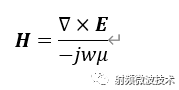

How-Siang Yap是Agilent技術(shù)公司EEsof部EDA產(chǎn)品營銷組成員,他概述了可以成為一種有效的協(xié)同仿真方案的跨域仿真技術(shù)(cross-domain-simulation)。首先他表示,需要數(shù)值域工具,如The MathWorks公司的Matlab,或Agilent公司的Ptolomy,以及C++、System-C和標(biāo)準(zhǔn)的HDL(硬件描述語言)。另外還需要頻域的交流仿真工具,它可以用S參數(shù)并實現(xiàn)諧波平衡技術(shù)。Yap補充說,對于時域,需要Spice工具。他的建議是,在設(shè)計轉(zhuǎn)為硬件以前,應(yīng)采用EM(電磁)域工具,它可以使用矩量法(method-of-moment)和有限元分析技術(shù),查找鄰近效應(yīng)和轉(zhuǎn)換效應(yīng)的錯誤。

?

Spice提速

對于Spice,關(guān)注的焦點是在提高速度的同時不喪失精度。為解決這個問題,Cadence設(shè)計系統(tǒng)公司近期宣布推出了Cadence Virtuoso APS(加速的并行仿真器),這是它的下一代電路仿真器,是Cadence MMSIM(多模式仿真)7.1版的組成部分。Cadence高級架構(gòu)師John Pierce稱,新仿真器將混合信號仿真的周轉(zhuǎn)時間從數(shù)天或數(shù)周減少到只有數(shù)小時。Cadence的一名高級產(chǎn)品經(jīng)理Nebabie Kebebew表示,新仿真器大大提升了單線程和可縮放多線程的性能,并且保持了與Cadence Virtuoso Spectre電路仿真器相當(dāng)?shù)木取ebebew說有20多個測試客戶已在200多個設(shè)計上對新仿真器作了測試,其中涉及的器件包括PLL(鎖相環(huán))、DAC、ADC、存儲器、電源管理電路和高速I/O電路。她說,一個客戶在一個八核系統(tǒng)上作65 nm PLL設(shè)計仿真時,性能提高至原來的60倍。她補充說,另一個客戶在做一個DC/DC轉(zhuǎn)換器的版圖后仿真時,性能提高至58倍,運行時間從20小時16分減少到21分鐘。

?

Mentor Graphics公司也一直致力于提高仿真速度。該公司在2008年10月推出了新版的Eldo與Eldo RF晶體管級模擬仿真器,在不影響精度的情況下,提高了原始的速度性能。新版采用一種經(jīng)修改的矩陣解算策略以及一種可縮放的多線程技術(shù),使用戶能夠充分利用廉價的多CPU硬件。

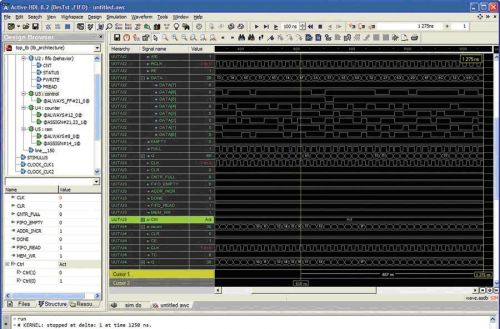

Mentor公司深亞微米業(yè)務(wù)發(fā)展經(jīng)理Tony Liao指出,多線程的Eldo運行速度為單核版的3倍~10倍以上,具體取決于電路中的有源器件數(shù)和寄生成分?jǐn)?shù)量。他說,要得到更快的仿真,客戶可以使用ADiT快速Spice仿真器,不過要付出一些精度的成本。一個ADiT與Eldo接口可以使電路同時運行兩種仿真器;需要高精度的部分在Eldo上運行,另一部分則在ADiT上運行。Liao指出,這些仿真器可與Mentor的ModelSim數(shù)字仿真器鏈接,支持協(xié)同仿真。仿真器與Mentor ICAnalyst的鏈接能幫助支持設(shè)計驗證。另外,兩種仿真器都可以協(xié)同工作在Mentor公司的ADMS(先進混合信號)仿真環(huán)境中(圖1)。

?

Synopsys也致力于加快Spice速度,并在2008年3月推出HSpice仿真器時,宣布了對其HSpice核心引擎技術(shù)的增強以及新的多線程能力。Synopsys混合信號仿真產(chǎn)品營銷總監(jiān)Geoffrey Ying表示,該公司正使全部工具都能配合多核處理器的優(yōu)勢,HSpice是第一個遷移的產(chǎn)品。他說,有了多線程版,電路設(shè)計者現(xiàn)在運行HSpice版圖后仿真的速度比單核處理器快兩倍,在四核處理器上更可以快達(dá)五倍。單核版的提速方式是改進符號的直流工作點收斂算法、瞬態(tài)時間步長控制、網(wǎng)表分析,以及模型性能。對于多核處理器,該軟件版能夠仿真包括100萬個以上阻性和容性寄生效應(yīng)的版圖后設(shè)計。

Synopsys已經(jīng)與TSMC(臺積電制造公司)在TMI(TSMC建模接口)方法上展開合作,包括一個將客戶器件模型與Synopsys HSpice、HSim與NanoSim電路仿真器相整合的協(xié)議。TMI方法為TSMC的40 nm及以下尺度工藝技術(shù)提供了一個創(chuàng)新而有效的器件建模方案。Ying稱TMI方法平均能將仿真時間和內(nèi)存使用減至五分之一,并且同時考慮了機械應(yīng)力對硅片的作用和版圖相關(guān)性,后者會根據(jù)與其它器件的接近程度,改變器件的特性。

Magma設(shè)計自動化公司采用多CPU,而不是多核心和多線程。Magma的定制設(shè)計業(yè)務(wù)部業(yè)務(wù)發(fā)展高級總監(jiān)KT Moore稱,該公司的FineSim Spice充分利用了Magma的NPT(原生并行技術(shù))將計算負(fù)載分配給多臺計算機,增加了速度與容量,并保持了精度。他說,通過該方案“客戶能夠用實際可行數(shù)量的計算機做成千上萬個器件的仿真,只用8臺計算機而不是用100臺計算機。”

雖然Spice的多線程和多計算機實現(xiàn)方法都提高了性能,但仍會繼續(xù)有對快速Spice實現(xiàn)的需求。Moore說:“在一個設(shè)計過程的不同階段,對精度的要求也有變化。在早期,你可以更關(guān)注于功能。當(dāng)你將設(shè)計集中于實際工作點和特性時,就希望收緊對精度的要求。很多大型設(shè)計都有數(shù)百萬只晶體管;你可能會在多只CPU上用我們的Spice引擎作仿真,對一個簽核(sign-off)仿真這種方法可能很好。”但他表示對于回歸仿真或功能仿真,NPT才是你可能希望使用的工具。

傳統(tǒng)的EDA公司都在Spice領(lǐng)域受到了來自相對較新成員的競爭,有時這模糊了真正Spice與快速Spice之間的界限。Berkeley設(shè)計自動化公司的首席運營官Paul Estrada說,快速Spice工具傾向于用精度換取速度。不過,制造商經(jīng)常在“Spice-accurate”(Spice級精度)的幌子下推出這些快速Spice工具。他表示,Berkeley設(shè)計自動化公司的Analog Fast Spice是真正能提供快速Spice能力,并有等同于真正Spice精度的性能。Estrada稱,該工具不做近似。反之,它運行的是原始器件方程,解算原始的全電路矩陣,產(chǎn)生的波形相當(dāng)于甚至優(yōu)于任何其它Spice引擎。

Analog Fast Spice提高了它在單核處理器上運行的性能,Estrada將其性能水平歸結(jié)于其開發(fā)人員不需要嘗試優(yōu)化原有代碼。他說:“深入觀察今天的任何Spice引擎,你會發(fā)現(xiàn),它們的基本結(jié)構(gòu)像一個老鼠窩。每個東西都與其它東西互相交織,如果你試圖改進仿真器的一個方面,那就總會把其它方面搞糟。”Analog Fast Spice采用一種模塊化架構(gòu),可以對每個模塊作優(yōu)化,而不會干擾其它模塊。展望未來,該公司認(rèn)為多線程有更好的結(jié)果,但尚未推出多線程版本。

Gemini公司也采用多線程來提高性能。該公司銷售與營銷副總裁Kent Jaeger稱,公司的目標(biāo)是95%的Spice精確工具和快速MOS Spice市場。他表示,Gemini的整體多線程Spice可提供兩至十倍的性能提升,而不會累及精度。“我們禁止自己的設(shè)計者使用任何有可能犧牲Spice精度的技術(shù)。”Gemini仿真器在90%的基準(zhǔn)測試中超過了快速MOS Spice仿真器的性能,運行在采用64位 Linux操作系統(tǒng)的低價英特爾多核處理器上。

Infinisim公司從快速Spice借用了一些技術(shù),而仍保持Spice的精度,這是該公司首席技術(shù)官Zakir Syed的表述。該公司的RASer(實時自適應(yīng)仿真)仿真器可用于設(shè)計驗證的全部階段,從單個塊到全芯片,以及從版圖前到版圖后。據(jù)該公司高級營銷總監(jiān)Anand Lyer表示,RASer針對做全系統(tǒng)仿真的關(guān)鍵需求,避免了硅片的重制(re-spin)要求。他說:“傳統(tǒng)的Spice仿真器在數(shù)十萬個元件時就無能為力了,即使采用并行處理,容量也不會增加。”

此時早晚得用類似快速Spice的方案。Syed說:“我們就像快速Spice那樣將一個電路拆成小部分,然后為不同部分使用不同的解算器。在快速Spice中,你會失去精度,但是,我們使用的是Spice采用的精確器件模型。”

雖然Infinisim支持多線程,但該公司主要關(guān)注提升每個線程的速度。Syed說:“很多公司正在開發(fā)在Spice上的多核算法,并且,這些公司已放棄了對Spice的改進。”他認(rèn)為,某些情況(如蒙特卡羅仿真)適用于多線程與分布式計算。此時,任何仿真都獨立于其它仿真。

Tanner EDA的產(chǎn)品管理總監(jiān)Nicolas Williams稱:“在模擬設(shè)計中,我們見到的迭代一般要運行五次角落模型和溫度掃描。如果要做蒙特卡羅分析,就必須對一個電路運行數(shù)千次仿真,很容易從一個指令臺處理這些仿真運行。”他補充說,這是在仿真工作級,而不是電路級,此時并行可以提供最大的好處。

Tanner的T-Spice仿真器面向大模擬、小數(shù)字芯片的設(shè)計。該公司集成了Verilog-A,同時支持行為模型和器件級Spice模型的仿真。Verilog-A支持自頂向下的設(shè)計,遠(yuǎn)優(yōu)于模擬設(shè)計者過去經(jīng)常采用的自下至上方案。Williams稱自頂向下設(shè)計可以消除昂貴而耗時的設(shè)計反復(fù),而對自下至上方案,當(dāng)設(shè)計周期后期出現(xiàn)系統(tǒng)集成問題時,這種反復(fù)是必不可少的。

他指出,模擬設(shè)計者在使用依賴性資源時會使用行為建模技術(shù),他們可能使用The MathWorks的Matlab來計算系數(shù),但迄今為止,他們在Spice編程環(huán)境中還缺乏一種行為語言。Spice與行為模型的組合使設(shè)計者能夠?qū)W⒂趬K的設(shè)計,并且無需漫長的運行時間而完成仿真。表1給出了仿真一個PLL的相對CPU時間,其元件表示為Spice與Verilog-A模型的各種組合。

超越Spice

即便一個芯片設(shè)計經(jīng)過了徹底的仿真與驗證,也不能保證在真正硅片誕生以后,該器件能正常地工作。硅片性能屈從于芯片封裝的EM效應(yīng)、封裝所安裝的電路板,或包含電路板的大尺度結(jié)構(gòu)(見附文《EM仿真:從PCB到直升機》)。Ansoft業(yè)務(wù)開發(fā)總監(jiān)Larry Williams詳述了一個半導(dǎo)體制造商的故事,它的器件裝在一塊評估板上,評估板有良好隔離的走線,并用大量的電源層和地層來隔離信號。然而,當(dāng)該制造商的客戶將器件裝在一個微型消費產(chǎn)品中時,走線靠得非常近,造成了更多的耦合,它的性能表現(xiàn)不正常。突然間,芯片的射頻開始出現(xiàn)異常,產(chǎn)生不可接受的帶外偽響應(yīng)。Williams說:“我們對芯片、芯片封裝和電路板作了完整的系統(tǒng)級仿真,以揭示如何解決這個問題。”Ansoft使用了該制造商對IC的Spice級模型,作了三維提取,為IC的BGA封裝和PCB(印刷電路板)建立了模型。他說:“我們在自己的環(huán)境中將三者全部結(jié)合起來,可以預(yù)測到這些毛刺。”

?

Ansoft的產(chǎn)品包括HFSS(高頻仿真器系統(tǒng)),它可以對高頻高速元件作三維電磁場仿真,還有SIwave(信號完整性波),它使工程師能夠直接從器件版圖數(shù)據(jù)庫(即物理CAD)中提取出電源分配與信號網(wǎng)表與頻率有關(guān)的電路模型,協(xié)助判斷信號完整性和電源分配問題(圖2)。Williams說:“我們解決了很多嚴(yán)重問題。”他補充說,滿足SI很重要,“各個公司都在設(shè)置SI部門,以確保可靠的電性能。看一下現(xiàn)在任何一臺手持電子設(shè)備,它可能有多個射頻,很多數(shù)字內(nèi)容能提供豐富的用戶體驗。它會工作在節(jié)能的低電壓下,而數(shù)字信號也因此對耦合更為敏感。我們讓一個工程設(shè)計團隊讀入一個PCB模型,與IC封裝模型的提取相耦合,將所有東西級聯(lián)起來,完成一次整體的系統(tǒng)級仿真。”

EEsof的工具包括ADS(先進設(shè)計系統(tǒng)),其起源是惠普一個開發(fā)RF與微波儀器的小組。ADS 1.0于2000年面世,它使設(shè)計者能夠仿真有數(shù)字電路(包括DSP)的RF電路。該工具最初大量應(yīng)用于WLAN(無線局域網(wǎng))設(shè)計,并繼續(xù)得到發(fā)展。隨著消費產(chǎn)品的制造商努力以更低價格提供更高的功能密度,他們正在小體積中塞入數(shù)字、模擬與射頻功能,從而創(chuàng)造出用ADS作芯片、封裝和電路板協(xié)同設(shè)計與仿真的需求。EEsof的Yap列舉了協(xié)同設(shè)計過程的兩個方面的實例:前端,它包括針對性能和成本的系統(tǒng)分區(qū)優(yōu)化;后端,涉及如球樣式規(guī)劃與布線以及I/O優(yōu)化等因素。

他表示,最新的發(fā)展是支持非線性X參數(shù)。上個月,Agilent宣布設(shè)計者可以從ADS的仿真或Agilent的測試測量儀器中生成X參數(shù),以加快通信產(chǎn)品的開發(fā)。Yap稱,X參數(shù)可節(jié)省大量時間。有了X參數(shù),設(shè)計者就可以獲得一個仿真中使用的模型。否則要做數(shù)月的特性描述,生成大量難以解析的圖表。

對于未來,Yap認(rèn)為會繼續(xù)努力將電磁仿真集成到設(shè)計流程中,從而從電路到天線的一切都作仿真。更多產(chǎn)品正在無線化,并且在緊湊型產(chǎn)品中,天線一般在PCB板上。他說,在交付實際硬件制造以前發(fā)現(xiàn)潛在問題的能力非常關(guān)鍵。

附文:EM仿真:從PCB到直升機

隨著產(chǎn)品日益復(fù)雜,工作頻率越來越高,研究信號與功率完整性問題,以仿真EMC(電磁兼容)與EMI(電磁干擾)效應(yīng)也日益重要。CST(Computer Simulation Technology)的PCB(印刷電路板) Studio可以提供幫助,它支持二維與三維仿真,可以在時域與頻域中確定趨膚效應(yīng)。它可以輸入IBIS(I/O緩沖信息規(guī)范)模型,與Spice等效工具接口。CST的Cable Studio支持PCB與連接電纜的協(xié)同仿真。

?

該公司將PCB Studio和Cable Studio整合到Studio Suite 2009 EM仿真軟件中,通過自動優(yōu)化和對某個問題采用最適當(dāng)?shù)慕馑慵夹g(shù),提升了設(shè)計的吞吐能力(圖A)。Studio Suite 2009支持瞬態(tài)EM和電路協(xié)同仿真,它提供一個64位的前端和基于MPI(消息傳遞接口)的并行,加快了大型與復(fù)雜結(jié)構(gòu)的仿真速度。它帶有一個瞬時熱解算器,可仿真加熱過程,并用一個生物熱方程作生理冷卻效應(yīng)的逼真建模。

電子發(fā)燒友App

電子發(fā)燒友App

評論