由于某整車廠混合動(dòng)力汽車在前期設(shè)計(jì)階段沒有考慮 EMC 方面的設(shè)計(jì),同時(shí)各個(gè)零部件廠家自身設(shè)計(jì)能力的不足,單個(gè)部件也不能夠滿足要求,因此整車在進(jìn)行 EMC 測(cè)試階段,也遇到不能夠滿足標(biāo)準(zhǔn) GB 18655 和 GB/T 18387 要求。

2018-05-07 08:42:23 6623

6623

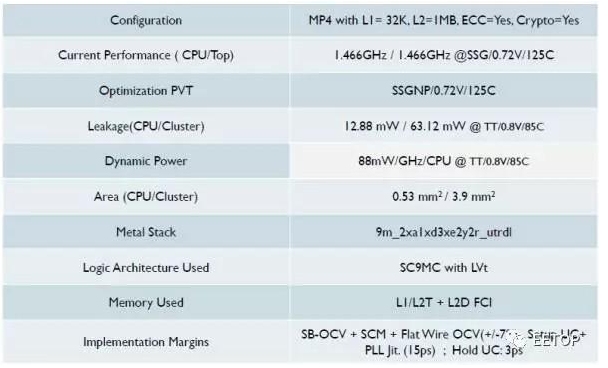

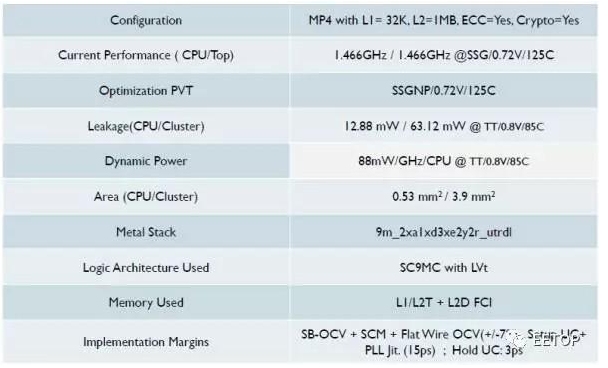

的標(biāo)準(zhǔn)。在流片階段,要遵循AEC-Q001-004以及16949的標(biāo)準(zhǔn)。成品分發(fā)之后,有AEC100的標(biāo)準(zhǔn)。應(yīng)用驗(yàn)證的時(shí)候,還要有真實(shí)的各種車內(nèi)工況測(cè)試,包括跑到吐魯番進(jìn)行高溫測(cè)試,跑到漠河對(duì)芯片進(jìn)行低溫測(cè)試的考驗(yàn)。

2021-09-02 08:32:38 10891

10891 摘 要:產(chǎn)品的電磁兼容性是工程設(shè)計(jì)人員在產(chǎn)品設(shè)計(jì)階段必須考慮的問題,它不僅影響產(chǎn)品的性能,同時(shí)影響產(chǎn)品的穩(wěn)定性。本文針對(duì)一TSV轉(zhuǎn)接板及其芯片,使用Ansys的HFSS、Designer組件對(duì)其

2022-07-19 09:42:28 2305

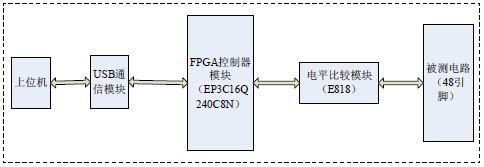

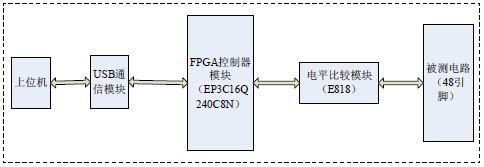

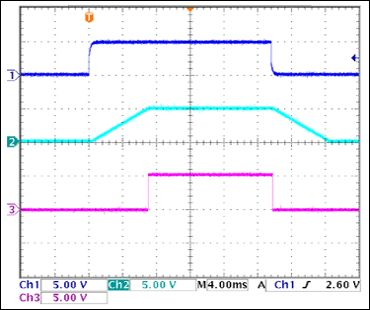

2305 硬件測(cè)試是電子產(chǎn)品開發(fā)過程很重要一環(huán),產(chǎn)品在設(shè)計(jì)階段很多潛在的問題只看表面是看不出來的,各模塊電路必須有針對(duì)性的測(cè)試才能將問題扼殺在搖籃里。因此,硬件測(cè)試工作顯得尤其重要。 ? 硬件測(cè)試工作從

2023-07-03 09:11:47 1518

1518

大家都知道在設(shè)計(jì)階段解決問題的成本是最低,同樣道理在原理圖設(shè)計(jì)階段做好關(guān)鍵信號(hào)、敏感電路的防護(hù)設(shè)計(jì)可以達(dá)到事半功倍的效果,本期將與大家探討在原理圖的設(shè)計(jì)階段如何考慮靜電防護(hù)設(shè)計(jì)。

2024-01-03 09:32:54 771

771

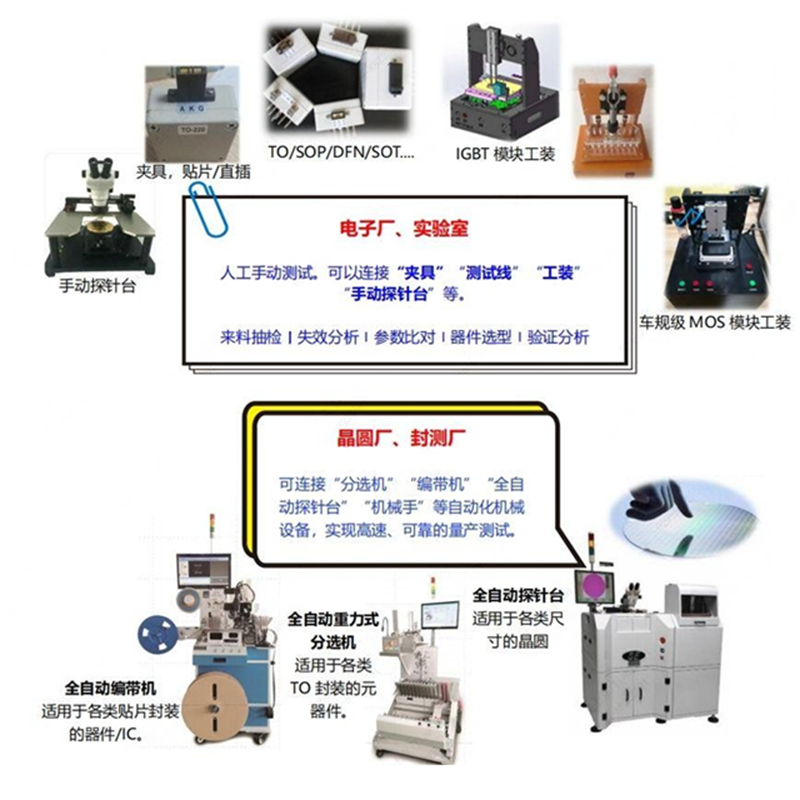

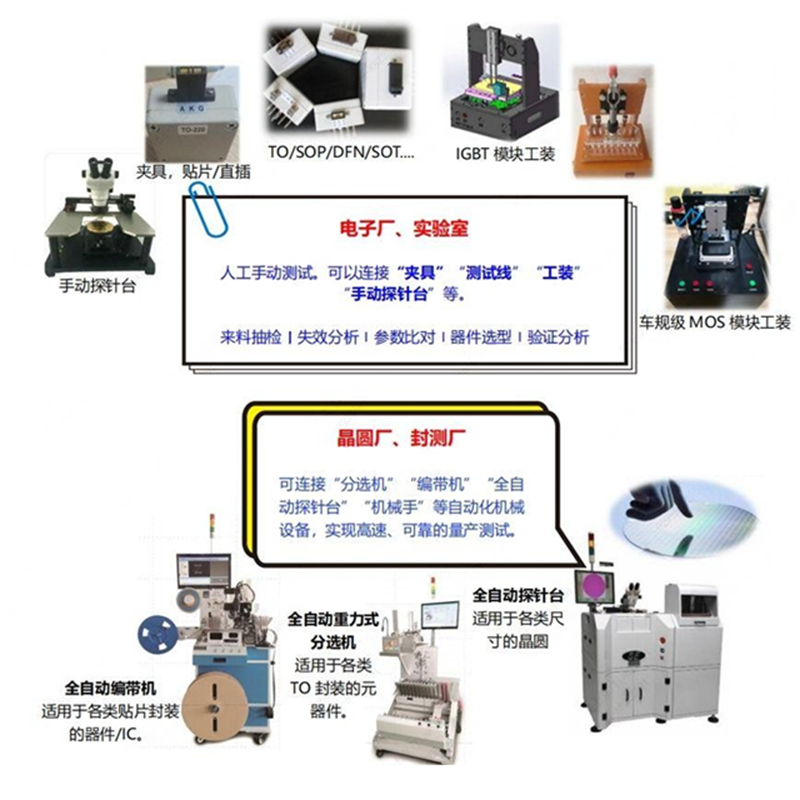

本文就芯片測(cè)試做一個(gè)詳細(xì)介紹。芯片的測(cè)試大致可以分成兩大部分。CP(chipprobering)和FT(finaltest)。某些芯片還會(huì)進(jìn)行SLT(systemlevetest)。還有一些特定

2024-07-26 14:30:47 1624

1624

集成電路測(cè)試卡位產(chǎn)業(yè)鏈關(guān)鍵節(jié)點(diǎn),貫穿設(shè)計(jì)、制造、封裝以及應(yīng)用的全過程。從整個(gè)制造流程上來看,集成電路測(cè)試具體包括設(shè)計(jì)階段的設(shè)計(jì)驗(yàn)證、晶圓制造階段的過程工藝檢測(cè)、封裝前的晶圓測(cè)試以及封裝后的成品測(cè)試

2024-08-06 08:28:14 1139

1139

對(duì)芯片進(jìn)行OS測(cè)試時(shí),都是只會(huì)連接芯片的兩根引腳,即GND與IO_PAD,這樣測(cè)試的結(jié)果就是GND與IO_

2022-01-18 09:23:30

芯片從制造到產(chǎn)品出貨,必須要經(jīng)過嚴(yán)格測(cè)試。沒有測(cè)試的芯片,無法出貨。在全世界范圍內(nèi),沒有哪家芯片設(shè)計(jì)公司敢不進(jìn)行測(cè)試就直接出貨。那么,芯片測(cè)試的重要性表現(xiàn)在什么地方?為什么要進(jìn)行測(cè)試?芯片的電路

2019-11-23 10:05:40

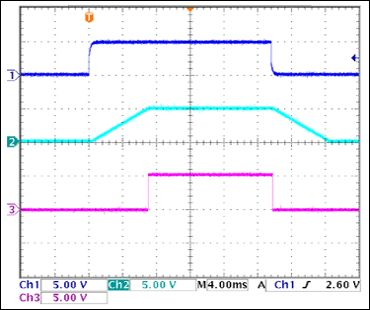

用的大部分IC都包含有數(shù)字信號(hào)。數(shù)字IC測(cè)試一般有直流測(cè)試、交流測(cè)試和功能測(cè)試,而功能測(cè)試一般在ATE上進(jìn)行,ATE測(cè)試可以根據(jù)器件在設(shè)計(jì)階段的模擬仿真波形,提供具有復(fù)雜時(shí)序的測(cè)試激勵(lì),并對(duì)器件的輸出進(jìn)行實(shí)時(shí)

2021-07-23 06:30:23

我正在嘗試在Virtex-5 FPGA板上實(shí)現(xiàn)我的研究項(xiàng)目的數(shù)字電路。電路板型號(hào)為“XC5VLX110T”。我正在使用ISE Design Suit 12.3。我有webpack許可證,我也下載了

2020-04-20 10:10:51

概述NI 提供了高速、靈活、精確的RF硬件,并搭配功能強(qiáng)大的NI LabVIEW軟件,以適應(yīng)無線通信領(lǐng)域日新月異的需求,并且貫穿了從設(shè)計(jì)、驗(yàn)證到生產(chǎn)的所有工程設(shè)計(jì)階段。為了能滿足不斷發(fā)展的通訊標(biāo)準(zhǔn)

2019-06-04 08:19:03

可以創(chuàng)建到相鄰組件引線的捷徑。階段4:PCB測(cè)試PCB制造完成后,測(cè)試對(duì)于檢查功能和特性至關(guān)重要。在這種方法中,PCB制造商確定電路板是否按預(yù)期工作。如今,PCB使用多種先進(jìn)的測(cè)試設(shè)備進(jìn)行了測(cè)試

2020-11-03 18:45:50

SoC芯片的開發(fā)流程SoC芯片開發(fā)流程大致分為四個(gè)階段,其中大部分工作都是借助于電子設(shè)計(jì)自動(dòng)化(EDA)工具完成的。總體設(shè)計(jì)總體設(shè)計(jì)階段的任務(wù)是按照系統(tǒng)需求說明書確定SoC的性能參數(shù),并據(jù)此進(jìn)行系統(tǒng)

2021-11-08 08:33:27

1、關(guān)于信令測(cè)試的故事在WiFi大規(guī)模應(yīng)用前,多數(shù)WiFi產(chǎn)品在開發(fā)階段采用直接嵌入WiFi模塊的方式來實(shí)現(xiàn)WiFi功能,甚至WiFi芯片廠家也僅粗略測(cè)量一下芯片性能即生產(chǎn)出廠。但是,隨著WiFi

2019-06-10 07:30:31

硬件上設(shè)計(jì)階段完成,接下來就是我們的軟件層次了。一:端口引腳的配置1 未使用的引腳:不用連接,配置為輸出模式并驅(qū)動(dòng)到任一狀態(tài)(高電平或低電平);配置為輸入模式并使用外部電阻(約10 k)拉至VDD

2021-11-11 08:45:36

:-------------------------------------------------關(guān)于本次大賽的幾個(gè)重要規(guī)則和流程:一、提交作品1. 提交設(shè)計(jì):以帖子形式將設(shè)計(jì)階段作品(方案設(shè)計(jì)說明、原理圖等)發(fā)布至社區(qū)全志科技小組進(jìn)行評(píng)審。2.

2022-11-08 17:16:08

公共接地點(diǎn)與外部地相連。為了減小電源的邊緣輻射,電源/地平面應(yīng)遵循20H設(shè)計(jì)原則,即地平面尺寸比電源平面尺寸大20H(見圖2),這樣邊緣場(chǎng)輻射強(qiáng)度可下降70%。 圖2 20H原則示意圖 在電路板設(shè)計(jì)階段

2018-10-09 10:53:41

和提高干擾接收器的敏感度,但已延伸到其他學(xué)科領(lǐng)域。 在印制電路板設(shè)計(jì)階段對(duì)電磁兼容考慮將減少電路在樣機(jī)中發(fā)生電磁干擾,問題的種類包括公共阻抗耦合、串?dāng)_、高頻載流導(dǎo)線產(chǎn)生的輻射和通過由互連布線和印制線形成的回路拾取噪聲等,那么在進(jìn)行EMC測(cè)試時(shí)具體有哪些規(guī)范需要我們注意?

2019-01-16 15:54:40

如何在PCB設(shè)計(jì)階段處理好EMC及其EMI的問題呢?有什么解決辦法嗎?

2023-04-06 15:52:59

Modbus傳感器是怎樣采集協(xié)議的?如何對(duì)485電路的程序進(jìn)行測(cè)試?

2021-09-28 08:47:07

如何對(duì)EEPROM芯片的讀寫速度進(jìn)行測(cè)試呢?如何對(duì)EEPROM芯片的全片有效性進(jìn)行測(cè)試呢?

2022-02-24 07:53:45

SWM32SRET6芯片有哪些特點(diǎn)呢?如何對(duì)SWM32SRET6芯片進(jìn)行測(cè)試呢?

2021-12-21 06:27:20

如何滿足工程過電壓與絕緣配合設(shè)計(jì)階段的建模需要?

2021-11-05 06:18:36

芯片;5. 可測(cè)試AD/DA芯片,放大器,比較器,三極管,光耦等集成電路芯片;6. 驅(qū)動(dòng)程序支持win2000/ winxp/ win2003/win7;7. 測(cè)試儀軟硬件獨(dú)立設(shè)計(jì),芯片庫(kù)可在線實(shí)時(shí)更新, 簡(jiǎn)單易用;8.可根據(jù)用戶提供的芯片,進(jìn)行測(cè)試(需定制);

2013-04-28 16:17:07

分析儀,記錄啟動(dòng)電流。如果在啟動(dòng)過程中發(fā)災(zāi)難性故障,至少可以獲得一些數(shù)據(jù),以調(diào)查可能的原因。 四 數(shù)字和模擬控制電路調(diào)試 這個(gè)階段檢查控制邏輯,這可能是設(shè)計(jì)中最重要、也是最復(fù)雜的部分,必須測(cè)試補(bǔ)償

2016-01-12 11:08:55

嵌入式測(cè)試階段:根據(jù)軟件開發(fā)階段不同,可分為平臺(tái)測(cè)試、單元測(cè)試、集成測(cè)試和系統(tǒng)測(cè)試。1.平臺(tái)測(cè)試包括硬件電路測(cè)試、操作系統(tǒng)及底層驅(qū)動(dòng)程序測(cè)試等等。硬件電路測(cè)試需要所對(duì)應(yīng)的測(cè)試工具來進(jìn)行測(cè)試。操作系統(tǒng)

2021-10-27 06:44:20

為了盡早地在產(chǎn)品設(shè)計(jì)階段解決電磁兼容問題,設(shè)計(jì)師需要進(jìn)行基于理論分析和協(xié)作設(shè)計(jì)的EMC仿真。本文采用AnsoftSIwave軟件,仿真分析了PCB中高頻諧波干擾對(duì)智能電器控制板電磁兼容性產(chǎn)生

2022-01-10 09:17:48

本文是機(jī)甲大師機(jī)器人控制的系列博客之一。在軟件單元階段完成后,進(jìn)行軟件單元測(cè)試。本文內(nèi)容與軟件架構(gòu)設(shè)計(jì)階段相對(duì)應(yīng)。文章目錄1 開發(fā)階段2 模型單元測(cè)試2.1 電機(jī)控制子系統(tǒng)測(cè)試2.2 舵機(jī)控制子系統(tǒng)

2021-08-18 08:10:23

求助工程師們幫助,怎么做好電路部分設(shè)計(jì),我目前是做一個(gè)傳感器的前放,因?yàn)槭亲霎a(chǎn)品的開發(fā),現(xiàn)在還是設(shè)計(jì)階段,我想知道怎么能做好電路的設(shè)計(jì),從做產(chǎn)品開發(fā)測(cè)試的角度看,需要注意哪些方面,在電路原理圖設(shè)計(jì)好

2015-06-18 21:49:49

因素正同時(shí)給設(shè)計(jì)和設(shè)計(jì)人員帶來深刻影響。設(shè)計(jì)電源是一個(gè)復(fù)雜的過程,涉及到多個(gè)步驟。我們簡(jiǎn)單將電源設(shè)計(jì)工作流程分為10個(gè)階段,提供每個(gè)階段的測(cè)試小貼士。希望我們這份電源設(shè)計(jì)全攻略對(duì)您有所裨益,讓您的測(cè)試

2016-08-03 21:16:24

結(jié)果及完成測(cè)試過程文檔的歸檔;3、協(xié)助項(xiàng)目設(shè)計(jì)評(píng)審和疑難問題解決,在各設(shè)計(jì)階段協(xié)助進(jìn)行技術(shù)評(píng)審,指出設(shè)計(jì)缺陷并提出解決方案 ;4、研究電力行業(yè)相關(guān)監(jiān)測(cè)設(shè)備新技術(shù)、標(biāo)準(zhǔn)、認(rèn)證等方面知識(shí),并定期輸出技術(shù)規(guī)范

2017-05-31 11:05:16

在電路設(shè)計(jì)階段,NuMicro?系列微控制器需要預(yù)留哪些接口進(jìn)行編程,量產(chǎn),程序調(diào)試?

2020-12-22 07:06:58

鋰離子電池進(jìn)行充電時(shí)有哪三個(gè)階段策略?為什么需要進(jìn)行3個(gè)階段?

2021-03-11 07:10:17

ICT測(cè)試 SMTSMT的高組裝密度使得傳統(tǒng)的測(cè)試方法陷入困境,在電路和SMB(Surface Mount Board)設(shè)計(jì)階段就進(jìn)行可測(cè)性設(shè)計(jì)是當(dāng)今業(yè)界所普遍采用的方法,其目的是提高產(chǎn)品質(zhì)量,降低測(cè)試

2008-06-28 19:18:51 62

62 長(zhǎng)期以來,人們往往注重對(duì)項(xiàng)目后期竣工結(jié)算,決算階段的造價(jià)控制,而忽視了對(duì)設(shè)計(jì)階段的造價(jià)控制。事實(shí)上,設(shè)計(jì)費(fèi)用一般只占建設(shè)成本的1%-2%,而其卻往往能影響70%-90%左右的

2009-12-28 15:39:27 5

5 輸變電工程設(shè)計(jì)階段的

2008-11-20 15:47:42 519

519 如何在設(shè)計(jì)階段考慮降低XILINX的功耗,最近Xilinx發(fā)布了不少關(guān)于使用serdes,ISERDES/OSERDES等基元設(shè)計(jì)一些很具創(chuàng)意性的接口。

2017-02-11 14:15:19 1986

1986 電源測(cè)量小貼士 10 個(gè)設(shè)計(jì)階段

2017-10-16 15:44:48 6

6 電源測(cè)量的小貼士 10 個(gè)設(shè)計(jì)階段

2017-10-19 09:03:49 4

4 這樣一類集成電路,它們屬于非邊界掃描器件,位于電路板邊緣連接器和由DSP芯片形成的邊界掃描鏈之間。這部分器件的功能測(cè)試難以進(jìn)行。首先,這些帶DSP的電路板有獨(dú)立的時(shí)序,所以不能單獨(dú)采用傳統(tǒng)的通過外部接口輸入測(cè)試矢量的方法進(jìn)行測(cè)試;其次,邊界掃描

2017-11-03 15:11:40 3

3 現(xiàn)代的電子產(chǎn)品往往將小信號(hào)模擬電路、數(shù)字電路和功率電路緊密地整合在一塊PCB上,電路布局不僅要滿足電路性能要求,還受結(jié)構(gòu)設(shè)計(jì)的約束,同時(shí)要符合EMC規(guī)范,這些都給地回路的布置帶來了很大的挑戰(zhàn)。在多重約束的限制下,設(shè)計(jì)階段PCB地回路布線會(huì)存在不確定的因素,需要在測(cè)試階段檢驗(yàn)。

2018-06-20 19:56:00 1919

1919

當(dāng)PCB設(shè)計(jì)人員所設(shè)計(jì)的產(chǎn)品投入生產(chǎn)時(shí),幾乎都會(huì)遇到一些問題。這些問題通常與生產(chǎn)制程和產(chǎn)量有關(guān),或是PCB組裝中出現(xiàn)了問題,導(dǎo)致產(chǎn)品報(bào)廢或大量的返工。當(dāng)出現(xiàn)上述情況時(shí),產(chǎn)品需重回設(shè)計(jì)階段進(jìn)行必要的設(shè)計(jì)改版,以便其能符合預(yù)定的生產(chǎn)制程。

2018-02-14 07:43:00 792

792 飛利信表示,公司芯片屬于自主可控芯片。目前,公司芯片處于光刻(平面型晶體管和集成電路生產(chǎn)中的一個(gè)主要工藝)的最后階段。

2018-07-18 14:32:02 5676

5676 在最原始的測(cè)試過程中,對(duì)集成電路(Integrated Circuit,IC)的測(cè)試是依靠有經(jīng)驗(yàn)的測(cè)試人員使用信號(hào)發(fā)生器、萬用表和示波器等儀器來進(jìn)行測(cè)試的。這種測(cè)試方法測(cè)試效率低,無法實(shí)現(xiàn)大規(guī)模

2018-11-29 08:13:00 8872

8872

該視頻演示了兩種在設(shè)計(jì)原型設(shè)計(jì)階段以及終端系統(tǒng)設(shè)計(jì)和集成階段監(jiān)控功耗的方法。

該演示將Maxim解決方案作為電源的一部分進(jìn)行了比較并利用了......

2018-11-26 07:08:00 2153

2153 這十年來我做過小的嵌入式系統(tǒng),大的電信系統(tǒng)以及基于web的系統(tǒng)。使用過C ++,Ruby,Java和Python等。這篇文章中的經(jīng)驗(yàn)教訓(xùn)旨在幫助減少編碼、測(cè)試和調(diào)試三個(gè)階段的bug。

2019-02-11 16:52:45 3182

3182 一。產(chǎn)品定位與市場(chǎng)分析階段,二、用戶研究與分析階段,三、架構(gòu)設(shè)計(jì)階段,四、原型設(shè)計(jì)階段,五、界面設(shè)計(jì)階段,六、界面輸出階段,七、可用性測(cè)試階段,八、完成工作階段,九、產(chǎn)品上線,十、分析報(bào)告及優(yōu)化方案

2019-04-29 17:38:16 6

6 電路仿真是一種計(jì)算機(jī)軟件模擬電子電路或系統(tǒng)行為的技術(shù)。無需實(shí)際構(gòu)建電路或系統(tǒng),即可對(duì)新設(shè)計(jì)進(jìn)行測(cè)試,評(píng)估和診斷。在實(shí)際進(jìn)行電路級(jí)故障排除之前,電路仿真可能是對(duì)系統(tǒng)進(jìn)行故障排除以收集數(shù)據(jù)的有用工具。這

2023-01-31 17:36:24 2506

2506 AMD在SC19大會(huì)上做了一次演講。AMD在開發(fā)以及IPC增長(zhǎng)方面對(duì)ZEN 3和Epyc發(fā)表了一些有趣的評(píng)論。首先,AMD提到ZEN 3架構(gòu)設(shè)計(jì)階段已經(jīng)完成。如今可以將AMD的設(shè)計(jì)和發(fā)布階段視為發(fā)布時(shí)間表。在這里,您可能會(huì)期望ZEN2的迭代更新。

2019-11-26 14:58:01 2667

2667 軟件測(cè)試的開發(fā)階段:特點(diǎn)和分類

2020-06-29 10:55:12 4405

4405 在一個(gè)應(yīng)用中,印刷電路板的成本對(duì)產(chǎn)品的整體價(jià)格有著巨大的影響。因此,重要的是納入有助于減少此支出的所有步驟。下面列出了一些步驟,通過在 PCB 設(shè)計(jì)階段進(jìn)行簡(jiǎn)單的更改,您就可以降低總體應(yīng)用程序成本

2020-11-18 19:19:54 2658

2658 為了盡早地在產(chǎn)品設(shè)計(jì)階段解決電磁兼容問題,設(shè)計(jì)師需要進(jìn)行基于理論分析和協(xié)作設(shè)計(jì)的EMC仿真。

2020-11-24 16:32:24 856

856 單粒子翻轉(zhuǎn)(Single-Event Upsets,SEU)指的是元器件受輻照影響引起電位狀態(tài)的跳變,“0”變成“1”,或者“1”變成“0”,但一般不會(huì)造成器件的物理性損傷。正因?yàn)椤皢瘟W臃D(zhuǎn)”頻繁出現(xiàn),因此在芯片設(shè)計(jì)階段需要重點(diǎn)關(guān)注。這也是這篇文章的重點(diǎn)。

2020-11-29 11:07:10 5926

5926 談到芯片,首先想到的一定是性能,功耗,價(jià)格,成熟度,生態(tài)圈兼容性等。但是只針對(duì)芯片本身的話,是看芯片內(nèi)部有什么運(yùn)算能力,比如處理器,浮點(diǎn)器,編解碼器,數(shù)字信號(hào)處理器,圖形加速器,網(wǎng)絡(luò)加速器等,還要

2021-02-20 15:42:21 13398

13398

? 集成電路產(chǎn)品EMC測(cè)試系統(tǒng)是嚴(yán)格按照IEC 61967和IEC 62132系列進(jìn)行設(shè)計(jì),整套系統(tǒng)的功能和性能不僅能夠滿足上述兩大類標(biāo)準(zhǔn)要求的測(cè)試項(xiàng)目。而且在系統(tǒng)的關(guān)鍵技術(shù)具有創(chuàng)新性、實(shí)踐可行性

2020-12-28 10:41:57 3984

3984 景嘉微:下一代圖形處理芯片處于后端設(shè)計(jì)階段 景嘉微在接受投資機(jī)構(gòu)調(diào)研時(shí)對(duì)外表示,公司下一代圖形處理芯片目前處于后端設(shè)計(jì)階段,后續(xù)的研發(fā)進(jìn)展將在定期報(bào)告中進(jìn)行披露。景嘉微表示,“公司一直高度重視員工

2021-01-13 11:38:00 2490

2490 集成電路芯片的測(cè)試(ICtest)分類包括:分為晶圓測(cè)試(wafertest)、芯片測(cè)試(chiptest)和封裝測(cè)試(packagetest)。

2021-07-14 14:31:23 10128

10128

嵌入式測(cè)試階段:根據(jù)軟件開發(fā)階段不同,可分為平臺(tái)測(cè)試、單元測(cè)試、集成測(cè)試和系統(tǒng)測(cè)試。1.平臺(tái)測(cè)試包括硬件電路測(cè)試、操作系統(tǒng)及底層驅(qū)動(dòng)程序測(cè)試等等。硬件電路測(cè)試需要所對(duì)應(yīng)的測(cè)試工具來進(jìn)行測(cè)試。操作系統(tǒng)

2021-10-20 09:59:09 9

9 硬件上設(shè)計(jì)階段完成,接下來就是我們的軟件層次了。一:端口引腳的配置1 未使用的引腳:不用連接,配置為輸出模式并驅(qū)動(dòng)到任一狀態(tài)(高電平或低電平);配置為輸入模式并使用外部電阻(約10 k)拉至VDD

2021-11-05 20:06:02 11

11 在需求分析階段,硬件電路的設(shè)計(jì)已經(jīng)較為全面的進(jìn)行了說明。接下來我們將細(xì)化硬件設(shè)計(jì)部分。一.低功耗外圍器件的選型1.電容:所有電容在電流通過電介質(zhì)時(shí)都會(huì)產(chǎn)生少量電荷損失,即使完全充電后也是如此,稱為

2021-11-05 20:21:02 13

13 封裝測(cè)試是將生產(chǎn)出來的合格晶圓進(jìn)行切割、焊線、塑封,使芯片電路與外部器件實(shí)現(xiàn)電氣連接,并為芯片提供機(jī)械物理保護(hù),并利用集成電路設(shè)計(jì)企業(yè)提供的測(cè)試工具,對(duì)封裝完畢的芯片進(jìn)行功能和性能測(cè)試。

2022-08-08 15:32:46 7445

7445 按照產(chǎn)品所處的階段,又分為設(shè)計(jì)階段的 DFMEA(Design Failure Mode and Effects Analysis)和生產(chǎn)階段的PFMEA(Process Failure Mode and Effects Analysis)。

2022-09-06 11:09:23 6572

6572 硬件測(cè)試是電子產(chǎn)品開發(fā)過程很重要一環(huán),產(chǎn)品在設(shè)計(jì)階段很多潛在的問題只看表面是看不出來的,各模塊電路必須有針對(duì)性的測(cè)試才能將問題扼殺在搖籃里。因此,硬件測(cè)試工作顯得尤其重要。

2022-09-19 12:58:43 2271

2271

包含了硬件PCB板的測(cè)試流程、測(cè)試方法、及所需的工具。硬件測(cè)試是電子產(chǎn)品開發(fā)過程很重要一環(huán),產(chǎn)品在設(shè)計(jì)階段很多潛在的問題只看表面是看不出來的,各模塊電路必須有針對(duì)性的測(cè)試才能將問題扼殺在搖籃里。因此,硬件測(cè)試工作顯得尤其重要。

2022-10-08 14:43:59 41

41 這是一個(gè)關(guān)于系統(tǒng)構(gòu)成和芯片架構(gòu)的高層次描達(dá)文件,涉及芯片的高層次操作、引腳分配與定義、軟件編程模型、可測(cè)性、寄存器定義以及應(yīng)用模型等。

2022-11-10 20:48:51 12733

12733 (WaferTest)階段。這個(gè)階段的測(cè)試可能在晶圓工廠內(nèi)進(jìn)行,也可能送往附近的代理測(cè)試廠商執(zhí)行。生產(chǎn)方工程師會(huì)使用自動(dòng)測(cè)試儀器(ATE)運(yùn)行芯片設(shè)計(jì)方給出的程序,粗暴的把芯片分成好的/壞的這兩部分,壞的會(huì)直接被舍棄,如果這個(gè)階

2023-01-17 16:40:49 3391

3391 根據(jù) ISO 26262 標(biāo)準(zhǔn)的相關(guān)要求, ISO 26262-3 概念設(shè)計(jì)階段是汽車安全生命 周期的起始階段, 旨在為道路車輛在系統(tǒng)級(jí)別上的相關(guān)安全活動(dòng)提供支持和指導(dǎo) 。

2023-03-25 09:28:21 1188

1188 在印制電路板設(shè)計(jì)階段對(duì)電磁兼容考慮將減少電路在樣機(jī)中發(fā)生電磁干擾。問題的種類包括公共阻抗耦合、串?dāng)_、高頻載流導(dǎo)線產(chǎn)生的輻射和通過由互連布線和印制線形成的回路拾取噪聲等。

2023-04-07 09:15:06 458

458 集成電路測(cè)試可以按照測(cè)試目的、測(cè)試內(nèi)容、按照器件開發(fā)和制造階段分類。參照需要達(dá)到的測(cè)試目的對(duì)集成電路測(cè)試進(jìn)行分類,可以分為:驗(yàn)證測(cè)試、制造測(cè)試、老化測(cè)試、入廠測(cè)試等。按照測(cè)試所涉及內(nèi)容,集成電路測(cè)試

2023-04-25 15:58:33 688

688 從這里開始我們進(jìn)入SDLC的設(shè)計(jì)階段,根據(jù)之前所有的要求開始計(jì)劃產(chǎn)品的設(shè)計(jì)階段,包括硬件上的配置、選型等,還包括軟件上的服務(wù)器設(shè)計(jì)、數(shù)據(jù)庫(kù)關(guān)系等確定。

2023-04-28 14:18:43 4673

4673

集成電路芯片的測(cè)試(ICtest)分類包括:分為晶圓測(cè)試(wafertest)、芯片測(cè)試(chiptest)和封裝測(cè)試(packagetest)。

2023-06-14 15:33:36 1031

1031 BMS是個(gè)功能特別復(fù)雜的電子設(shè)備。在其設(shè)計(jì)階段,需要對(duì)原型的功能進(jìn)行驗(yàn)證;在生產(chǎn)階段,需要對(duì)產(chǎn)品的功能進(jìn)行測(cè)試;如果設(shè)備出現(xiàn)故障,需要進(jìn)行檢修。在這些階段都需要有對(duì)應(yīng)的測(cè)試設(shè)備來支持。BMS的功能

2021-12-17 15:32:07 2719

2719

算法(ControllerModel)刷入目標(biāo)板,那如何帶著位于PC端的PlantModel一起進(jìn)行閉環(huán)測(cè)試呢?圖1PiL階段的閉環(huán)測(cè)試流程下面我會(huì)為以一個(gè)座艙溫度

2022-12-15 10:31:30 740

740

集成電路(Integrated Circuit,簡(jiǎn)稱IC)芯片的三大測(cè)試環(huán)節(jié)包括前端測(cè)試、中間測(cè)試和后端測(cè)試。

2023-06-26 14:30:05 1527

1527 芯片封裝測(cè)試是在芯片制造過程的最后階段完成的一項(xiàng)重要測(cè)試,它主要用于驗(yàn)證芯片的封裝質(zhì)量和功能可靠性。芯片封裝測(cè)試包括以下主要方面。

2023-06-28 13:49:56 1970

1970 芯片測(cè)試座,又稱為IC測(cè)試座、芯片測(cè)試夾具或DUT夾具,是一種用于測(cè)試集成電路(IC)或其他各種類型的半導(dǎo)體器件的設(shè)備。它為芯片提供了一個(gè)穩(wěn)定的物理和電氣接口,使得在不造成芯片或測(cè)試設(shè)備損傷的情況下

2023-10-07 09:29:44 1790

1790

IC芯片測(cè)試基本原理是什么? IC芯片測(cè)試是指對(duì)集成電路芯片進(jìn)行功能、可靠性等方面的驗(yàn)證和測(cè)試,以確保其正常工作和達(dá)到設(shè)計(jì)要求。IC芯片測(cè)試的基本原理是通過引入測(cè)試信號(hào),檢測(cè)和分析芯片的響應(yīng),以判斷

2023-11-09 09:18:37 1803

1803 芯片電學(xué)測(cè)試如何進(jìn)行?包含哪些測(cè)試內(nèi)容? 芯片電學(xué)測(cè)試是對(duì)芯片的電學(xué)性能進(jìn)行測(cè)試和評(píng)估的過程。它是保證芯片質(zhì)量和可靠性的重要環(huán)節(jié),通過測(cè)試可以驗(yàn)證芯片的功能、性能和穩(wěn)定性,從而確保芯片可以在實(shí)際

2023-11-09 09:36:48 1244

1244 每種芯片在設(shè)計(jì)階段都會(huì)對(duì)一些核心指標(biāo)參數(shù)進(jìn)行提前的計(jì)算規(guī)劃

2023-11-09 17:21:16 974

974

如何用集成電路芯片測(cè)試系統(tǒng)測(cè)試芯片老化? 集成電路芯片老化測(cè)試系統(tǒng)是一種用于評(píng)估芯片長(zhǎng)期使用后性能穩(wěn)定性的測(cè)試設(shè)備。隨著科技的進(jìn)步和電子產(chǎn)品的廣泛應(yīng)用,人們對(duì)芯片的可靠性要求日益增高,因此老化測(cè)試

2023-11-10 15:29:05 1186

1186 為什么需要芯片靜態(tài)功耗測(cè)試?如何使用芯片測(cè)試工具測(cè)試芯片靜態(tài)功耗? 芯片靜態(tài)功耗測(cè)試是評(píng)估芯片功耗性能和優(yōu)化芯片設(shè)計(jì)的重要步驟。在集成電路設(shè)計(jì)中,靜態(tài)功耗通常是指芯片在不進(jìn)行任何操作時(shí)消耗的功率

2023-11-10 15:36:27 2001

2001 。本文將詳細(xì)解釋為什么要進(jìn)行芯片上下電功能測(cè)試,以及測(cè)試的重要性。 首先,芯片上下電功能測(cè)試是確保芯片按照設(shè)計(jì)要求正確工作的重要手段。芯片是電子產(chǎn)品的核心部件,如果其中的電路設(shè)計(jì)有錯(cuò)誤或缺陷,將導(dǎo)致芯片在上電或

2023-11-10 15:36:30 1135

1135 分選機(jī)主要應(yīng)用于集成電路設(shè)計(jì)階段中的驗(yàn)證環(huán)節(jié)和封裝測(cè)試階段的成品測(cè)試環(huán)節(jié),主要用途為

2023-11-15 10:17:55 463

463

車規(guī)芯片為什么要進(jìn)行三溫測(cè)試? 車規(guī)芯片,也被稱為汽車惡劣環(huán)境芯片,是一種專門用于汽車電子系統(tǒng)的集成電路芯片。車規(guī)芯片需要進(jìn)行三溫測(cè)試,是因?yàn)槠嚬ぷ鳝h(huán)境極其復(fù)雜,溫度變化范圍廣,從極寒的寒冷地區(qū)到

2023-11-21 16:10:48 4018

4018 在技術(shù)日新月異的時(shí)代,芯片作為科技發(fā)展的核心,其性能和可靠性至關(guān)重要。作為芯片測(cè)試領(lǐng)域的領(lǐng)軍企業(yè),是德科技以其深入的專業(yè)知識(shí)和前沿的技術(shù)創(chuàng)新,引領(lǐng)著測(cè)試行業(yè)的發(fā)展。我們不僅在芯片設(shè)計(jì)階段提供精準(zhǔn)

2023-12-13 16:15:03 282

282

設(shè)計(jì)驗(yàn)證與優(yōu)化:電路仿真允許工程師在設(shè)計(jì)階段對(duì)電路進(jìn)行模擬測(cè)試,從而驗(yàn)證設(shè)計(jì)的正確性和可行性。這有助于在實(shí)際制造之前發(fā)現(xiàn)并解決潛在的設(shè)計(jì)問題,避免成本高昂的后期修改。同時(shí),通過仿真可以優(yōu)化電路性能,提高電路的效率、穩(wěn)定性和可靠性。

2024-03-29 14:12:20 2440

2440 WAT需要標(biāo)注出測(cè)試未通過的裸片(die),只需要封裝測(cè)試通過的die。

FT是測(cè)試已經(jīng)封裝好的芯片(chip),不合格品檢出。WAT和FT很多項(xiàng)目是重復(fù)的,F(xiàn)T多一些功能性測(cè)試。WAT需要探針接觸測(cè)試點(diǎn)(pad)

2024-04-17 11:37:20 581

581

隨著集成電路技術(shù)的飛速發(fā)展,芯片作為現(xiàn)代電子設(shè)備的核心組件,其性能和質(zhì)量對(duì)于整個(gè)系統(tǒng)的穩(wěn)定性和可靠性具有至關(guān)重要的影響。因此,在芯片生產(chǎn)過程中,出廠測(cè)試和ATE(自動(dòng)測(cè)試設(shè)備)測(cè)試成為了確保芯片質(zhì)量的關(guān)鍵環(huán)節(jié)。本文將詳細(xì)介紹芯片的出廠測(cè)試和ATE測(cè)試是如何進(jìn)行的。

2024-04-19 10:31:45 1361

1361

、產(chǎn)品開發(fā)周期、標(biāo)準(zhǔn)要求和降低成本,同樣也給設(shè)計(jì)和設(shè)計(jì)人員帶來巨大影響。電源設(shè)計(jì)是一項(xiàng)復(fù)雜的工作,分成許多步驟。在本指南中,我們將根據(jù)簡(jiǎn)單的工作流程,提供 10 個(gè)設(shè)計(jì)階段每個(gè)階段的測(cè)試小貼士。希望能讓您的測(cè)試更高效

2024-04-25 09:06:07 8

8 HUSTEC-DC-2010分立器件測(cè)試儀,是我司團(tuán)隊(duì)結(jié)合多年半導(dǎo)體器件測(cè)試經(jīng)驗(yàn)而研發(fā)的,可以應(yīng)用于多種場(chǎng)景,如: ? 測(cè)試分析(功率器件研發(fā)設(shè)計(jì)階段的初始測(cè)試) 失效分析(對(duì)失效器件進(jìn)行測(cè)試分析

2024-05-20 16:50:33 339

339

? 融入“制造意識(shí)”(Manufacturing Awareness)的設(shè)計(jì)是一種設(shè)計(jì)哲學(xué),它強(qiáng)調(diào)在產(chǎn)品設(shè)計(jì)和開發(fā)過程中對(duì)制造過程的理解和考慮。這種設(shè)計(jì)方法的目的是減少設(shè)計(jì)階段到生產(chǎn)階段的轉(zhuǎn)換時(shí)間

2024-06-18 16:51:16 937

937

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論