在考慮EMI控制時,設(shè)計工程師及PCB板級設(shè)計工程師首先應(yīng)該考慮IC芯片的選擇。集成電路的某些特征如封裝類型、偏置電壓和芯片的:工藝技術(shù)(例如CMoS、ECI)等都對電磁干擾有很大的影響。下面將著重探討IC對EMI控制的影響。

2014-05-26 11:25:07 1726

1726 IC設(shè)計不同于一般的板級電子設(shè)計,由于流片的投資更大,復(fù)雜度更高,系統(tǒng)性更強(qiáng),所以學(xué)習(xí)起來也有些更有意思的地方。那么如何才能成為一個優(yōu)秀的IC設(shè)計工程師?

2015-09-08 08:43:16 1693

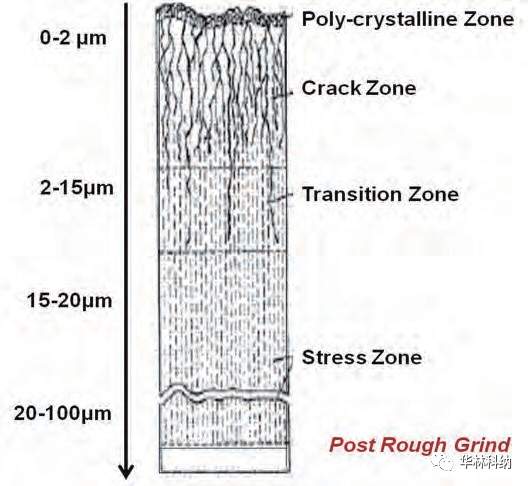

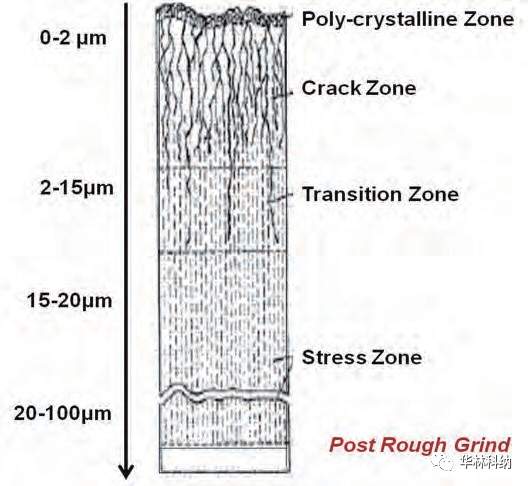

1693 經(jīng)過前端工藝處理并通過晶圓測試的晶圓將從背面研磨(Back Grinding)開始后端處理。背面研磨是將晶圓背面磨薄的工序,其目的不僅是為了減少晶圓厚度,還在于聯(lián)結(jié)前端和后端工藝以解決前后兩個工藝

2023-05-12 12:39:18 764

764

經(jīng)過前端工藝處理并通過晶圓測試的晶圓將從背面研磨(Back Grinding)開始后端處理。背面研磨是將晶圓背面磨薄的工序,其目的不僅是為了減少晶圓厚度,還在于聯(lián)結(jié)前端和后端工藝以解決前后兩個工藝

2023-05-22 12:44:23 691

691

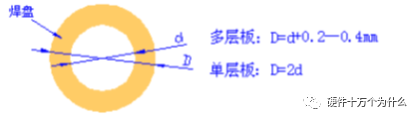

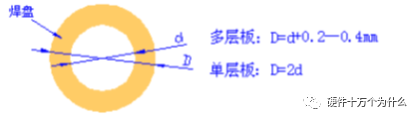

1. 目的 規(guī)范產(chǎn)品的PCB焊盤設(shè)計工藝,規(guī)定PCB焊盤設(shè)計工藝的相關(guān)參數(shù),使得PCB 的設(shè)計滿足可生產(chǎn)性、可測試性、安規(guī)、EMC、EMI 等的技術(shù)規(guī)范要求,在產(chǎn)品設(shè)計過程中構(gòu)建產(chǎn)品的工藝、技術(shù)

2023-08-09 09:19:52 1068

1068

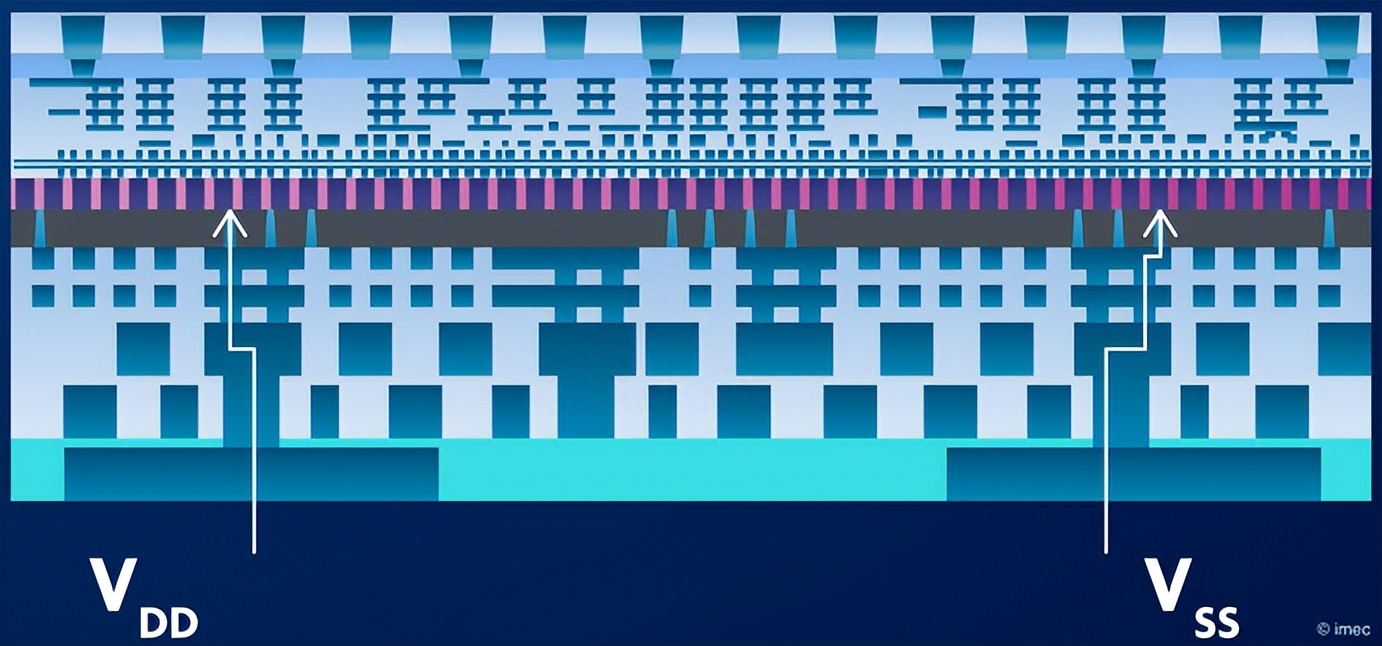

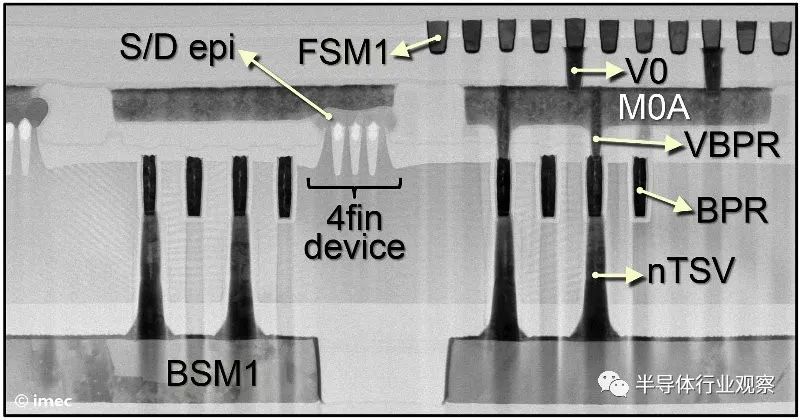

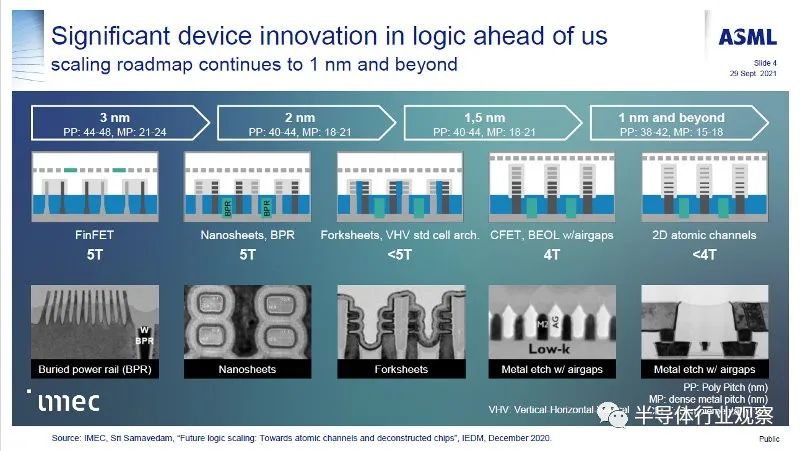

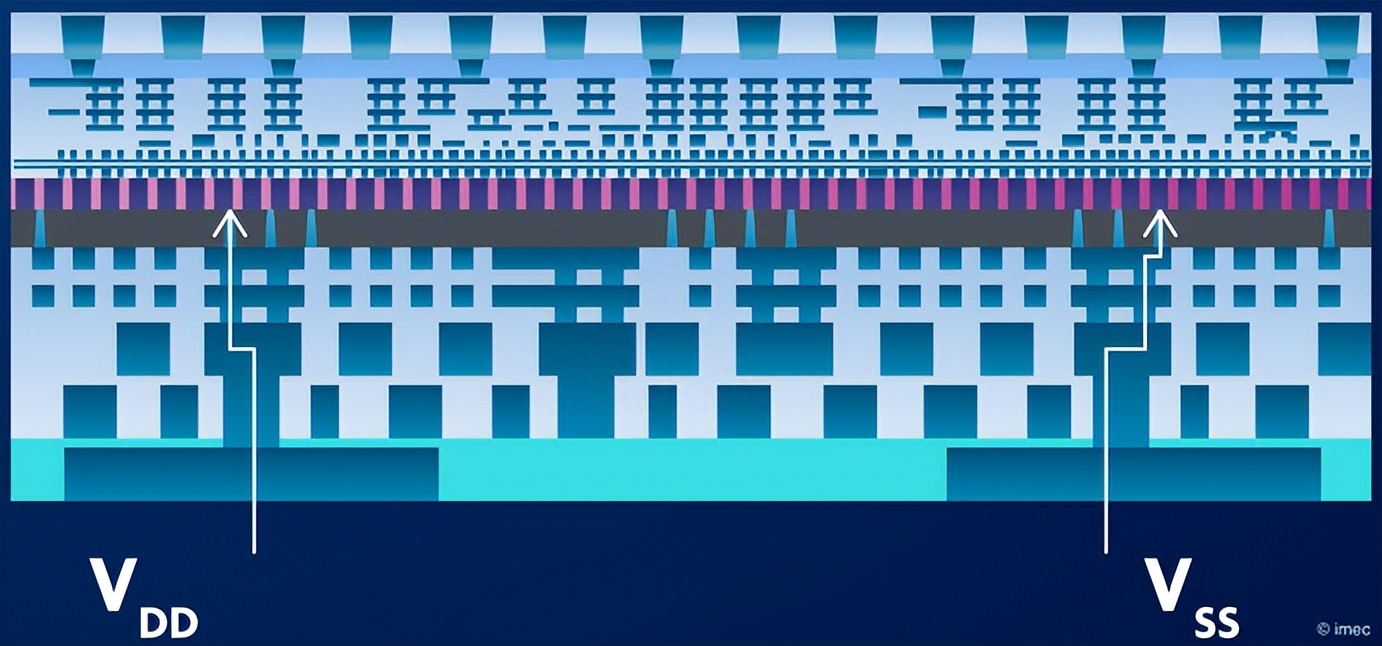

來源:IMEC Imec強(qiáng)調(diào)了背面供電在高性能計算方面的潛力,并評估了背面連接的選項 背面供電:下一代邏輯的游戲規(guī)則改變者 背面供電打破了在硅晶圓正面處理信號和電力傳輸網(wǎng)絡(luò)的長期傳統(tǒng)。通過背面供電

2023-09-05 16:39:38 464

464

GPS防盜IC安防監(jiān)控降壓芯片,GPS安防監(jiān)控降壓IC、GPS汽車GPS防盜器IC供電IC,摩托車GPS防盜器IC電源芯片、GPS定位防盜器IC電定位器IC供電芯片,GPS防盜IC安防監(jiān)控供電IC

2018-09-27 09:37:23

JD招聘IC設(shè)計工程師 3年以上Mix-signal IC設(shè)計工作經(jīng)驗;具備傳感器后續(xù)處理電路(調(diào)壓/放大/比較)、SPI、I2C等接口IC電路的項目經(jīng)驗為佳,央企創(chuàng)業(yè)平臺,股權(quán)激勵可談。工作內(nèi)容

2016-03-27 18:28:20

卡模塊,最后嵌入IC卡塑料基板。 隨著IC產(chǎn)品制造工藝的提高以及高性能LSI的涌現(xiàn),IC智能卡不斷向功能多樣化、智能化的方向發(fā)展,以滿足人們對方便、迅捷的追求。然而使用過程中出現(xiàn)的密碼校驗錯誤、數(shù)據(jù)

2018-11-05 15:57:30

、5年以上IC Layout經(jīng)驗。有先進(jìn)工藝模擬版圖經(jīng)驗者優(yōu)先; 3、能熟練使用主流IC版圖設(shè)計工具,如Virtuso、Laker等、版圖驗證工具,如Calibre, 能看懂不同F(xiàn)oundry的DRC

2015-11-18 11:10:56

PCB和系統(tǒng)級設(shè)計中的EMI控制。在考慮EMI控制時,設(shè)計工程師及PCB板級設(shè)計工程師首先應(yīng)該考慮IC芯片的選擇。集成電路的某些特征如封裝類型、偏置電壓和芯片的:工藝技術(shù)(例如CMoS、ECI)等都對電磁干擾有很大的影響。下面將著重探討IC對EMI控制的影響。

2019-05-31 07:28:26

大家好,我學(xué)FPGA也有幾個月了,都是學(xué)習(xí)板上的設(shè)計,現(xiàn)在可以隨便的編寫一些簡單的邏輯;我琢磨著以后想往IC設(shè)計工程師這個職位走,不知道IC設(shè)計工程師除了邏輯編寫的能力以外,還有哪方面的知識。或者有什么好的資料可以推薦一下。。。謝謝!

2012-05-25 01:02:01

設(shè)計工程師三類。另外,設(shè)計環(huán)節(jié)還需要工藝接口工程師、應(yīng)用工程師、驗證工程師等。IC版圖設(shè)計師 IC版圖設(shè)計師的主要職責(zé)是通過EDA設(shè)計工具,進(jìn)行集成電路后端的版圖設(shè)計和驗證,最終產(chǎn)生送交供集成電路

2012-02-06 10:23:07

為進(jìn)行公司所設(shè)計的硬件產(chǎn)品之軟件開發(fā),例如驅(qū)動程序等。 一、 IC 設(shè)計領(lǐng)域簡介(一)模擬與混號訊號電路設(shè)計IC 電路可分為為模擬 IC 與數(shù)字 IC 兩大類,以及兩者兼具的混合訊號等三種。模擬與數(shù)字

2011-12-19 16:11:48

`關(guān)于PCB設(shè)計工藝邊及拼板技術(shù)規(guī)范,更多電子設(shè)計知識掃描微信二維碼關(guān)注@電子設(shè)計創(chuàng)新`

2017-11-15 09:23:49

RFIC/射頻IC設(shè)計工程師QQ:2361362181射頻:崗位職責(zé): 射頻集成電路設(shè)計,包括前仿、版圖和后仿。 任職資格: 1、 電子等相關(guān)專業(yè)碩士或博士; 2、 有無線射頻芯片的相關(guān)設(shè)計經(jīng)驗,有

2013-04-08 17:25:04

STD6N95K5IC本體背面有刮痕,會影響使用嗎?

2023-08-05 06:05:38

,全日制碩士及以上學(xué)歷;2、5年以上模擬IC設(shè)計工作經(jīng)驗;3、需具有ADC,DAC豐富流片經(jīng)驗;4、具有扎實的模擬電路基礎(chǔ),精通OPA,Bandgap,LDO等基礎(chǔ)模塊設(shè)計;熟練掌握Virtuoso

2020-07-02 14:14:59

`書籍:《炬豐科技-半導(dǎo)體工藝》文章:IC制造工藝編號:JFSJ-21-046作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html摘要:集成電路的制造主要包括以下工藝

2021-07-08 13:13:06

)動手編譯APP【Thunderboard Sense試用體驗】之(三)供電問題梳理【Thunderboard Sense試用體驗】之(四)體驗官方Demo【Thunderboard Sense試用

2017-06-16 11:17:09

資深版圖設(shè)計工程師(電源管理 DC-DC)-上海職位描述:崗位職責(zé):--負(fù)責(zé)模擬IC版圖設(shè)計和驗證,有電源類以及高壓工藝經(jīng)驗者優(yōu)先--能與工藝廠和模擬IC設(shè)計工程師溝通以確保產(chǎn)品的高質(zhì)量任職要求

2014-09-29 16:15:19

資深版圖設(shè)計工程師(電源管理 DC-DC)-上海職位描述:崗位職責(zé):--負(fù)責(zé)模擬IC版圖設(shè)計和驗證,有電源類以及高壓工藝經(jīng)驗者優(yōu)先--能與工藝廠和模擬IC設(shè)計工程師溝通以確保產(chǎn)品的高質(zhì)量任職要求

2014-10-10 15:34:08

招聘IC設(shè)計工程師3年以上數(shù)字或模擬 IC設(shè)計工作經(jīng)驗;具備反向IC電路的項目經(jīng)驗為佳,央企創(chuàng)業(yè)平臺,股權(quán)激勵可談。工作內(nèi)容主要為參與公司設(shè)計項目管理及新型電路設(shè)計。工作地點為江蘇無錫。聯(lián)系人

2016-05-02 17:40:23

此文檔介紹了一些常用的PCB設(shè)計工藝規(guī)范

2018-08-09 15:20:14

單面板設(shè)計工藝技巧

2012-09-02 23:02:09

是什么推動著高精度模擬芯片設(shè)計?如何利用專用晶圓加工工藝實現(xiàn)高性能模擬IC?

2021-04-07 06:38:35

大家看一下這個電路設(shè)計合理不?能否使IC正常供電

2015-09-19 11:07:05

1、模擬IC設(shè)計工程師25-60W(電源方向:初級、高工、經(jīng)理、 目前需求職位如下1、模擬IC設(shè)計工程師25-60W(電源方向:初級、高工、經(jīng)理、目前需求職位如下:1、模擬IC設(shè)計工程師25-60W

2017-06-29 16:47:51

1、模擬IC設(shè)計工程師25-60W(電源方向:初級、高工、經(jīng)理、目前需求職位如下:1、模擬IC設(shè)計工程師25-60W(電源方向:初級、高工、經(jīng)理、總監(jiān))均有需求,坐標(biāo):深圳/上海/武漢/長沙/南京

2017-06-07 11:37:18

目前需求職位如下:1、模擬IC設(shè)計工程師25-60W(電源方向:初級、高工、經(jīng)理、總監(jiān))均有需求,坐標(biāo):深圳/上海/武漢/長沙/南京/蘇州/杭州/成都/西安/北京。2、資深模擬IC設(shè)計(混合信號

2017-05-22 11:11:08

目前需求職位如下:1、模擬IC設(shè)計工程師25-60W(電源方向:初級、高工、經(jīng)理、總監(jiān))均有需求,坐標(biāo):深圳/上海/武漢/長沙/南京/蘇州/杭州/成都/西安/北京。2、資深模擬IC設(shè)計(混合信號

2017-05-23 14:21:55

目前需求職位如下:1、模擬IC設(shè)計工程師25-60W(電源方向:初級、高工、經(jīng)理、總監(jiān))均有需求,坐標(biāo):深圳/上海/武漢/長沙/南京/蘇州/杭州/成都/西安/北京。2、資深模擬IC設(shè)計(混合信號

2017-06-19 15:09:33

數(shù)字IC設(shè)計工程師-上海職位要求: 1、電子類相關(guān)專業(yè),本科或本科以上學(xué)歷 2、熟悉數(shù)字IC設(shè)計流程,熟練掌握verilogHDL coding,DC/PT/FT等工具 3、有FPGA設(shè)計經(jīng)驗者優(yōu)先

2015-06-15 10:06:11

數(shù)字IC設(shè)計工程師工作地點:北京主要職責(zé):1. 確定芯片的解決方案及架構(gòu),選擇算法,進(jìn)行優(yōu)化。2. 對芯片進(jìn)行模塊劃分及Micro Architecture的定義。3.較大規(guī)模ASIC芯片的頂層

2013-04-23 10:17:25

數(shù)字IC設(shè)計工程師筆試面試經(jīng)典100題(大部分有答案)

2012-08-20 20:25:20

本篇簡單羅列了作為數(shù)字IC設(shè)計工程師的必備知識和學(xué)習(xí)建議,希望對本科高年級和研究生階段有志從事數(shù)字IC設(shè)計的學(xué)生有所幫助。數(shù)字集成電路基礎(chǔ)CMOS制造工藝器件(二極管、場效應(yīng)管)導(dǎo)線門電路組合邏輯(反相器、與門、或門、異或)時序邏輯(La...

2021-07-29 08:31:04

模擬IC設(shè)計工程師工作地點:上海。杭州,廣東職位職能:集成電路IC設(shè)計/應(yīng)用工程師 職位描述:職責(zé):從事模擬電路與系統(tǒng)的規(guī)格制定、電路設(shè)計、版圖規(guī)劃與檢查、實際電路的驗證、實際產(chǎn)品的測試方法,檢查

2013-04-22 12:11:11

模擬IC設(shè)計工程師(IP)-杭州崗位職責(zé):1.參與模擬IP規(guī)格定義。2.負(fù)責(zé)模擬IP電路設(shè)計,仿真,驗證。3.負(fù)責(zé)模擬版圖設(shè)計。4.協(xié)助芯片模擬IP的測試。5.參與制定與模擬IP相關(guān)文檔。崗位要求

2015-01-22 15:45:00

江蘇外企招IC版圖設(shè)計工程師兩年以上工作經(jīng)驗暫不招應(yīng)屆實習(xí)生英語或者日語熟練咨詢顧問-席亞軍,簡歷委托郵箱:xyj@intebankjp.comQQ:1291937747MSN:bmhr012@hotmail.com

2012-04-06 14:00:59

、SCHEMATIC及LAYOUT數(shù)據(jù)檢查及備份,確保送出的數(shù)據(jù)準(zhǔn)確無誤; 4、協(xié)助設(shè)計工程師完成表單及設(shè)計文件歸檔等其它相關(guān)工作。 崗位要求:1、幾年模擬IC版圖設(shè)計經(jīng)驗; 2、掌握virtuso

2014-03-06 15:07:57

、SCHEMATIC及LAYOUT數(shù)據(jù)檢查及備份,確保送出的數(shù)據(jù)準(zhǔn)確無誤; 4、協(xié)助設(shè)計工程師完成表單及設(shè)計文件歸檔等其它相關(guān)工作。 崗位要求:1、幾年模擬IC版圖設(shè)計經(jīng)驗; 2、掌握virtuso

2014-03-14 15:49:23

、SCHEMATIC及LAYOUT數(shù)據(jù)檢查及備份,確保送出的數(shù)據(jù)準(zhǔn)確無誤; 4、協(xié)助設(shè)計工程師完成表單及設(shè)計文件歸檔等其它相關(guān)工作。 崗位要求:1、幾年模擬IC版圖設(shè)計經(jīng)驗; 2、掌握virtuso

2014-03-18 17:14:33

本帖最后由 723290508 于 2014-1-3 10:10 編輯

用來電池供電低壓報警的IC,萬分感謝!

2013-11-23 09:51:06

供電系統(tǒng)是否容易讓人管理,系統(tǒng)設(shè)計工程師怎么解決負(fù)載電源的管理問題?

2021-03-11 07:22:41

`背金工藝之前 ,背面如何處理? 最近做片時出現(xiàn)異常,如下圖中間靠下為異常區(qū)域,合金沒合好,請問如何避免,謝謝!!`

2011-01-07 11:10:24

表面安裝pcb設(shè)計工藝淺談

2012-08-20 20:13:21

模擬IC設(shè)計工程師-西安1.參與IC產(chǎn)品的框架設(shè)計和Spec定義;2.獨立負(fù)責(zé)產(chǎn)品電路設(shè)計及仿真驗證工作,指導(dǎo)后端工程師完成版圖設(shè)計;3.協(xié)助完成測試方案,提供測試支持,并對測試結(jié)果進(jìn)行分析;4.

2017-07-13 17:42:23

QQ:2361362181 郵箱:carry.wang@yaxunhr.com 工作地點:珠海。觸控ic設(shè)計工程師職位要求:1 、電子工程、微電子等相關(guān)專業(yè)本科以上學(xué)歷; 2 、熟練掌握

2013-04-08 17:21:49

獵頭職位:模擬IC設(shè)計工程師【深圳】崗位職責(zé):1.負(fù)責(zé)電源管理芯片相關(guān)模擬電路的設(shè)計與驗證;2.負(fù)責(zé)電源方面新技術(shù)的研究與開發(fā)。任職要求:1.碩士及以上學(xué)歷,電子、微電子相關(guān)專業(yè),3年以上

2017-06-16 10:54:20

請問技術(shù)創(chuàng)新是如何推動設(shè)計工藝發(fā)展的?

2021-04-21 06:46:39

[p=***,***,***eft]資深/模擬IC設(shè)計工程師(信號鏈 AD -DA PLL sderes)-武漢 上海 成都 深圳 北京 杭州[p=***,***,***eft]職位描述[p

2018-09-19 14:18:29

資深RFIC/射頻IC設(shè)計工程師-上海 廣東射頻:崗位職責(zé): 射頻集成電路設(shè)計,包括前仿、版圖和后仿。 任職資格: 1、 電子等相關(guān)專業(yè)碩士或博士,有海外經(jīng)驗,有帶團(tuán)隊經(jīng)驗優(yōu)先。 2、 有無線射頻

2013-09-26 16:47:46

資深模擬IC/模擬IC設(shè)計工程師(電源DC-DC)-上海 深圳 昆山崗位職責(zé):1、電源管理芯片模擬電路的設(shè)計;2、協(xié)助layout工程師規(guī)劃layout,檢查驗收layout;3、協(xié)助系統(tǒng)工程師完成

2015-05-15 11:25:32

資深模擬IC設(shè)計工程師(DC-DC)工作地點:上海崗位職責(zé):1、參與DC-DC及相關(guān)產(chǎn)品的規(guī)格定義;2、負(fù)責(zé)DC-DC及相關(guān)產(chǎn)品的系統(tǒng)設(shè)計及線路設(shè)計;3、負(fù)責(zé)DC-DC及相關(guān)產(chǎn)品的版圖規(guī)劃;4、參與

2014-03-06 14:58:23

資深模擬IC設(shè)計工程師(音頻功放IC )-上海 工作職責(zé): 1、參與模擬IC規(guī)格制定,負(fù)責(zé)電路設(shè)計和仿真,編寫電路設(shè)計文檔;2、協(xié)助版圖設(shè)計工程師完成模擬IC版圖設(shè)計;3、協(xié)助測試工程師制定測試方案

2015-05-18 15:10:57

PCB設(shè)計是每個電子工程師入門必備的技能,本資料為國內(nèi)知名企業(yè)的PCB板設(shè)計工藝規(guī)范,包括布線、鋪銅和穿孔等流程的詳細(xì)教程,并且對于工藝邊和和拼板也有在具體要求下的設(shè)計技巧,讓您在PCB設(shè)計

2019-03-15 14:22:13

芯片背面研磨,上海IC研磨,IC集成電路研磨公司,宜特檢測集成電路背面研磨(Backside Polishing)工作原理:透過自動研磨機(jī),從芯片背面進(jìn)行研磨將Si基材磨薄至特定厚度后再進(jìn)行拋光

2018-10-24 10:57:21

霍爾IC芯片的制造工藝霍爾IC傳感器是一種磁性傳感器,通過感應(yīng)磁場的變化,輸出不同種類的電信號。霍爾IC芯片主要有三種制造工藝,分別為 Bipolar、CMOS 和 BiCMOS 工藝,不同工藝的產(chǎn)品具有不同的電參數(shù)與磁參數(shù)特性。霍爾微電子柯芳(***)現(xiàn)為您分別介紹三種不同工藝產(chǎn)品的特點。

2016-10-26 16:48:22

高級射頻IC設(shè)計工程師工作地點:廣州 珠海職位描述:負(fù)責(zé)無線通信芯片射頻電路設(shè)計,包括LNA、Mixer、PA、VCO等;編寫相關(guān)技術(shù)文檔;3.獨立承擔(dān)或配合完成版圖、芯片測試等工作;職位要求

2014-03-18 17:47:45

高級模擬IC設(shè)計工程師(LED AC-DC電源)-上海崗位職責(zé):1、模擬電路模塊包括帶隙基準(zhǔn)源、低壓差穩(wěn)壓電路、運放、比較器、振蕩器、鎖相環(huán)等電路設(shè)計,工藝極限仿真,撰寫模塊設(shè)計報告,召開模塊

2015-01-26 16:23:37

高級模擬IC設(shè)計工程師(LED AC-DC電源)-上海崗位職責(zé):1、模擬電路模塊包括帶隙基準(zhǔn)源、低壓差穩(wěn)壓電路、運放、比較器、振蕩器、鎖相環(huán)等電路設(shè)計,工藝極限仿真,撰寫模塊設(shè)計報告,召開模塊

2015-02-28 14:03:37

高級模擬IC設(shè)計工程師(電源DC-DC)-上海 昆山 深圳崗位職責(zé):1、電源管理芯片模擬電路的設(shè)計;2、協(xié)助layout工程師規(guī)劃layout,檢查驗收layout;3、協(xié)助系統(tǒng)工程師完成IC的驗證

2015-03-19 17:15:46

數(shù)字IC設(shè)計工程師崗位要求:(6K-10k)1.電子、通信、電路與系統(tǒng)等相關(guān)專業(yè)大學(xué)本科以上學(xué)歷;2.扎實的數(shù)字電路理論知識,對模擬電路理論有一定了解;3.掌握Verilog等硬件描述語言,熟練

2017-04-13 15:58:15

IC工藝技術(shù)問題 集成電路芯片偏置和驅(qū)動的電源電壓Vcc是選擇IC時要注意的重要問題。從IC電源管腳吸納的電流主要取決于該電壓值以及該IC芯片輸出級

2009-08-27 23:13:38 780

780 采用PC的IC工具降低MEMS設(shè)計方法

鑒于MEMS工藝源自光刻微電子工藝,所以人們很自然會考慮用IC設(shè)計工具來創(chuàng)建MEMS器件的

2010-03-11 14:23:33 467

467 在代工廠網(wǎng)站下載經(jīng)過驗證的Laker工藝文件,從0.5微米到65納米的邏輯、模擬、混合信號、RF、存儲等IC設(shè)計工藝都可支持。

2012-05-04 10:57:53 66

66 邏輯設(shè)計工程師、IC automation設(shè)計工程師筆試題 威盛(VIA)2007最新考題 1、ASIC flow 寫出幾個流程,并用2-3句話簡介,然后列出相應(yīng)的2-3個EDA tools 2、名詞解釋 FIFO,SETUP/HOLD TIME,CPLD,Cache,DFT,

2012-05-24 13:14:18 75

75 可植入、可消化、可互動、可互操作以及支持因特網(wǎng),這些醫(yī)療設(shè)備現(xiàn)在及未來獨特的需求都要求合適的IC工藝技術(shù)與封裝。本文將對醫(yī)療半導(dǎo)體器件采用的雙極性(bipolar)與CMOS工藝進(jìn)

2012-07-16 17:54:57 2873

2873

IC制造工藝方面的資料,學(xué)習(xí)學(xué)習(xí) ,有需要的可以看一下

2015-12-07 11:23:41 0

0 中興通訊結(jié)構(gòu)設(shè)計工藝手冊

2017-10-27 08:57:47 31

31 而mems即微機(jī)電系統(tǒng),是一門新興學(xué)科和領(lǐng)域,跟ic有很大的關(guān)聯(lián),當(dāng)然mems工藝也和cmos工藝會有很大的相似之處,現(xiàn)在的發(fā)展方向應(yīng)該是把二者集成到一套的工藝上來.

對mems不是特別的了)

2018-07-13 14:40:00 19763

19763 IC設(shè)計工程師是一個從事IC開發(fā),集成電路開發(fā)設(shè)計的職業(yè)。隨著中國IC設(shè)計產(chǎn)業(yè)漸入佳境,越來越多的工程師加入到這個新興產(chǎn)業(yè)中。成為IC設(shè)計工程師所需門檻較高,往往需要有良好的數(shù)字電路系統(tǒng)及嵌入系統(tǒng)

2018-04-27 11:26:05 22518

22518 本文首先介紹了ic設(shè)計行業(yè)發(fā)展現(xiàn)狀及工程師工作的內(nèi)容,其次介紹了IC設(shè)計工程師就業(yè)前景及發(fā)展方向的探究,最后闡述了如何才能成為一個優(yōu)秀的ic設(shè)計工程師。

2018-04-27 11:57:40 46729

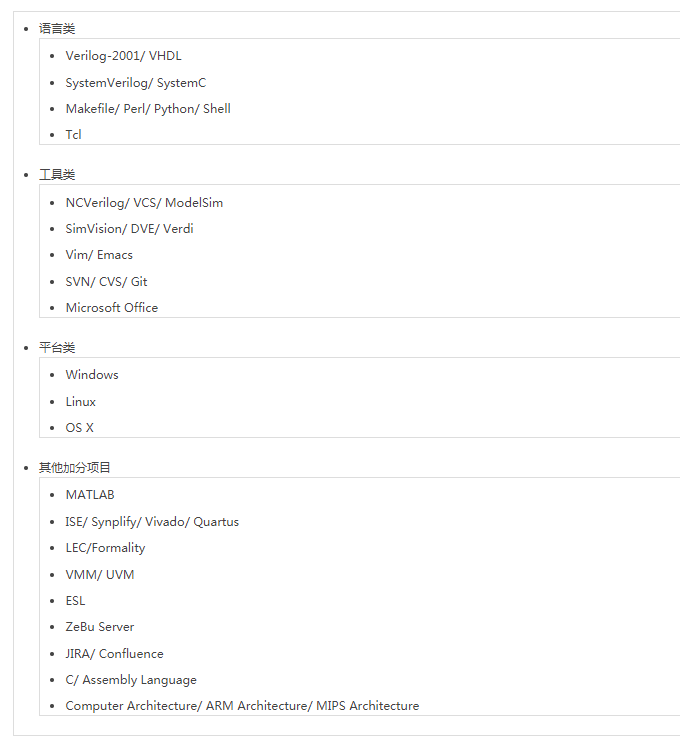

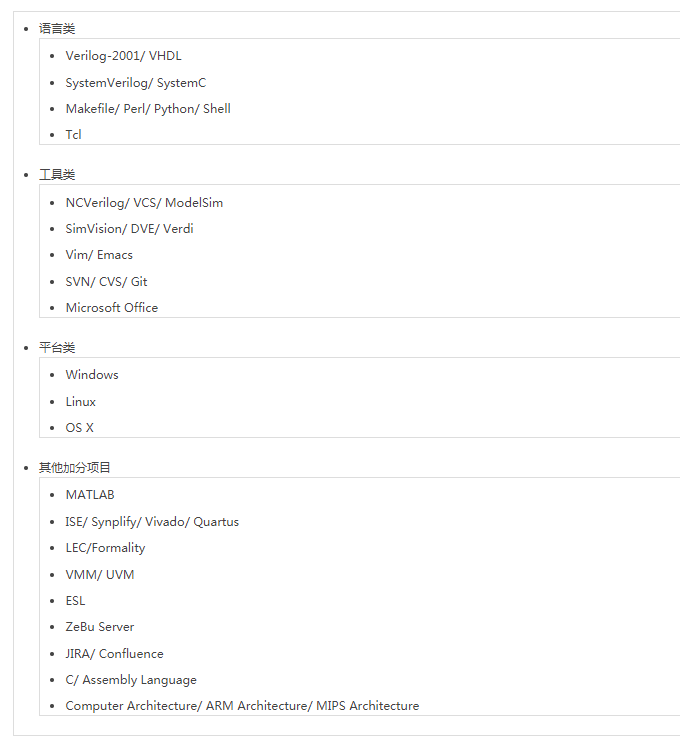

46729 作為一個真正合格的數(shù)字IC設(shè)計工程師,你永遠(yuǎn)都需要去不斷學(xué)習(xí)更加先進(jìn)的知識和技術(shù)。因此,這里列出來的技能永遠(yuǎn)都不會是完整的。我盡量每年都對這個列表進(jìn)行一次更新。

2019-01-04 16:36:38 10828

10828

本文檔詳細(xì)介紹的是PCB的設(shè)計工藝資料應(yīng)用教材免費下載主要內(nèi)容包括了:一。設(shè)計文件格式問題,二.PCB 各層可制造性的應(yīng)用及介紹,三。嘉立創(chuàng)各工藝詳解,四。審廠問題,五。設(shè)計錯誤案例測試

2019-02-25 08:00:00 0

0 華虹半導(dǎo)體的新方案是基于Cadence IC5141 EDA軟件的工藝設(shè)計工具包(PDK),包括PSP SOI和BSIM SOI的射頻模型仿真平臺。此0.2微米射頻SOI工藝設(shè)計工具(PDK)可以

2019-10-21 11:19:02 2688

2688 一文看懂PCB線路板設(shè)計工藝的缺陷都有什么?

2019-08-20 16:32:58 2619

2619 本文檔的主要內(nèi)容詳細(xì)介紹的是5V電源供電的簡易音響功放設(shè)計工程文件和原理圖等資料免費下載。

2019-10-28 08:00:00 18

18 “百花齊放”的繁榮景象。但作為產(chǎn)業(yè)命脈的IC設(shè)計人才,在IC產(chǎn)業(yè)最集中的長三角地區(qū)也僅僅只有幾千人。所以擁有一定工作經(jīng)驗的設(shè)計工程師,目前已成為人才獵頭公司爭相角逐的“寵兒”。

2020-07-13 09:39:41 5125

5125 功率、下電極基底溫度、腔室壓力等參數(shù)對SiC背面通孔的刻蝕速率、選擇比、傾斜角及側(cè)壁光滑度的影響。通過裝片夾具改進(jìn)及工藝條件優(yōu)化,開發(fā)出刻蝕速率為1μm/min、SiC與Ni的選擇比大于60∶1、傾斜角小于85°、側(cè)壁光滑的SiC通孔工藝條件,可用

2020-12-29 14:32:10 2146

2146 功率、下電極基底溫度、腔室壓力等參數(shù)對SiC背面通孔的刻蝕速率、選擇比、傾斜角及側(cè)壁光滑度的影響。通過裝片夾具改進(jìn)及工藝條件優(yōu)化,開發(fā)出刻蝕速率為1μm/min、SiC與Ni的選擇比大于60∶1、傾斜角小于85°、側(cè)壁光滑的SiC通孔工藝條件,可用

2020-12-29 14:34:10 1235

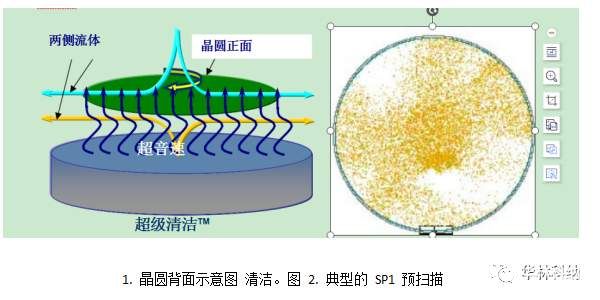

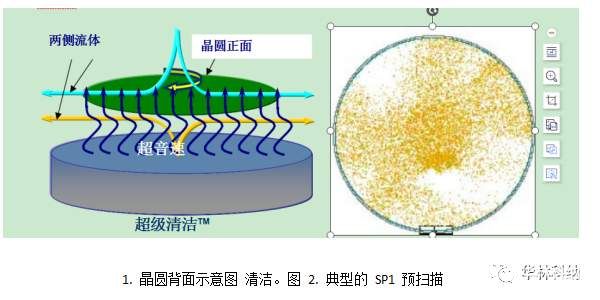

1235 摘要 已經(jīng)為光刻前背面清洗工藝開發(fā)了具有全覆蓋背面兆聲波的單晶片清洗系統(tǒng)。背面顆粒去除效率 (PRE)僅使用 DIW 即可在 ≥65nm 處實現(xiàn)大于 95% 的 Si3N4 顆粒,這表明使用全覆蓋

2022-03-03 14:17:11 664

664

在許多 IC 工藝輔助配件進(jìn)行蝴蝶研磨(背面研磨、研磨),使裝片薄形化,例如:用巧克力蛋糕及智能封裝等。到200~40μm。在珍珠打磨之后,有許多產(chǎn)品需要進(jìn)行工藝,包括:離子布植(離子實現(xiàn))、熱處理

2022-03-23 14:15:31 1096

1096

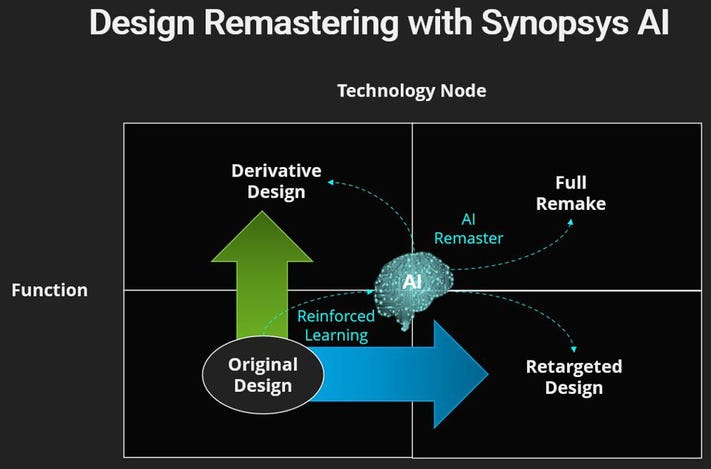

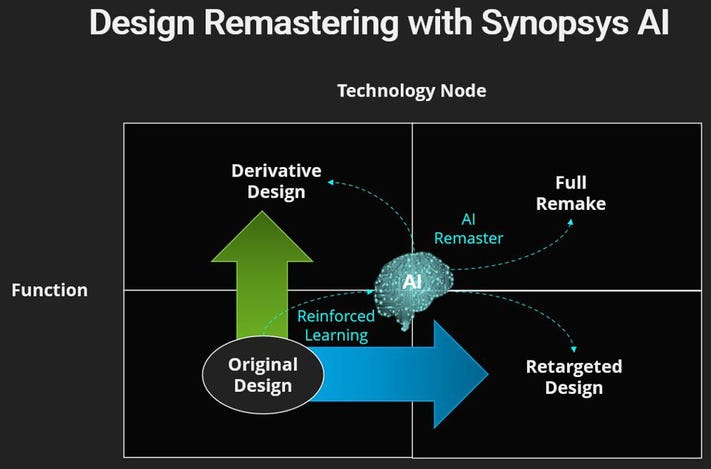

有8%至10%的晶圓廠的產(chǎn)能仍未得到充分利用,也就是約2,000萬至2,500萬片晶圓。對芯片進(jìn)行設(shè)計工藝遷移,將是平衡產(chǎn)能和需求的重要手段。

2023-05-25 14:32:27 751

751

英特爾率先在產(chǎn)品級芯片上實現(xiàn)背面供電技術(shù),使單元利用率超過90%,同時也在其它維度展現(xiàn)了業(yè)界領(lǐng)先的性能。 英特爾宣布在業(yè)內(nèi)率先在產(chǎn)品級測試芯片上實現(xiàn)背面供電(backside power

2023-06-06 16:22:00 314

314 英特爾宣布在業(yè)內(nèi)率先在產(chǎn)品級測試芯片上實現(xiàn)背面供電(backside power delivery)技術(shù),滿足邁向下一個計算時代的性能需求。作為英特爾業(yè)界領(lǐng)先的背面供電 解決方案,PowerVia

2023-06-09 20:10:03 193

193 英特爾表示,它是業(yè)內(nèi)第一個在類似產(chǎn)品的測試芯片上實現(xiàn)背面供電的公司,實現(xiàn)了推動世界進(jìn)入下一個計算時代所需的性能。PowerVia 將于 2024 年上半年在英特爾 20A 工藝節(jié)點上推出,正是英特爾業(yè)界領(lǐng)先的背面供電解決方案。它通過將電源路由移動到晶圓的背面,解決了面積縮放中日益嚴(yán)重的互連瓶頸問題。

2023-06-20 15:39:06 326

326 背面實施流程已通過成功的 SF2 測試芯片流片得到驗證。這是 2nm 設(shè)計的一項關(guān)鍵功能,但可能會受到三星、英特爾和臺積電缺乏布線的限制,而是在晶圓背面布線并使用過孔連接電源線。

2023-07-05 09:51:37 460

460 最近有許多正在全球范圍內(nèi)研究和開發(fā)的技術(shù),例如晶體管GAA(Gate All around)、背面供電以及3D IC。

2023-07-26 18:21:58 1844

1844

背面電力傳輸打破了在硅晶圓正面處理信號和電力傳輸網(wǎng)絡(luò)的長期傳統(tǒng)。通過背面供電,整個配電網(wǎng)絡(luò)被移至晶圓的背面。硅通孔 (TSV) 將電源直接從背面傳送到正面,而無需電子穿過芯片正面日益復(fù)雜的后道工序 (BEOL) 堆棧。

2023-08-30 10:34:20 549

549

PCB設(shè)計工藝指導(dǎo)手冊(v1.0)

2022-12-30 09:20:39 7

7 英特爾在2023年國際電子設(shè)備制造大會上宣布,他們已經(jīng)成功完成了一項名為PowerVia的背面供電技術(shù)的開發(fā)。這個技術(shù)是基于英特爾的最新晶體管研究成果,它實現(xiàn)了互補(bǔ)金屬氧化物半導(dǎo)體場效應(yīng)晶體管

2023-12-11 16:10:42 502

502

PCB 焊盤與孔設(shè)計工藝規(guī)范 1. 目的 規(guī)范產(chǎn)品的PCB焊盤設(shè)計工藝,規(guī)定PCB焊盤設(shè)計工藝的相關(guān)參數(shù),使得PCB 的設(shè)計滿足可生產(chǎn)性、可測試性、安規(guī)、EMC、EMI 等的技術(shù)規(guī)范要求,在產(chǎn)品

2023-12-22 19:40:02 506

506

摘要:論述了傳統(tǒng)的集成電路裝片工藝面臨的挑戰(zhàn)以及現(xiàn)有用DAF膜(DieAttachmentFilm,裝片膠膜)技術(shù)進(jìn)行裝片的局限性;介紹了一種先進(jìn)的、通過噴霧結(jié)合旋轉(zhuǎn)的涂膠模式制備晶圓背面

2023-12-30 08:09:58 337

337

PCBA設(shè)計師們在設(shè)計線路板的時候,往往會預(yù)留工藝邊。這么做得到原因大家知道是為什么嗎?設(shè)計工藝邊有什么好處嗎?今天給大家講解一下PCBA為什么要設(shè)計工藝邊?

2024-03-22 11:45:19 255

255 的邏輯半導(dǎo)體具有10至15層甚至更多的多層布線,細(xì)信號線和粗電源線混合在多層布線中,線路層越來越混亂。為了解決芯片設(shè)計線路層混亂的問題,背面供電網(wǎng)絡(luò)BSPDN技術(shù)的應(yīng)用受到越來越多的關(guān)注。 ? 探索背面供電,解決芯片線路設(shè)計兩難

2023-09-03 00:01:00 1578

1578

電子發(fā)燒友App

電子發(fā)燒友App

評論