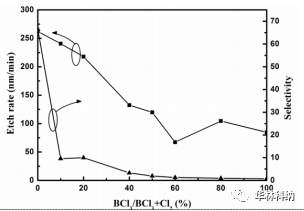

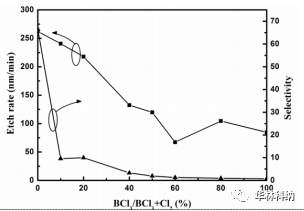

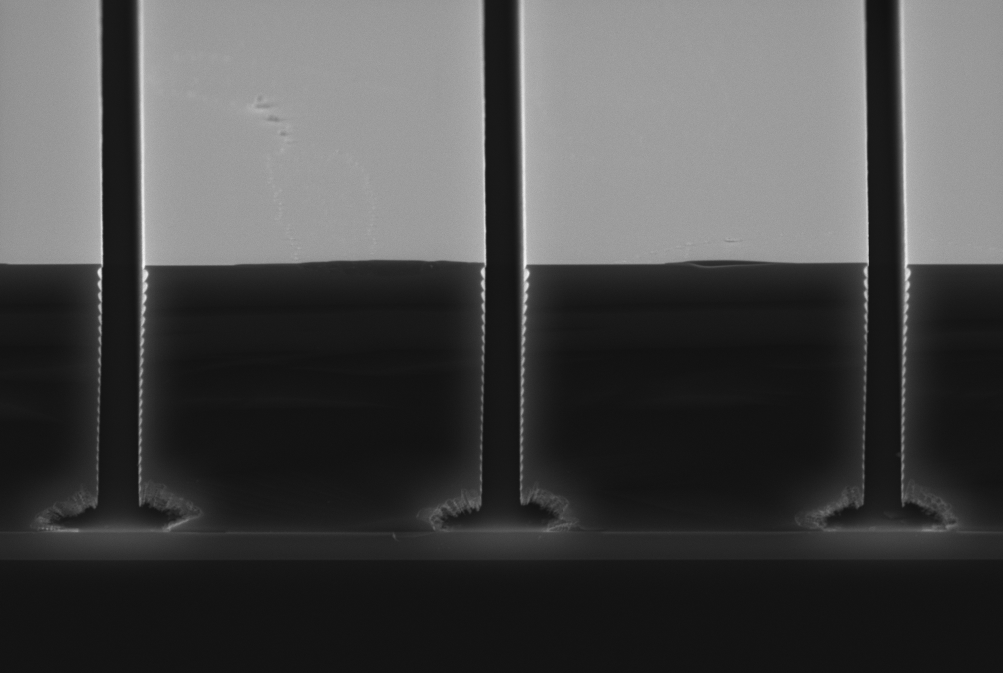

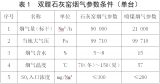

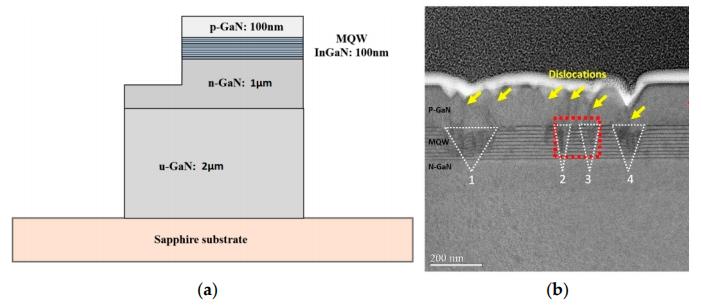

采用電感耦合等離子體刻蝕法對氮化鎵基發光二極管結構進行干法刻蝕,刻蝕氣體為氯氣,添加氣體為三氯化硼。研究了刻蝕氣體流量、電感耦合等離子體功率、射頻功率和室壓等關鍵工藝參數對氮化鎵基發光二極管結構刻蝕

2022-04-26 14:07:28 1762

1762

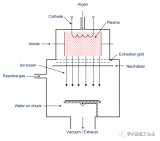

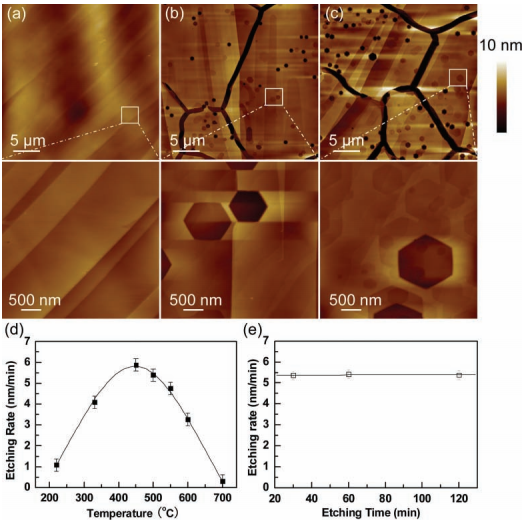

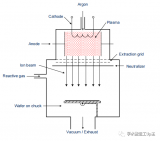

等離子體工藝廣泛應用于半導體制造中。比如,IC制造中的所有圖形化刻蝕均為等離子體刻蝕或干法刻蝕,等離子體增強式化學氣相沉積(PECVD)和高密度等離子體化學氣相沉積 (HDP CVD)廣泛用于電介質

2022-11-15 09:57:31 2626

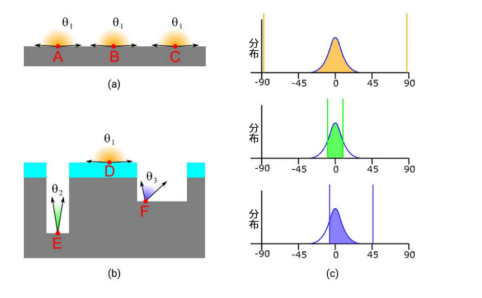

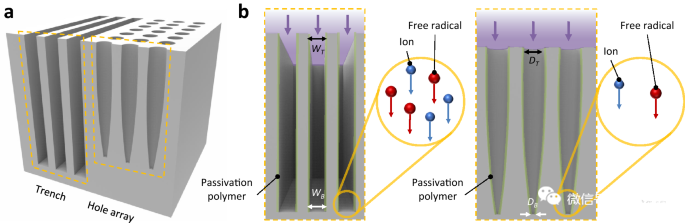

2626 等離子體圖形化刻蝕過程中,刻蝕圖形將影響刻蝕速率和刻蝕輪廓,稱為負載效應。負載效應有兩種:宏觀負載效應和微觀負載效應。

2023-02-08 09:41:26 2467

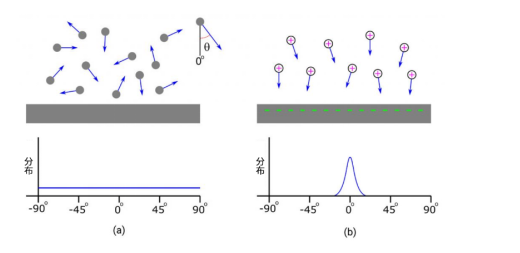

2467 在干法蝕刻中,氣體受高頻(主要為 13.56 MHz 或 2.45 GHz)激發。在 1 到 100 Pa 的壓力下,其平均自由程為幾毫米到幾厘米。

2023-06-20 09:49:16 3694

3694

在半導體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來講講如何采用這個“餅干模具”印出我們想要的“餅干”。這一步驟的重點,在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

2023-08-10 15:06:10 506

506 濕法刻蝕由于精度較差,只適用于很粗糙的制程,但它還是有優點的,比如價格便宜,適合批量處理,酸槽里可以一次浸泡25張硅片,所以有些高校和實驗室,還在用濕法做器件,芯片廠里也會用濕法刻蝕來顯露表面缺陷(defect),腐蝕背面多晶硅。

2023-08-28 09:47:44 891

891

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-09-24 17:42:03 996

996

但是里面也有幾個關鍵的工藝參數需要控制的。同樣Etch GaAs也可以用ICP干法刻蝕的工藝,比濕法工藝效果要好些,側壁也垂直很多。

2023-11-14 09:31:29 407

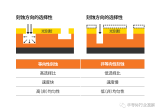

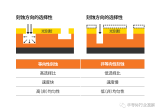

407 干法刻蝕技術是一種在大氣或真空條件下進行的刻蝕過程,通常使用氣體中的離子或化學物質來去除材料表面的部分,通過掩膜和刻蝕參數的調控,可以實現各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結構

2024-01-20 10:24:56 1114

1114

在半導體加工工藝中,常聽到的兩個詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現,有著千絲萬縷的聯系,這一節介紹半導體刻蝕工藝。

2024-01-26 10:01:58 552

552

(干法刻蝕硅)17、 RIE SiO2 (干法刻蝕二氧化硅)18、 RIE Si3N4 (干法刻蝕氮化硅)19、 RIE Al、AlN、Ti、TiN (干法刻蝕金屬,包括干法刻蝕鋁、干法刻蝕氮化

2015-01-07 16:15:47

不同特征尺寸的MOS晶體管,計算了由這些晶體管組成的靜態隨機存儲器(SRAM)單粒子翻轉的臨界電荷Qcrit、LET閾值(LETth),建立了LETth與臨界電荷之間的解析關系,研究了特征工藝尺寸

2010-04-22 11:50:00

AOE刻蝕氧化硅可以,同時這個設備可以刻蝕硅嗎?大致的氣體配比是怎樣的,我這里常規的刻蝕氣體都有,但是過去用的ICP,還沒有用過AOE刻蝕硅,請哪位大佬指點一下,謝謝。

2022-10-21 07:20:28

實現,必須采用微加工技術制造。微加工技術包括硅的體微加工技術、表面微加工技術和特殊微加工技術。體加工技術是指沿著硅襯底的厚度方向對硅襯底進行刻蝕的工藝,包括濕法刻蝕和干法刻蝕,是實現三維結構的重要方法

2016-12-09 17:46:21

技術、表面微加工技術和特殊微加工技術。體加工技術是指沿著硅襯底的厚度方向對硅襯底進行刻蝕的工藝,包括濕法刻蝕和干法刻蝕,是實現三維結構的重要方法。表面微加工是采用薄膜沉積、光刻以及刻蝕工藝,通過在犧牲層

2018-11-12 10:51:35

30 dBm,增益大于5 dB。關鍵詞:碳化硅;金屬?半導體場效應晶體管;犧牲氧化;干法刻蝕;等平面工藝

2009-10-06 09:48:48

表面的預處理 治療2.2 GaN襯底的CMP處理2.3 GaN襯底的ICP干法刻蝕2.4 表面處理后的表面和次表面評估3. 結果和討論3.1 GaN襯底的CMP處理3.2 GaN襯底的ICP干法刻蝕

2021-07-07 10:26:01

新加坡知名半導體晶圓代工廠招聘資深刻蝕工藝工程師和刻蝕設備主管!此職位為內部推薦,深刻蝕工藝工程師需要有LAM 8寸機臺poly刻蝕經驗。刻蝕設備主管需要熟悉LAM8寸機臺。待遇優厚。有興趣的朋友可以將簡歷發到我的郵箱sternice81@gmail.com,我會轉發給HR。

2017-04-29 14:23:25

提到。基于其局限性考慮,干法刻蝕被用于先進電路的小特征尺寸精細刻蝕中。干法刻蝕是一個通稱術語,是指以氣體為主要媒體的刻蝕技術,晶圓不需要液體化學品或沖洗。晶圓在干燥的狀態進出系統。三種干法刻蝕技術

2018-12-21 13:49:20

半導體光刻蝕工藝

2021-02-05 09:41:23

的有氧化爐、沉積設備、光刻機、刻蝕設備、離子注入機、清洗機、化學研磨設備等。以上是今日Enroo關于晶圓制造工藝及半導體設備的相關分享。

2018-10-15 15:11:22

擊穿電壓。同時,還簡要描述了這種器件的制造工藝。關鍵詞:靜電感應晶閘管;埋柵結構;臺面刻蝕;柵陰擊穿;表面缺

2009-10-06 09:30:24

形成電路,而“濕法”刻蝕(使用化學浴)主要用于清潔晶圓。 干法刻蝕是半導體制造中最常用的工藝之一。 開始刻蝕前,晶圓上會涂上一層光刻膠或硬掩膜(通常是氧化物或氮化物),然后在光刻時將電路圖形曝光在晶圓

2017-10-09 19:41:52

基于汽車音響的發展和現狀,本文總結了未來汽車多媒體的5大發展特征、系統理念和系統架構,并對未來汽車多媒體的發展趨勢進行了簡單的介紹。

2021-05-13 06:48:50

煙氣循環流化床干法脫硫工藝系統設計中的技術關鍵

2009-09-11 01:00:04

負責兼顧wet制程設備(清洗&刻蝕&剝離)。任職資格:1. 本科以上學歷,5年以上相關工作經驗;2. 熟悉LTPS工藝者佳,熟悉干法刻蝕段所有設備的工藝需求;3. 具有良好的英文書

2017-02-04 10:04:52

(清洗&刻蝕&剝離)。任職資格:1. 本科以上學歷,5年以上相關工作經驗;2. 熟悉LTPS工藝者佳,熟悉干法刻蝕段所有設備的工藝需求;3. 具有良好的英文書面表達能力,可以使用英語或

2016-12-16 11:45:29

混合液(也稱緩沖氫氟酸液),氮化硅膜的腐蝕液為180 oC左右的熱磷酸;鋁的腐蝕液為磷酸溶液(磷酸:醋酸:硝酸=250:20:3,55 + - 5 oC。 2 干法腐蝕 干法刻蝕分為各向同性刻蝕

2019-08-16 11:11:34

、具有半導體器件工藝開發工作經歷,3年以上工作經驗,4、具有良好的團隊合作精神和進取精神三、半導體刻蝕工藝工程師職責描述:1、 獨立負責干法、濕法刻蝕工藝,進行刻蝕工藝菜單的調試; 2、優化干法刻蝕、濕法

2016-10-26 17:05:04

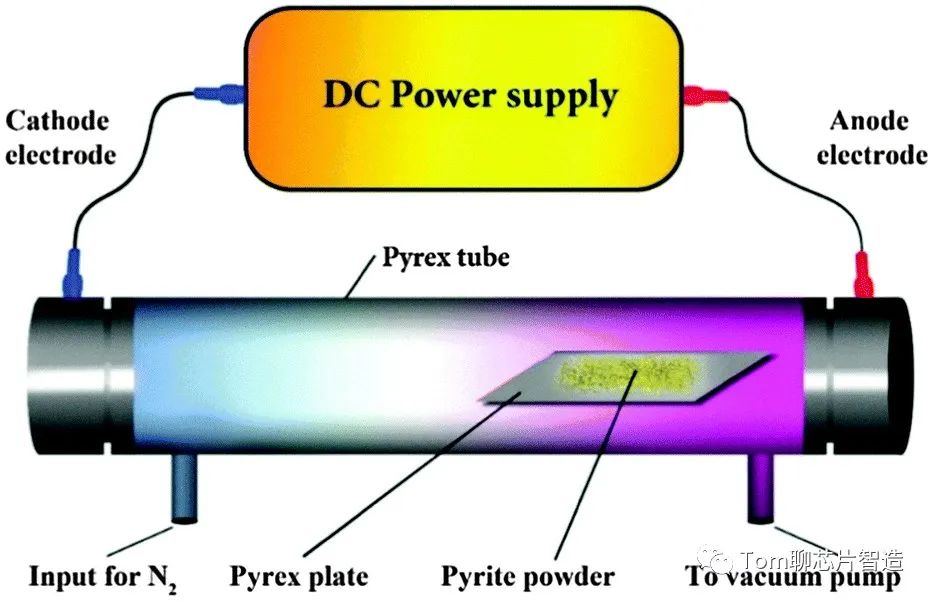

最近需要用到干法刻蝕技術去刻蝕碳化硅,采用的是ICP系列設備,刻蝕氣體使用的是SF6+O2,碳化硅上面沒有做任何掩膜,就是為了去除SiC表面損傷層達到表面改性的效果。但是實際刻蝕過程中總是會在碳化硅

2022-08-31 16:29:50

本帖最后由 gk320830 于 2015-3-7 11:21 編輯

釋放MEMS機械結構的干法刻蝕技術濕法刻蝕是MEMS 器件去除犧牲材料的傳統工藝,總部位于蘇格蘭的Point 35

2013-11-04 11:51:00

煙氣循環流化床干法脫硫工藝系統設計中的技術關鍵:煙氣循環流化床干法脫硫工藝系統設計中的技術關鍵可歸納為“循環流化、一頭一尾”八個字,即物料循環系統、吸收塔系統

2009-05-31 12:39:31 28

28 本文以金屬刻蝕去膠腔為背景,簡述干刻清洗工藝開發和評價過程。針對實際應用中的問題,展開討論。通過實際案例分析,展示了干刻清洗工藝的應用價值。關鍵字:干刻清

2009-12-14 11:06:10 16

16 刻蝕•光刻就是在光刻膠上形成圖形•下一步就是將光刻膠上的圖形通過刻蝕轉移到光刻膠下面的層上•刻蝕工藝分為濕法和干法刻蝕的品質•刻

2010-06-21 17:29:40 72

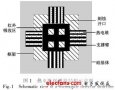

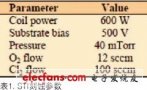

72 摘要 利用Cl2/BCl3/CH4電感應耦合等離子體(ICP)干法刻蝕技術,實現了對AlGaInAs,InP材料的非選擇性刻蝕。AlGaInAs與InP的刻蝕速率分別為820nm/min與770nm/min,獲得了刻蝕深度為4.9μm,垂直光滑的A

2010-11-30 14:58:45 17

17 釋放MEMS機械結構的干法刻蝕技術

濕法刻蝕是MEMS 器件去除犧牲材料的傳統工藝,總部位于蘇格蘭的Point 35 Microstructures在SEMICON C

2009-11-18 09:17:32 880

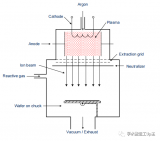

880 干法刻蝕原理

刻蝕作用:去除邊緣PN結,防止上下短路。干法刻蝕原理:利用高頻輝光放電反應,使CF4氣體激活成活性粒子,這些活性

2010-07-18 11:28:20 5637

5637 蘋果設計和工程團隊研究出一種新型的鍵盤刻蝕工藝,利用不同的激光來制作蘋果背光鍵盤.

2011-12-16 09:43:20 764

764

本文實現了一種正面開口的熱電堆結構,采用XeF2作為工作氣體干法刻蝕工藝釋放器件。相對于刻蝕硅,XeF2氣體對鋁等材料的刻蝕速率極小,這樣就可以采用標準CMOS工藝中最常用的材料

2012-05-02 17:26:13 3612

3612

本文在淺溝槽隔離刻蝕過程中發現,當刻蝕腔室上石英窗口的溫度超過85℃時,刻蝕終止出現在300mm晶圓的中心。我們認為刻蝕終止的原因是由于某些低揮發SiOxCly刻蝕產物再淀積。石英

2012-05-04 17:09:37 2803

2803

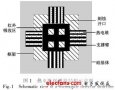

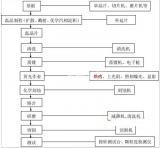

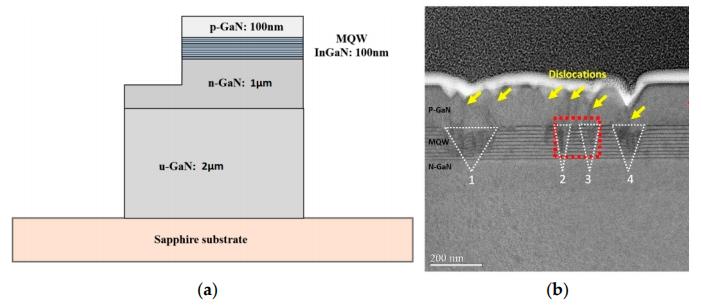

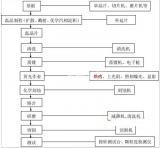

LED 芯片的制造工藝流程:外延片→清洗→鍍透明電極層→透明電極圖形光刻→腐蝕→去膠→平臺圖形光刻→干法刻蝕→去膠→退火→SiO2 沉積→窗口圖形光刻→SiO2 腐蝕→去膠→N極圖形光刻→預清洗→鍍膜→剝離→退火→P 極圖形光刻→鍍膜→剝離→研磨→切割→芯片→成品測試。

2016-08-05 17:45:21 17422

17422

晶體硅太陽能電池生產線刻蝕工序培訓 1、刻蝕的作用及方法;2、刻蝕的工藝設備、操作流程及常用化學品;3、主要檢測項目及標準;4、常見問題及解決方法;5、未來工藝的發展方向;

2017-09-29 10:29:09 24

24 目前市場上,一臺新的干法刻蝕設備使用的射頻源售價大概在1萬美金左右,而維修一臺射頻源的費用一般也要1萬元人民幣以上,可見其費用相當昂貴。本著節約成木的原則,本單位對在使用中出現故障的射頻源進行自主

2018-06-08 09:19:00 7395

7395

左藍微電子(www.sappland.com)專注于MEMS射頻器件的研發,公司擁有國際一流的實驗室設備和工藝加工能力。薄膜沉積,ALN鍍膜,各種光刻工藝,干法刻蝕和濕法刻蝕,先進的圖像分析和測量儀器等。歡迎共享,合作交流!請聯系李志鵬,手機號碼1885168273。

2018-03-13 11:25:00 206

206 左藍微電子專注于MEMS射頻器件的研發,公司擁有國際一流的實驗室設備和工藝加工能力。薄膜沉積,ALN鍍膜,各種光刻工藝,干法刻蝕和濕法刻蝕,先進的圖像分析和測量儀器等。歡迎共享,合作交流!請聯系李志鵬,手機號碼1885168273。

2018-03-13 11:27:45 198

198 反刻是在想要把某一層膜的總的厚度減小時采用的(如當平坦化硅片表面時需要減小形貌特征)。光刻膠是另一個剝離的例子。總的來說,有圖形刻蝕和無圖形刻蝕工藝條件能夠采用干法刻蝕或濕法腐蝕技術來實現。為了復制硅片表面材料上的掩膜圖形,刻蝕必須滿足一些特殊的要求。

2018-12-14 16:05:27 68523

68523 外延片→清洗→鍍透明電極層→透明電極圖形光刻→腐蝕→去膠→平臺圖形光刻→干法刻蝕→去膠→退火→SiO2沉積→窗口圖形光刻→SiO2腐蝕→去膠→N極圖形光刻→預清洗→鍍膜→剝離→退火→P極圖形光刻→鍍膜→剝離→研磨→切割→芯片→成品測試。

2019-03-27 16:58:15 20979

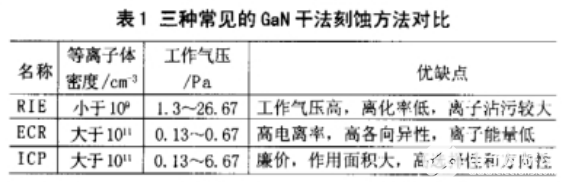

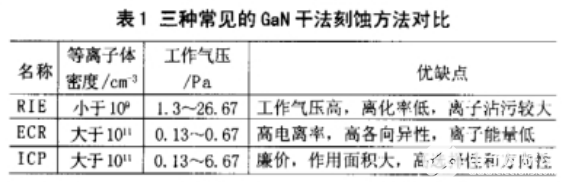

20979 摘要:對比了RIE,ECR,ICP等幾種GaN7干法刻蝕方法的特點。回顧了GaN1法刻蝕領域的研究進展。以ICP刻蝕GaN和AIGaN材料為例,通過工藝參數的優化,得到了高刻蝕速率和理想的選擇比及

2020-12-29 14:39:29 2909

2909

在集成電路的制造過程中,刻蝕就是利用化學或物理方法有選擇性地從硅片表面去除不需要的材料的過程。從工藝上區分,刻蝕可以分為濕法刻蝕和干法刻蝕。前者的主要特點是各向同性刻蝕;后者是利用等離子體來進行

2020-12-29 14:42:58 8547

8547

摘要:簡述了在SiC材料半導體器件制造工藝中,對SiC材料采用干法刻蝕工藝的必要性.總結了近年來SiC干法刻蝕技術的工藝發展狀況. 半導體器件已廣泛應用于各種場合,近年來其應用領域已拓展至許多

2020-12-30 10:30:11 7638

7638

刻蝕速率是指在刻蝕過程中去除硅片表面材料的速度通常用?/min表示, 刻蝕窗口的深度稱為臺階高度。 為了高的產量, 希望有高的刻蝕速率。 在采用單片工藝的設備中, 這是一個很重要的參數。 刻蝕速率由工藝和設備變量決定, 如被刻蝕材料類型、 蝕機的結構配置、 使用的刻蝕氣體和工藝參數設置。

2022-03-15 13:41:59 2907

2907

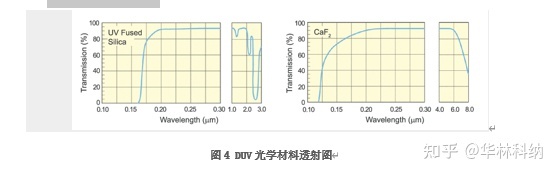

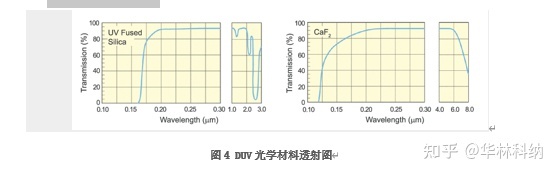

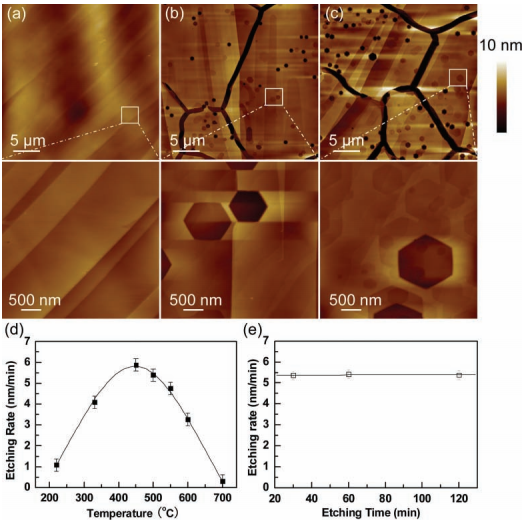

我們華林科納研究了一種干法各向異性刻蝕石墨和石墨烯的方法,能夠通過調整蝕刻參數,如等離子體強度、溫度和持續時間,從邊緣控制蝕刻,蝕刻過程歸因于碳原子的氫化和揮發,蝕刻動力學與甲烷形成一致,這種簡單、干凈、可控且可擴展的技術與現有的半導體處理技術兼容。

2022-05-19 17:06:46 1781

1781

刻蝕室半導體IC制造中的至關重要的一道工藝,一般有干法刻蝕和濕法刻蝕兩種,干法刻蝕和濕法刻蝕一個顯著的區別是各向異性,更適合用于對形貌要求較高的工藝步驟。

2022-06-13 14:43:31 6

6 灰化,簡單的理解就是用氧氣把光刻膠燃燒掉,光刻膠的基本成分是碳氫有機物,在射頻或微波作用下,氧氣電離成氧原子并與光刻膠發生化學反應,生成一氧化碳,二氧化碳和水等,再通過泵被真空抽走,完成光刻膠的去除。

2022-07-21 11:20:17 4871

4871 在 MEMS 制造工藝中,常用的干法刻蝕包括反應離子刻蝕 (Reactive lon Etching, RIE)、深反應離子刻蝕(Deep Reactive lon Etching, DRIE) 和XerF2各向同性蝕刻。

2022-10-10 10:12:15 3281

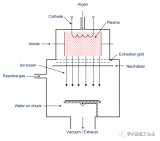

3281 干法刻蝕工藝流程為,將刻蝕氣體注入真空反應室,待壓力穩定后,利用射頻輝光放電產生等離子體;受高速電子撞擊后分解產生自由基,并擴散到圓片表面被吸附。

2022-11-10 09:54:19 3264

3264 濕法刻蝕是集成電路制造工藝最早采用的技術之一。雖然由于受其刻蝕的各向同性的限制,使得大部分的濕法刻蝕工藝被具有各向異性的干法刻蝕替代,但是它在尺寸較大的非關鍵層清洗中依然發揮著重要的作用。

2022-11-11 09:34:18 7251

7251 目前制作硅通孔的主要手段有濕法刻蝕,激光加工和干法刻蝕(深反應離子刻蝕, DRIE )三種。

2022-12-07 11:26:20 282

282 其制造工藝流程如下:首先形成補償側墻 (Offset Spacer),經n+/p+輕摻雜源漏后,選擇性地進行圖形化,在p型源漏區先進行干法刻蝕,使其凹陷適當的深度(30~100nm);然后采用濕法各向異性刻蝕形成“鉆石”形腔(Diamond Cavity,又稱“∑”形狀)

2023-01-05 14:08:31 2145

2145 清洗硅晶片,在其上形成諸如金屬或絕緣膜的薄膜,并且通過光刻形成用于電路圖案的抗蝕劑掩模。然后,通過干法蝕刻進行實際加工,去除并清洗不需要的抗蝕劑,并檢查圖案尺寸。在這里,光刻和干法蝕刻這兩種技術被稱為微細加工。

2023-01-05 14:16:05 2622

2622 刻蝕是移除晶圓表面材料,達到IC設計要求的一種工藝過程。刻蝕有兩種:一種為圖形 化刻蝕,這種刻蝕能將指定區域的材料去除,如將光刻膠或光刻版上的圖形轉移到襯底薄膜 上

2023-02-01 09:09:35 1748

1748 刻蝕速率是測量刻蝕物質被移除的速率。由于刻蝕速率直接影響刻蝕的產量,因此刻蝕速率是一個重要參數。

2023-02-06 15:06:26 3998

3998 干法電極工藝特點是工藝過程簡單、電極更厚、無溶劑化。電極制造過程沒有溶劑參與的固液兩相懸浮液混合,濕涂層的干燥過程,工藝更簡單,更靈活性。

2023-02-12 11:18:26 3200

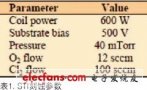

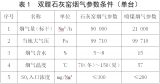

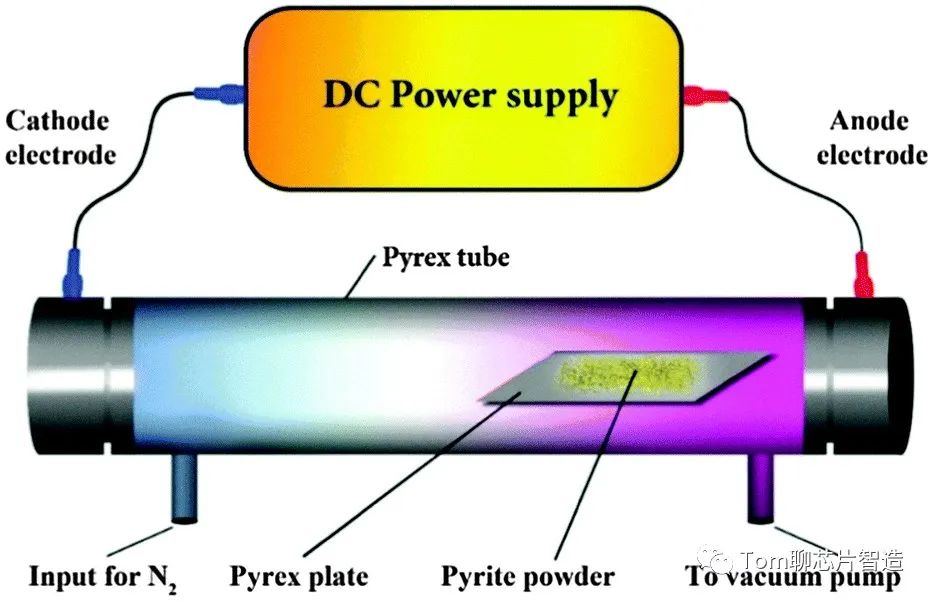

3200 。本研究采用電感耦合等離子體刻

蝕法對氮化鎵基發光二極管結構進行干法刻蝕,刻蝕氣體為氯氣,添加氣體為三氯化硼。研究了刻蝕氣體流量、電感耦合等離

子體功率、射頻功率和室壓等關鍵工藝參數對氮化鎵基發光二極管結構刻蝕性

2023-02-22 15:45:41 0

0 對于濕法刻蝕,大部分刻蝕的終點都取決于時間,而時間又取決于預先設定的刻蝕速率和所需的刻蝕厚度。由于缺少自動監測終點的方法,所以通常由操作員目測終點。濕法刻蝕速率很容易受刻蝕劑溫度與濃度的影響,這種影響對不同工作站和不同批量均有差異,因此單獨用時間決定刻蝕終點很困難,一般釆用操作員目測的方式。

2023-03-06 13:56:03 1773

1773 FinFET三維器件也可以用體硅襯底制作,這需要更好地控制單晶硅刻蝕工藝,如CD、深度和輪廓。

2023-03-30 09:39:18 2461

2461 DRAM柵工藝中,在多晶硅上使用鈣金屬硅化物以減少局部連線的電阻。這種金屬硅化物和多晶硅的堆疊薄膜刻蝕需要增加一道工藝刻蝕W或WSi2,一般先使用氟元素刻蝕鈞金屬硅化合物層,然后再使用氯元素刻蝕多晶硅。

2023-04-07 09:48:16 2200

2200 圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。

2023-04-28 11:24:27 1074

1074

采用干法刻蝕。采用高頻輝光放電反應,采用高頻輝光放電反應,使反應氣體激活成活性粒子,如原子或各種游離基,這些活性粒子擴散到硅片邊緣,在那里與硅進行反應,形成揮發性生成物四氟化硅而被去除。

2023-05-06 15:08:23 2911

2911

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-06-15 17:51:57 1181

1181

:使用特定的化學溶液進行化學反應來去除氧化膜的濕法刻蝕,以及使用氣體或等離子體的干法刻蝕。1、濕法刻蝕使用化學溶液去除氧化膜的濕法刻蝕具有成本低、刻蝕速度快和生產率高

2022-07-12 15:49:25 1454

1454

離子束蝕刻 (Ion beam etch) 是一種物理干法蝕刻工藝。由此,氬離子以約1至3keV的離子束輻射到表面上。由于離子的能量,它們會撞擊表面的材料。晶圓垂直或傾斜入離子束,蝕刻過程是絕對

2023-06-20 09:48:56 3990

3990

Dimension, CD)小型化(2D視角),刻蝕工藝從濕法刻蝕轉為干法刻蝕,因此所需的設備和工藝更加復雜。由于積極采用3D單元堆疊方法,刻蝕工藝的核心性能指數出現波動,從而刻蝕工藝與光刻工藝成為半導體制造的重要工藝流程之一。

2023-06-26 09:20:10 816

816

干法電極工藝再獲國際車企巨頭“力挺”。

2023-06-28 09:55:17 1028

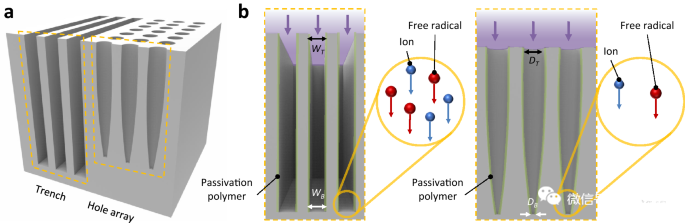

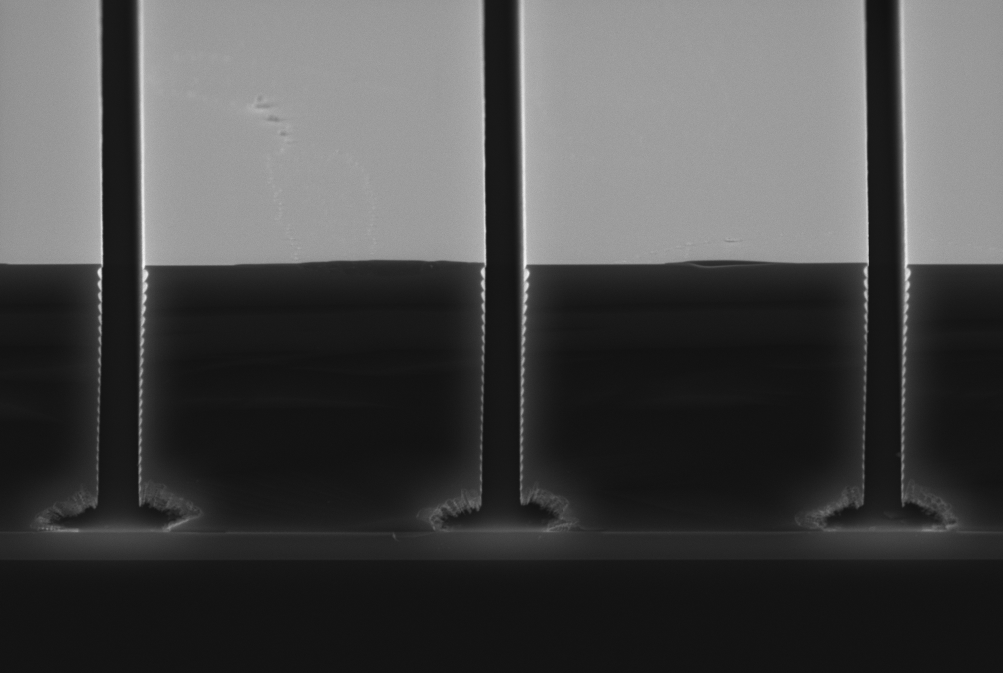

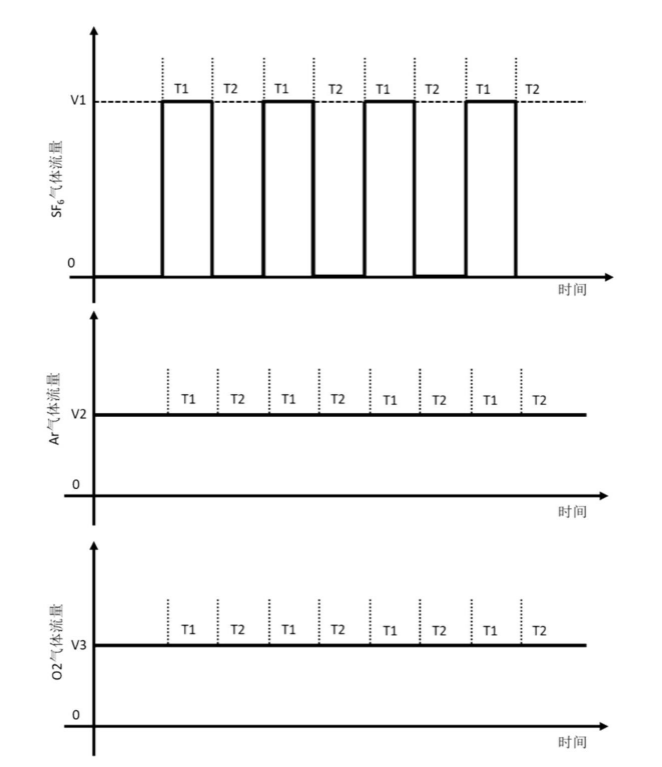

1028 第一種是間歇式刻蝕方法(BOSCH),即多次交替循環刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 3214

3214

雙色紅外探測器具有抗干擾能力強、探測波段范圍廣、目標特征信息豐富等優點,因此被廣泛應用于導彈預警、氣象服務、精確制導、光電對抗和遙感衛星等領域。雙色紅外探測技術可降低虛警率,實現復雜背景下的目標

2023-08-25 09:16:42 886

886

半導體工程裝備、北方華創的主要品種是刻蝕、薄膜、清洗、熱處理、晶體生長等核心技術裝備,廣泛應用邏輯部件,存儲半導體零部件、先進封裝、第三代半導體照明、微機電系統、新型顯示、新能源,襯底材料制造等工藝過程。

2023-09-18 09:47:19 578

578 9月17日,北方華創在投資者互動平臺表示,公司前期已經發布了首臺國產12英寸CCP晶邊干法刻蝕設備研發成功有關信息,目前已在客戶端實現量產,其優秀的工藝均勻性、穩定性贏得客戶高度評價。

2023-09-20 10:09:49 559

559 在半導體制造中,刻蝕工序是必不可少的環節。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術各有優勢,也各有一定的局限性,理解它們之間的差異是至關重要的。

2023-09-26 18:21:00 3307

3307

有過深硅刻蝕的朋友經常會遇到這種情況:在一片晶圓上不同尺寸的孔或槽刻蝕速率是不同的。

2023-10-07 11:29:17 1454

1454

但是,在刻蝕SOI襯底時,通常會發生一種凹槽效應,導致刻蝕的形貌與預想的有很大出入。那么什么是凹槽效應?什么原因引起的?怎么抑制這種異常效應呢?

2023-10-20 11:04:21 461

461

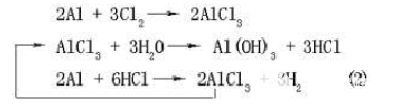

在芯片制程中,很多金屬都能用等離子的方法進行刻蝕,例如金屬Al,W等。但是唯獨沒有聽說過干法刻銅工藝,聽的最多的銅互連工藝要數雙大馬士革工藝,為什么?

2023-11-14 18:25:33 2644

2644

據工信部網站11月16日消息,工信部公開征集了《半導體設備 集成電路制造用干法刻蝕設備測試方法》等196個行業標準、1個行業標準外文版、38個推薦性國家標準計劃項目的意見。

2023-11-16 17:04:49 652

652

半導體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創建所需圖形

2023-11-27 16:54:26 256

256

通過CFD流場模擬技術對溫度流場和混合流場進行優化,提升脫硫效率,對改進的SDS干法脫硫工藝設計起到了指導作用。

2023-12-01 14:51:55 347

347

W刻蝕工藝中使用SF6作為主刻步氣體,并通過加入N2以增加對光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負載效應,避免產生凹坑,并使用對TiN有高選擇比的化學氣體進行刻蝕。

2023-12-06 09:38:53 1538

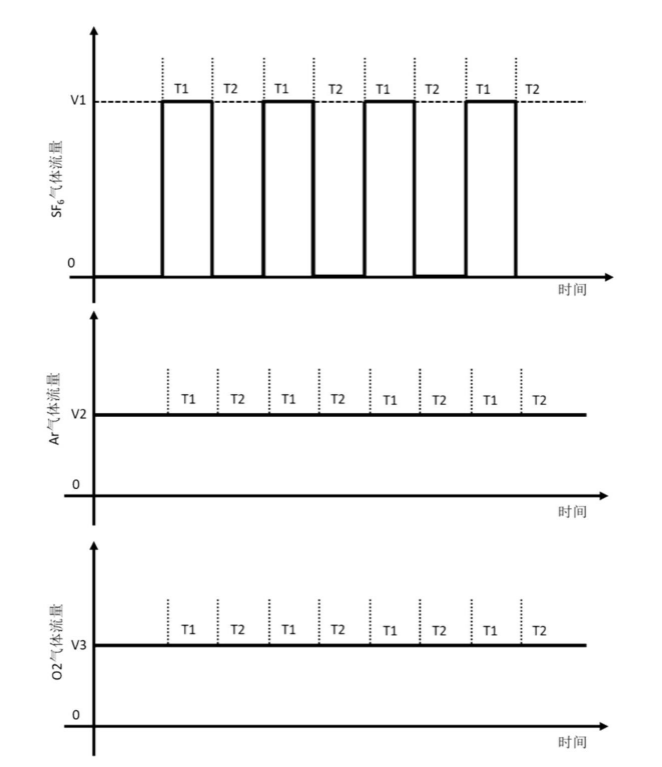

1538 該專利詳細闡述了一種針對含硅有機介電層的高效刻蝕方法及相應的半導體工藝設備。它主要涉及到通過交替運用至少兩個刻蝕步驟來刻蝕含硅有機介電層。這兩個步驟分別為第一刻蝕步驟和第二刻蝕步驟。

2023-12-06 11:58:16 370

370

在芯片制程中,幾乎所有的干法制程,如PVD,CVD,干法刻蝕等,都逃不過輝光放電現象。

2023-12-09 10:00:54 751

751

GaN和相關合金由于其優異的特性以及大的帶隙、高的擊穿電場和高的電子飽和速度而成為有吸引力的材料之一,與優化工藝過程相關的成熟材料是有源/無源射頻光電子器件近期發展的關鍵問題。專用于三元結構的干法蝕刻工藝特別重要,因為這種器件通常包括異質結構。因此,GaN基光電器件的制造部分或全部依賴于干法刻蝕。

2023-12-11 15:04:20 188

188

電子發燒友App

電子發燒友App

評論