MEMS晶圓級(jí)測(cè)試系統(tǒng)

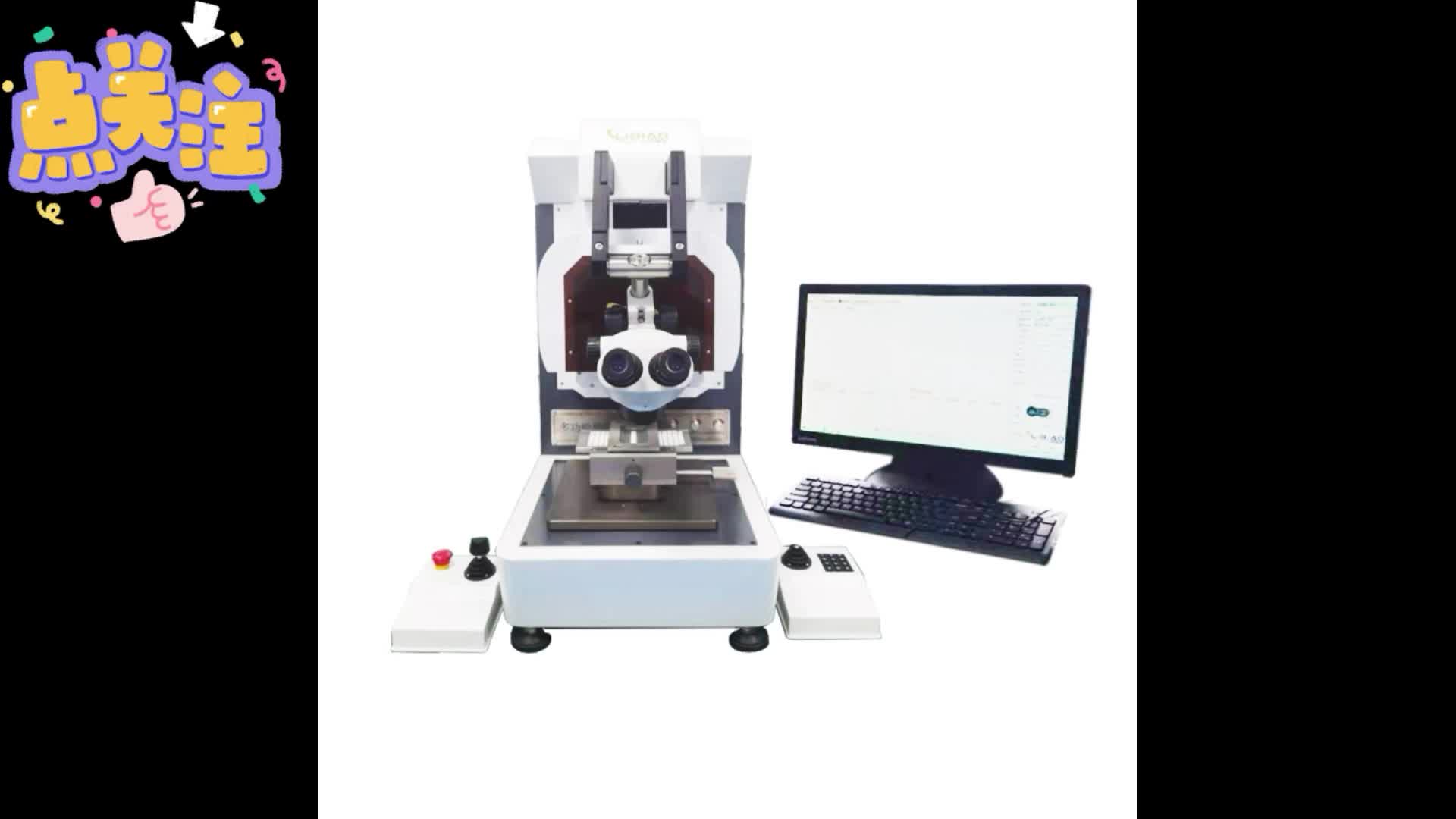

國(guó)外MEMS發(fā)展非常重視基礎(chǔ)技術(shù)尤其是測(cè)試技術(shù)的建設(shè),建立了相應(yīng)的實(shí)驗(yàn)室,如美國(guó)的MCNC、SANDIA國(guó)家實(shí)驗(yàn)室、德國(guó)的BOSCH實(shí)驗(yàn)室等。此外,成立于2003年的MEMUNITY是微系統(tǒng)測(cè)試技術(shù)領(lǐng)域的國(guó)際性組織,主要研究微機(jī)械產(chǎn)品的計(jì)量與測(cè)試。通過(guò)研究晶圓級(jí)測(cè)試技術(shù)所用的裝置,降低MEMS產(chǎn)品生產(chǎn)成本,推動(dòng)微電子機(jī)械系統(tǒng)的商業(yè)化。該組織主要目標(biāo)是了解下一代微機(jī)電系統(tǒng)機(jī)械和電性能的測(cè)量技術(shù)最新進(jìn)展,討論晶圓級(jí)測(cè)試策略和標(biāo)準(zhǔn)化問(wèn)題。晶圓級(jí)測(cè)試技術(shù)領(lǐng)域取得了多項(xiàng)研究成果。最近,MEMUNITY完成了協(xié)同PAR-TEST項(xiàng)目的工作,項(xiàng)目的成果是開(kāi)發(fā)出了一種集成式晶圓級(jí)MEMS器件測(cè)試系統(tǒng)。該測(cè)試系統(tǒng)是一種半自動(dòng)探測(cè)系統(tǒng)(SUSS PA200),具有精確、自動(dòng)的定位和圓片繪圖功能,通過(guò)一個(gè)靜電探針卡驅(qū)動(dòng)膜片,利用一個(gè)激光多普勒計(jì)測(cè)量面外運(yùn)動(dòng)。通過(guò)測(cè)量本征頻率可以提取特征參數(shù),所得到的數(shù)據(jù)結(jié)果用于優(yōu)化器件設(shè)計(jì)和制造工藝,以及確定好壞的管芯測(cè)試。

2. 國(guó)內(nèi)現(xiàn)狀

我國(guó)MEMS晶圓級(jí)測(cè)試技術(shù)研究始于20世紀(jì)90年代初,經(jīng)過(guò)20年的發(fā)展,初步形成了幾個(gè)研究力量比較集中的地區(qū),如京津、華東、東北、西南、西北地區(qū)等。由于MEMS晶圓級(jí)測(cè)試的對(duì)象為立體微結(jié)構(gòu),其測(cè)試技術(shù)與傳統(tǒng)IC晶圓測(cè)試相比有很大不同,難點(diǎn)主要體現(xiàn)在3個(gè)方面:待測(cè)芯片為純機(jī)械結(jié)構(gòu),無(wú)任何電路元件;芯片的信號(hào)非常微弱,如電容量?jī)H為aF級(jí),提取困難,抗干擾能力差;測(cè)試項(xiàng)目除了靜態(tài)測(cè)試之外,還需要大量動(dòng)態(tài)指標(biāo)測(cè)試,如諧振頻率、阻尼系數(shù)、帶寬等。前文中提及國(guó)內(nèi)航天新銳的測(cè)試技術(shù)處于國(guó)內(nèi)領(lǐng)先地位,特別是采用低寄生參數(shù)探針、專(zhuān)用微小電容檢測(cè)電路、檢測(cè)電路與探卡集成、屏蔽與隔振、寄生參數(shù)補(bǔ)償五種技術(shù)減小寄生參數(shù)對(duì)待測(cè)電容的影響,實(shí)現(xiàn)微小電容檢測(cè)。

MEMS測(cè)試系統(tǒng)驗(yàn)證

目前,國(guó)內(nèi)MEMS晶圓級(jí)測(cè)試系統(tǒng)主要開(kāi)展的是晶圓片電參數(shù)的測(cè)量,而國(guó)際上針對(duì)此部門(mén)的研究已經(jīng)趨于成熟,國(guó)際上針對(duì)芯片和產(chǎn)品的力學(xué)參數(shù)開(kāi)展了大量研究,下面逐一闡述。

1. 國(guó)際驗(yàn)證方案

國(guó)際上采用美國(guó)國(guó)家標(biāo)準(zhǔn)技術(shù)研究院的Janet Cassard提出的提供了一種五合一的標(biāo)準(zhǔn)物質(zhì)(reference material, RM)解決MEMS晶圓級(jí)測(cè)試系統(tǒng)的驗(yàn)證。這種標(biāo)準(zhǔn)物質(zhì)是一種獨(dú)立具有測(cè)試結(jié)構(gòu)的芯片,這種測(cè)試結(jié)構(gòu)是通過(guò)五種標(biāo)準(zhǔn)的測(cè)試方法獲取材料和空間特性的。客戶(hù)可以通過(guò)將標(biāo)準(zhǔn)物質(zhì)在本機(jī)構(gòu)測(cè)試系統(tǒng)中的測(cè)試數(shù)據(jù)與此標(biāo)準(zhǔn)物質(zhì)在NIST(國(guó)家標(biāo)準(zhǔn)技術(shù)研究院)的同一測(cè)試系統(tǒng)中所得數(shù)據(jù)進(jìn)行比對(duì)來(lái)進(jìn)行溯源。此外,五合一MEMS還可以應(yīng)用于過(guò)程測(cè)量及驗(yàn)證、客戶(hù)系統(tǒng)本地測(cè)量、實(shí)驗(yàn)室比對(duì)、糾紛及仲裁、儀器的校準(zhǔn)等方面。

MEMS五合一芯片是用以測(cè)量空間和材料特性的NIST標(biāo)準(zhǔn)物質(zhì),分為RM8096和RM8097。RM8096是用1.5μm的化合物半導(dǎo)體(CMOS)工藝線和顯微機(jī)械加工刻蝕制成的。據(jù)報(bào)道此標(biāo)準(zhǔn)物質(zhì)的每一層均為化合物氧化層。RM8097是由多層表面顯微機(jī)械加工MEMS多晶硅的背面刻蝕技術(shù)制成,其中第一、第二層的多晶硅材料特性是公開(kāi)報(bào)道的。

“五種標(biāo)準(zhǔn)測(cè)試方法”用于MEMS五合一芯片的特性測(cè)試,分別為:楊氏模量、臺(tái)階高度、殘余應(yīng)變、應(yīng)變梯度以及平面長(zhǎng)度。其中,楊氏模量和臺(tái)階高度的測(cè)試方法已經(jīng)在“國(guó)際半導(dǎo)體儀器和材料(SEMI)”被報(bào)道,而殘余應(yīng)變、應(yīng)變梯度、平面長(zhǎng)度三者的測(cè)量方法由“美國(guó)國(guó)際測(cè)量&材料聯(lián)合社(ASTM)”公開(kāi)報(bào)道,上述每種測(cè)量方法均有一系列的準(zhǔn)確度和修正數(shù)據(jù)。

“8個(gè)技術(shù)特性”是標(biāo)準(zhǔn)物質(zhì)證書(shū)中具有代表性的典型參數(shù),即前文敘述中提到的五種加上以下三種:殘余應(yīng)力、應(yīng)力梯度、橫梁厚度。殘余應(yīng)力和應(yīng)力梯度是通過(guò)楊氏模量測(cè)試方法計(jì)算得到的;橫梁厚度特性是利用RM8096通過(guò)基于電物理技術(shù)、加上RM8097通過(guò)光機(jī)械技術(shù),應(yīng)用臺(tái)階高度測(cè)量方法獲得的(在NIST特刊SP260—177中提及)。因此,五種測(cè)試方法可以用于獲得8個(gè)技術(shù)特性參數(shù)。

正如列舉的各個(gè)測(cè)試方法所涉及的,楊氏模量的測(cè)試方法使用的是光學(xué)振動(dòng)計(jì)、頻閃觀測(cè)儀的激光干涉儀或同類(lèi)儀器。其它四種測(cè)量方法使用的是光學(xué)激光干涉儀和針式表面光度計(jì)或同類(lèi)儀器。MEMS計(jì)算器可對(duì)MEMS特性參量進(jìn)行數(shù)據(jù)分析。在每一個(gè)數(shù)據(jù)分析表單的最下方有檢定區(qū)。如果所有的相關(guān)單元均顯示“OK”,則數(shù)據(jù)驗(yàn)證通過(guò);否則,特定區(qū)域會(huì)提示“修正數(shù)據(jù)并重新計(jì)算”。

每一個(gè)“五合一芯片”均附帶標(biāo)準(zhǔn)物質(zhì)證書(shū)一份,包括相應(yīng)數(shù)據(jù)分析表單、五種測(cè)量方法和NISTSP260-177。附帶的相應(yīng)數(shù)據(jù)分析表單給出了對(duì)應(yīng)測(cè)量方法的特殊測(cè)試結(jié)構(gòu),同時(shí)包括用于在NIST獲取標(biāo)準(zhǔn)物質(zhì)證書(shū)中測(cè)量結(jié)果的原始數(shù)據(jù)。SP260是一本全面的MEMS五合一用戶(hù)使用手冊(cè);它列出了基于NIST相同測(cè)量結(jié)構(gòu)的同一SEMI或ASTM標(biāo)準(zhǔn)測(cè)量方法;同時(shí),推薦一種可與NIST標(biāo)準(zhǔn)物質(zhì)證書(shū)相比較的測(cè)量方法,以驗(yàn)證用戶(hù)文件標(biāo)準(zhǔn)測(cè)量方法的正確性。

2. 國(guó)內(nèi)驗(yàn)證手段

我國(guó)目前已經(jīng)購(gòu)置或組建多臺(tái)MEMS晶圓級(jí)測(cè)試系統(tǒng),驗(yàn)證手段尚處于空白階段。由于國(guó)內(nèi)尚無(wú)針對(duì)此類(lèi)專(zhuān)用測(cè)試設(shè)備的標(biāo)準(zhǔn)物質(zhì)和標(biāo)準(zhǔn)樣片,因此,測(cè)試系統(tǒng)的準(zhǔn)確度和一致性驗(yàn)證問(wèn)題尚未解決,仍停留在“單臺(tái)儀器拆分計(jì)量”的層面,未開(kāi)展系統(tǒng)的整體校準(zhǔn)工作,各系統(tǒng)參數(shù)無(wú)法溯源到探針端面,難以保證MEMS產(chǎn)品參數(shù)的準(zhǔn)確和一致性,為產(chǎn)品質(zhì)量埋下隱患。

存在的差距

無(wú)論從硬件組成還是從測(cè)試技術(shù)和驗(yàn)證手段比較,目前我們與國(guó)際還有一定的差距,主要體現(xiàn)在3個(gè)方面:

1)缺乏標(biāo)準(zhǔn)化測(cè)試硬件系統(tǒng)。盡管早期測(cè)試有諸多好處,但對(duì)大部分制造商來(lái)說(shuō)很難找到標(biāo)準(zhǔn)化、獨(dú)立運(yùn)行的測(cè)試系統(tǒng),且尚無(wú)同一的測(cè)試標(biāo)準(zhǔn)可依循。MEMS測(cè)試必須通過(guò)添加適當(dāng)?shù)哪K進(jìn)行非電激勵(lì)輸入測(cè)量和非電信號(hào)輸出檢測(cè),晶圓探針可以被擴(kuò)展成一個(gè)開(kāi)放的、通用的測(cè)試平臺(tái),根據(jù)測(cè)試需要可以方便地調(diào)整。整個(gè)開(kāi)放平臺(tái)可以用于測(cè)試不同的產(chǎn)品如:壓力傳感器、微麥克風(fēng)和微鏡等。

2)測(cè)試技術(shù)有待提高。在激勵(lì)信號(hào)方面,除了電激勵(lì)和電測(cè)試之外,器件可能還需要進(jìn)行聲學(xué)、發(fā)光、振動(dòng)、流體、壓力、溫度、化學(xué)或動(dòng)力激勵(lì)輸入;在測(cè)試平臺(tái)方面,器件可能需要開(kāi)放的平臺(tái)且在受控的環(huán)境中測(cè)試才能保護(hù)器件不受環(huán)境的損傷或正確地在封裝的環(huán)境內(nèi)激勵(lì)器件。MEMS器件的晶圓級(jí)測(cè)試可以在測(cè)試所需的真空中或在特殊的氣體環(huán)境中操作,需要精確可控的測(cè)試環(huán)境。

3)系統(tǒng)驗(yàn)證手段空白。目前國(guó)內(nèi)的測(cè)試系統(tǒng)鑒于晶圓級(jí)測(cè)試的微觀性和用于探針末端的標(biāo)準(zhǔn)樣片的缺乏,無(wú)法從準(zhǔn)確度方面對(duì)其進(jìn)行量值傳遞,從而難以保證其溯源性,無(wú)法發(fā)揮晶圓級(jí)測(cè)試的優(yōu)越性,難以保障剔除芯片的合理性和準(zhǔn)確性。

結(jié)束語(yǔ)

自20世紀(jì)60年代微機(jī)械技術(shù)誕生以來(lái),MEMS晶圓測(cè)試技術(shù)隨著MEMS產(chǎn)品的發(fā)展而逐漸成熟,隨著制造器件實(shí)用化、高可靠性、成本低廉的要求,測(cè)試系統(tǒng)出現(xiàn)了如下發(fā)展趨勢(shì):未來(lái)MEMS晶圓級(jí)測(cè)試系統(tǒng)向著標(biāo)準(zhǔn)化、模塊化的開(kāi)放式平臺(tái)發(fā)展;在參數(shù)級(jí)計(jì)量測(cè)試方面,急需利用MEMS或IC技術(shù)研制高穩(wěn)定性標(biāo)準(zhǔn)樣片,是行之有效的校準(zhǔn)方案;在產(chǎn)品級(jí)測(cè)試方面,參照NIST的MEMS五合一測(cè)試芯片,急需通過(guò)對(duì)MEMS芯片添加外圍電路形成模塊化的標(biāo)準(zhǔn)測(cè)試平臺(tái)的手段,解決非電信號(hào)激勵(lì)下的測(cè)試難題,研制符合相應(yīng)激勵(lì)信號(hào)測(cè)試的標(biāo)準(zhǔn)物質(zhì),與國(guó)際NIST標(biāo)準(zhǔn)接軌,進(jìn)一步趕超國(guó)際水平,提升我國(guó)MEMS晶圓級(jí)測(cè)試的整體水平。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論