介紹了一種標準芯片單元可連通性的檢測方法,可以有效檢測標準芯片單元的可連通性,在布局布線階段之前,改進標準單元的版圖,或者增加布局布線的約束條件,從而保證標準芯片單元的設(shè)計對布局布線的友好性。通過對標準芯片單元的檢測和改進,可以有效提高芯片的整體可連通性,從而節(jié)約布局布線階段的工作時間,減少開發(fā)周期,提高芯片良率。本方法可以實現(xiàn)標準芯片單元庫的全覆蓋檢測,通過優(yōu)化算法,可以在盡可能減少芯片測試工作量的前提下,實現(xiàn)90%以上的隨機場景再現(xiàn)。通過在不同技術(shù)節(jié)點標準芯片單元檢測中的應用,有效地捕獲了標準芯片單元連通性的問題,在數(shù)字后端布局布線之前,改進或阻止了可能出現(xiàn)的不友好場景,提升了芯片后端設(shè)計的效率。

在市場需求的驅(qū)動下,近40年來,芯片的設(shè)計和制造技術(shù)得到了突飛猛進的發(fā)展。從45nm到28nm,從16nm到10nm,芯片制造技術(shù)一路高歌猛進,每隔一到兩年時間,芯片的設(shè)計和制造技術(shù)就會被推進到下一個技術(shù)節(jié)點。在人們津津樂道享受著芯片性能提升帶來便利的同時,芯片的設(shè)計和制造正在面臨著巨大的挑戰(zhàn)。

基于物理學定律,工程師通過縮小芯片尺寸來提升其性能。作為一個實際問題,把芯片變得越來越小是非常困難的。現(xiàn)在芯片設(shè)計已經(jīng)將芯片各個組成部分之間的空間縮小到了十幾納米,但邏輯芯片的管腳數(shù)量不會因為芯片尺寸的縮小而減少,如何把百萬數(shù)量級的管腳按照邏輯關(guān)系連接好,是不得不面對的技術(shù)問題。隨著制造工藝越來越復雜,設(shè)計規(guī)則也越來越復雜。工藝每推進一個技術(shù)節(jié)點,后端布局布線的設(shè)計規(guī)則都會有兩到三倍增加,這給芯片設(shè)計和制造帶來很大的挑戰(zhàn)。標準芯片單元作為最小的邏輯單元,在整個芯片上會被大量重復使用,所以標準芯片單元的設(shè)計顯得尤為重要。如果標準芯片單元的可連通性出現(xiàn)問題,將會導致布局布線無法滿足設(shè)計規(guī)則要求,甚至造成芯片斷路失效。本文介紹一種標準芯片單元可連通性的檢測方法,可以實現(xiàn)標準芯片單元庫的全覆蓋檢測,并模擬實際布局布線中的隨機場景來預測可能出現(xiàn)的問題,在實際應用中,取得了很好的效果。

1影響標準芯片單元連通性的主要因素

標準芯片單元的管腳形狀和排列布局會影響芯片的可連通性。在標準芯片單元庫中,與門是一種使用最頻繁的標準單元。圖1(a)是與門的邏輯電路圖,有兩個輸入管腳和一個輸出管腳。在標準芯片單元的版圖上,對應的也有兩塊金屬用于輸入端的連接,一塊金屬用于輸出端的連接,如圖1(b)。

在進行版圖設(shè)計時,版圖工程師會對版圖本身的設(shè)計規(guī)則進行檢查,同時預留管腳的外連空間。管腳的外連方法一般有兩種,一種是在管腳上打過孔,然后再用金屬層接出;另一種方法是把管腳做金屬層延伸,然后在通過跳層方法接出。不管采用哪種方法把管腳引出,在進行標準芯片單元版圖設(shè)計時,這些引出的金屬層都是不存在的,版圖工程師只能預估可能的接線方法來預留空間。

影響管腳接線的設(shè)計規(guī)則主要有:金屬線與金屬線之間的距離、金屬端頭之間的距離、過孔被金屬層覆蓋的面積、跨層金屬之間的距離等。圖2(a)~圖2(c)是一些常見的設(shè)計規(guī)則。

設(shè)計規(guī)則比較復雜,有些場景需要考慮多個金屬之間的相互影響。如果版圖工程師沒有能充分考慮到這些可能存在的場景,或者對設(shè)計規(guī)則的理解不充分,就有可能在實際連線中出現(xiàn)管腳不能被引出,或者管腳能夠被引出,但引線違反了設(shè)計規(guī)則。

在實際應用中,標準芯片單元有可能是緊挨著放在一起,這時候兩個單元的管腳就會相互影響。版圖工程師很能考慮這種情形,因為很難預測到哪些標準芯片單元會被放在一起。圖3是兩個標準芯片單元放在一起的場景。兩個輸入端管腳離得很近,而且都需要引出,引出線之間很容易觸發(fā)設(shè)計規(guī)則,如果預留的空間不足,就有可能造成管腳無法引出的情況。

2 標準芯片單元連通性檢測的思路

標準芯片單元是孤立的元器件,為了檢測芯片管腳的可連通性,需要把標準芯片單元連接一起,通過實際布局布線來檢測管腳設(shè)計的合理性。在標準單元設(shè)計初期,標準芯片單元的功能可能還沒有完善,數(shù)量也不足以組成一個真正的邏輯芯片[10]。同時做一個真正的邏輯網(wǎng)表和完成完整的數(shù)字后端,需要的時間也比較長,版圖工程師可能沒有經(jīng)驗和時間來做這種測試。如果能夠簡單地把這些標準芯片單元連接起來,并做快速的布局布線,將會幫助工程師快速地檢測芯片管腳的連通性。

基于以上需求,本文用腳本產(chǎn)生一個網(wǎng)表,然后使用innovus的布局布線工具來模擬標準芯片單元的管腳連接情況。圖4是本方法的流程圖。

從標準芯片單元庫中任選兩個驅(qū)動單元和接收單元,用驅(qū)動單元來連接單元庫的標準單元,所有標準單元的管腳連接到接受單元。使用這種方法來產(chǎn)生隨機網(wǎng)表,其目的是遍歷標準單元庫的所有標準單元,保證每個標準單元的管腳都被連接。

使用這個隨機網(wǎng)表,在innovus平臺進行布局,通常布局的密度從小到大。先使用較小的布局密度,這時標準單元放在一起的幾率不大,可以檢查標準單元本身的連通性。然后逐步增加布局密度,這時標準單元放在一起的幾率增大,可以檢查標準單元之間的相互影響。

在布線階段,通過參數(shù)設(shè)置,來限制管腳連接的方向和位置,可以實現(xiàn)特定目的的測試。也可以通過設(shè)置參數(shù)來模擬實際芯片設(shè)計時的場景,比如,增大連接線的寬度,增加過孔的數(shù)量,添加靜電隔離線,等等,從而盡可能再現(xiàn)實際應用場景。

如果標準芯片單元的管腳連通性出現(xiàn)問題,innovus會在管腳處留下違規(guī)標記。我們可以根據(jù)違規(guī)標記找到對應的設(shè)計規(guī)則,對管腳的形狀進行分析,研究如何改進管腳的形狀來避免管腳引線觸發(fā)設(shè)計規(guī)則。如果芯片單元的管腳受空間限制,不能夠進行更改,則研究是否可能通過增加布局布線的約束條件來避免出現(xiàn)這些場景。

3 隨機網(wǎng)表的產(chǎn)生

隨機網(wǎng)表使用verilog語言描述,下面是一段連接關(guān)系的例子。

supply0 VSS;

supply1 VDD;

NR 01 (.A1(41),.A2(VSS),.ZN(01),.A3(86) );

AD 02 (.S(02),.A(47),.CO(03),.B(44) );

QD 03 (.CP(50),.Q(04),.D(71),.DN(VDD) );

ND 04 (.DN(83),.CP(clk),.Q(05),.D(38),.SDN(58) );

RD 05 (.A1(72),.A2(56),.A4(12),.ZN(06),.A3(56) );

用驅(qū)動單元的驅(qū)動端作為起點, 遍歷標準芯片單元庫里的標準單元,連接到驅(qū)動單元的驅(qū)動管腳上。當驅(qū)動單元驅(qū)動能力達到上限時,停止遍歷標準單元庫,把被驅(qū)動單元的管腳連接到接收單元上。再使用驅(qū)動單元作為新的起點,重復上面的步驟,生成新的連接關(guān)系。由于管腳之間的連接關(guān)系是隨機選取的,遍歷單元庫的次數(shù)越多,標準芯片單元被兩兩互聯(lián)的幾率越大。

在隨機網(wǎng)表中,驅(qū)動單元驅(qū)動多個標準芯片單元,這些連接沒有實際意義的邏輯關(guān)系,只是為了把芯片的管腳連接在一起。圖5是一個驅(qū)動單元驅(qū)動多個標準單元的例子。在布局后,這些標準芯片單元分布在芯片的各個角落,在布線后,被實體金屬線連接在一起。

4 重點芯片單元的選取

如果標準芯片單元的管腳設(shè)計對布局布線不友好,布線工具會把管腳連接上,同時留下違規(guī)標記;或者讓管腳懸空,同時留下管腳懸空標記。在布局布線后,通過布線工具留下的違規(guī)標記,可以找到有問題的標準芯片單元。

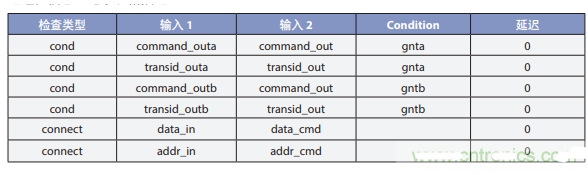

有些管腳的連接性問題是受它的周邊環(huán)境的影響,也就是說,這些管腳隨著它的周邊環(huán)境變化,有的時候出現(xiàn)連通性問題,有的時候又可以正常引出。innovus平臺提供了一個功能來統(tǒng)計標準芯片單元在芯片中出現(xiàn)的次數(shù)和出現(xiàn)連通性問題的頻率。表1是一個innovus報告的例子,報告中列舉了設(shè)計規(guī)則違規(guī)的標準單元的出現(xiàn)次數(shù)和違規(guī)頻率。違規(guī)頻率越高,表明這個標準單元越容易出錯。

由于標準芯片的組合非常多,窮舉所有的組合進行測試顯示不大現(xiàn)實。假如一個標準芯片單元庫有300個標準單元,每個標準單元在布局有4種翻轉(zhuǎn)狀態(tài),也就是有1 200種芯片單元放置狀態(tài)。考慮兩個標準單元兩兩相鄰的情況,這些場景就有![]() 超過100萬,而實際上每個標準單元周邊可以擺放8個標準單元, 那么就是

超過100萬,而實際上每個標準單元周邊可以擺放8個標準單元, 那么就是![]() 所以需要選取重點的標準芯片單元來進行測試。

所以需要選取重點的標準芯片單元來進行測試。

在選取重點標準芯片單元時,設(shè)計規(guī)則和設(shè)計規(guī)則違規(guī)頻率是兩個重要的考慮因素。我們賦予設(shè)計規(guī)則類型不同的權(quán)重,如表2所示。

根據(jù)設(shè)計規(guī)則違規(guī)出現(xiàn)的頻率,來進行權(quán)重的修正。

根據(jù)重點芯片的權(quán)重,我們把權(quán)重大于0.1的標準芯片單元選取出來,生出更多的隨機網(wǎng)表來增加布局布線的場景覆蓋率。對于權(quán)重大于0.5的標準芯片單元,我們會生成特定的場景來檢測芯片單元放在一起時的連通性。

5 重點芯片連通性的檢測方法

對于重點芯片,我們通過遍歷芯片的擺放位置, 來檢測芯片周邊環(huán)境的影響。圖6所示,標準芯片單元繞Y軸翻轉(zhuǎn),有兩個擺放狀態(tài)。如果兩兩相鄰的話,共有4種組合。

本方法遍歷所有的重點芯片單元,每種組合生成一個網(wǎng)表。在布局時,標準芯片單元兩兩相鄰。布線后檢查芯片管腳的連通性,如果Innovus檢查出有設(shè)計規(guī)則違規(guī),則輸出設(shè)計規(guī)則違規(guī)報告文件,自動保存布線后的數(shù)據(jù)以備進一步分析使用。

6 芯片聯(lián)通性問題的處理

連通性問題通常是由不合理的管腳形狀引起。如圖7(a)所示,在使用過孔連接中間位置的管腳時,過孔會觸發(fā)過孔和相鄰金屬之間的設(shè)計規(guī)則。在使用金屬線連接中間位置的管腳時,如圖7(b)所示,則會觸發(fā)金屬線和金屬線之間的設(shè)計規(guī)則。

對上面這個管腳設(shè)計,有兩種改進方案,一種是把中間的這個管腳往下移動,或者增大管腳面積,這樣在用過孔連接管腳的時候,可以把過孔向下方挪動一些,以避免觸發(fā)過孔和金屬線之間的設(shè)計規(guī)則,如圖8(a)所示。或者如圖8(b)所示,把相鄰的管腳剪除一些,這個管腳往下引線的時候,可以避開金屬線端頭和金屬線之間的設(shè)計規(guī)則,同時這條引線可以和相鄰的金屬線保持一點距離,允許使用過孔往高層跳線。

如果管腳的連通性問題是由于兩個標準單元擺放在一起引起的,同時受限于版圖空間的限制,管腳的形狀無法改變。這時我們采用增加布局布線約束的方法來阻止這種場景出現(xiàn)。如圖9(a)所示,兩個標準芯片單元相鄰放在一起,中間兩個短的管腳無法被連接。通過增加布局布線的約束,在標準單元的邊界上增加約束條件,在布局的時候,不允許這兩個標準單元的邊界放在一起,從而留出大的空間來連接這兩個短的管腳。

7 本方法的優(yōu)缺點和可能改進的方面

本方法可以快速地生成隨機網(wǎng)表,在標準芯片單元開發(fā)的早期階段,使用innovus平臺對標準單元的連通性進行檢測分析。本方法的優(yōu)點在于簡單易用,標準芯片單元的連通性問題比較直觀,方便統(tǒng)計分析;缺點在于運算量比較大,無法實現(xiàn)場景全覆蓋測試,隨機網(wǎng)表比較大時,會出現(xiàn)無法布局布線的情況。可能改進的兩個方面:一是在產(chǎn)生隨機網(wǎng)表時,盡可能模擬實際的邏輯電路,避免出現(xiàn)不能布局布線的情形。二是優(yōu)化實驗設(shè)計,在盡可能減少運算量的情況下,增加場景的覆蓋率。

8 結(jié)語

本文介紹了一種標準芯片單元可連通性的檢測方法,可以實現(xiàn)標準芯片單元庫的全覆蓋檢測,通過優(yōu)化算法,可以在減少芯片測試工作量的前提下,實現(xiàn)90%以上的隨機場景再現(xiàn)。在標準芯片單元檢測中的實際應用中,有效地捕獲了標準芯片單元連通性的問題,通過和標準芯片單元庫廠商合作,改進了標準的單元版圖設(shè)計,從而提高的芯片設(shè)計的效率和芯片的制造良率。

電子發(fā)燒友App

電子發(fā)燒友App

評論