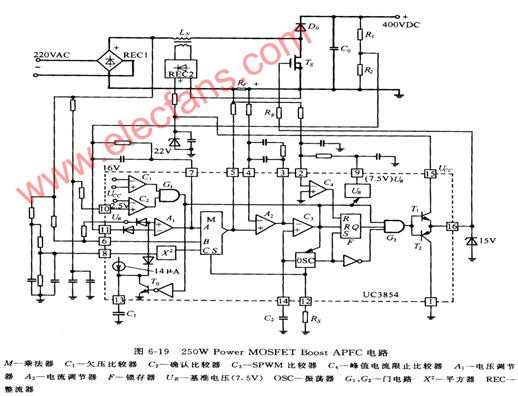

一種用于APFC的改進(jìn)型ZVT-BOOST電路

摘要:介紹一種改進(jìn)型ZVT-BOOST電路,輔助管增加了無損吸收電路,進(jìn)一步提高了軟開關(guān)

電路的效率。文中分析了電路的工作原理,給出了仿真與實驗結(jié)果以及主要參數(shù)的設(shè)計。

關(guān)鍵詞:軟開關(guān)電路無損吸收效率

An Advanced ZVT- BOOST Circuit for APFC

Abstract: The paper introduces an advanced ZVT- BOOST circuit. In order to enhance the efficiency, an lossless snubber circuit is given for auxilliary switching. The analysis of the circuit theory, PSPICE simulation and experimental result are also given.

Keywords:Soft- switching circuit Lossless snubber Efficiency

1引言

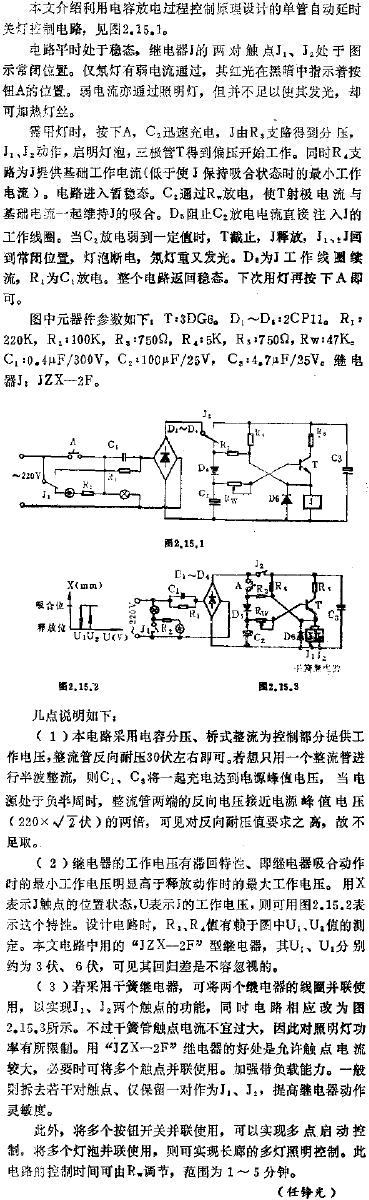

有源功率因數(shù)校正(APFC)技術(shù)能夠?qū)崿F(xiàn)各種電源裝置網(wǎng)側(cè)電流正弦化,把非線性負(fù)載變換成為一個等效純電阻,使功率因數(shù)接近1,極大地減少了電流的高次諧波,消除了無功損耗,減小了電磁干擾(EMI)。目前已進(jìn)入商業(yè)實用階段。由于是在電網(wǎng)和電源裝置之間串聯(lián)插入的功率校正裝置,因此功率因數(shù)校正裝置的可靠性和電效率顯得尤為重要。能夠?qū)崿F(xiàn)功率因數(shù)校正的電路有多種,在功率較大的場合,BOOST電路具有許多優(yōu)點而得到了廣泛的應(yīng)用[1]。但是,單相BOOST型PFC硬開關(guān)變換器工作于電流連續(xù)模式(CCM)時,由于BOOST二極管的反向恢復(fù),功率開關(guān)器件將產(chǎn)生很大的開通損耗(這部分損耗將占PFC電路總損耗的30%)[2]。同時產(chǎn)生很大的干擾。這不僅降低了功率,更為嚴(yán)重的是,由于損耗引起溫升,降低了可靠性。所以在大功率時,硬開關(guān)BOOST電路存在嚴(yán)重的缺陷[1]。零電壓過渡(ZVT)技術(shù)應(yīng)用于BOOST電路很好地解決了二極管反向恢復(fù)問題。但是其輔助管工作于硬關(guān)斷狀態(tài),將產(chǎn)生較大的關(guān)斷損耗。

2改進(jìn)型ZVT-BOOST電路的原理

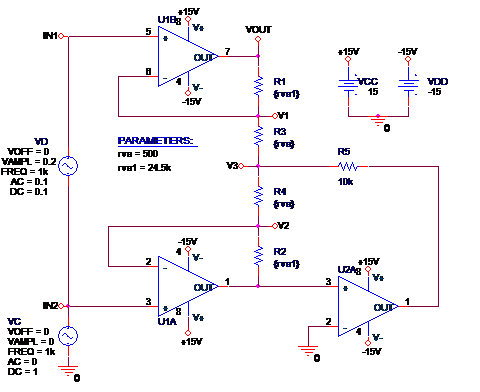

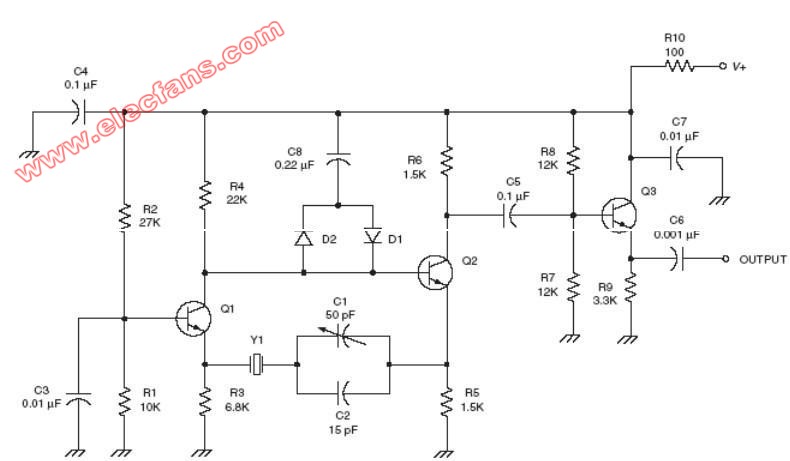

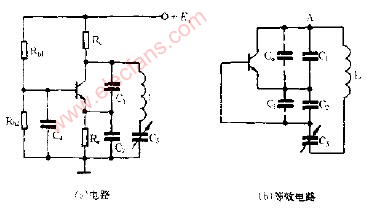

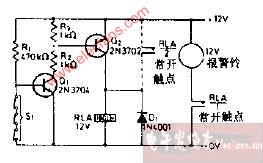

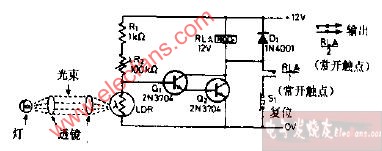

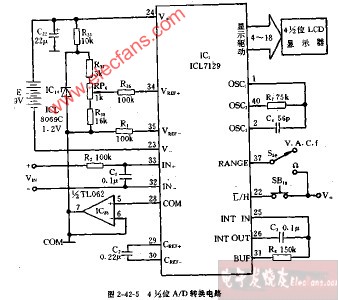

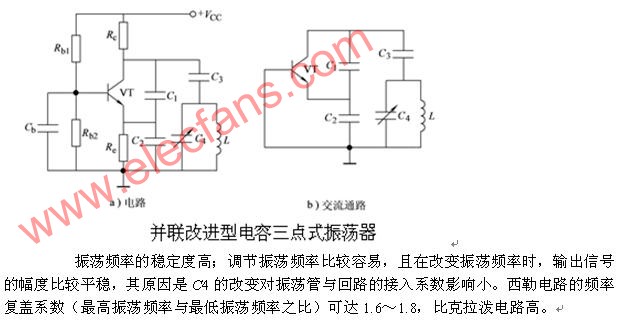

為了減少ZVT-BOOST電路輔助管的關(guān)斷損耗,在輔助管上加入無損吸收電路,實現(xiàn)輔助管的軟關(guān)斷。電路如圖1所示,圖中C1、VD1就是關(guān)斷時的無損耗吸收電路。

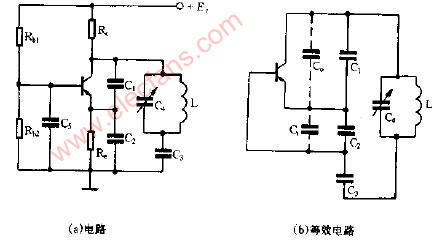

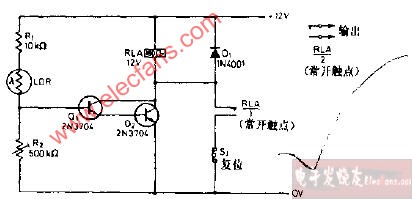

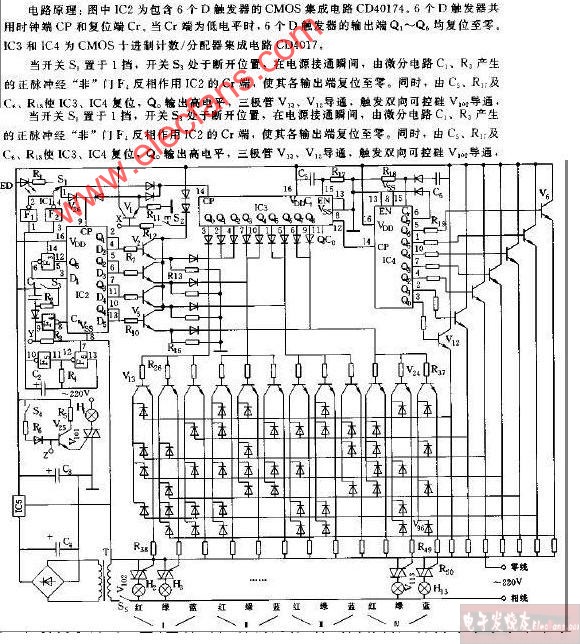

電路的工作有八個階段組成,如圖2所示。

Mode1,t0-t1階段:t0時刻輔管Sr受控開通,流過BOOST二極管VD的電流iD開始向輔管Sr、輔助電感Lr換流。LrdiLr/dt=U0,直至iLr=iL,iD=0。

Mode2,t1-t2階段:BOOST二極管VD電流過零關(guān)斷,諧振電容Cr(包括主管S的內(nèi)部電容)和輔助電感Lr諧振,iLr繼續(xù)上升,Ucr下降。

當(dāng)Uin>Ucr時,BOOST電感L中的電流iL開始上升。

Mode3,t2-t3階段:Ucr下降為零,主管S的內(nèi)部反并聯(lián)二極管導(dǎo)通,主管S的端壓被鉗位于-0.7V。

Mode4,t3-t4階段:在零端壓下主管S受控開通,iL流入S:LdiL/dt=Uin,同時輔管Sr受控關(guān)斷,iLr向吸收電容C1以及輔管Sr內(nèi)部電容Cds諧振充電:LrdiLr/dt=Ucl=UCds,(C1+Cds)dUcl/dt=iLr。

由于增加了吸收電容C1,所以輔管Sr關(guān)斷時電壓上升的速度變慢,實現(xiàn)了關(guān)斷緩沖。

Mode5,t4-t5階段:當(dāng)Ucl=Ucds=UO時,VD2導(dǎo)通,Ucl、Ucds被箝位于UO,Lr通過已開通的主管S向負(fù)載釋放能量,直至iLr=0。

Mode6,t5-t6階段:iLr下降為零,VD1、VD2、VD3因電流過零關(guān)斷,iL通過導(dǎo)通的主管S繼續(xù)上升。

Mode7,t6-t7階段:主管S受控關(guān)斷,iL向Cr充電,Ucr上升;由于Ucl+Ucr=UO,Ucr上升使Ucl下降(也就是iL向C1反向充電,VD2導(dǎo)通)。直至Ucr=UO,Ucl=0,使輔管Sr的緩沖電容C1電壓無損回零,實現(xiàn)

圖1改進(jìn)型ZVT-BOOST電路

(a)Mode1?? (b)Mode2

(c)Mode3??? (d)Mode4

(e)Mode5??? (f)Mode6

(g)Mode7??? (h)Mode8

圖2電路工作的八個階段

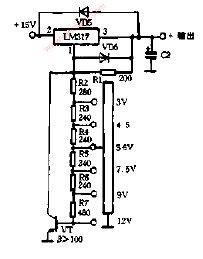

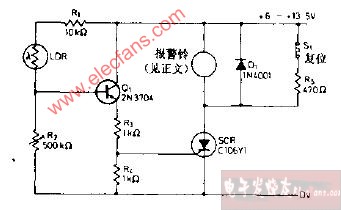

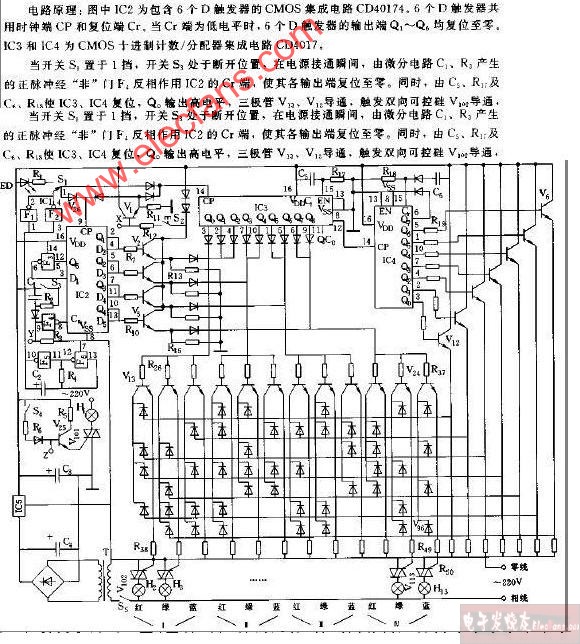

圖3電路工作的原理波形

了無損吸收,可以看出,C1對主管S關(guān)斷也起到了關(guān)斷緩沖的作用。

Mode8,t7-t8階段:BOOST二極管VD開通,并保持Ucr=UO,Ucl=0。

電路進(jìn)入下一周期。圖3給出了電路的主要波形。

可以看出,改進(jìn)型ZVT-BOOST電路的主管在零電壓下開通。關(guān)斷時,并聯(lián)電容減少了關(guān)斷損耗。輔管由于增加了緩沖吸收電容C1,減少了關(guān)斷損耗。而且吸收電路的能量(1/2)C1U2o向負(fù)載釋放,沒有造成損耗。因此,無損吸收進(jìn)一步降低了原來ZVT-BOOST電路的損耗。

3仿真結(jié)果

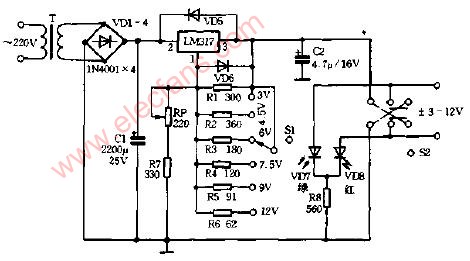

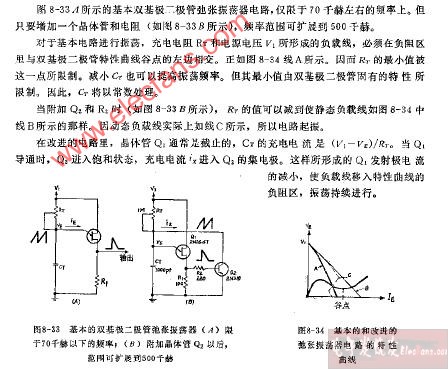

對圖1電路用PSPICE進(jìn)行仿真,選用參數(shù)為:L=600μH,Cr=1000pF,Lr=20μH,C1=1nF,Cds=400pF,Uin=200V(DC),UO=400V,RO=82Ω。圖4給出了仿真結(jié)果。

4主要參數(shù)的設(shè)計

把改進(jìn)型ZVT-BOOST電路運(yùn)用于PFC,設(shè)計指標(biāo):Pin=4.0kW,Uin=220V,Uo=400V,fs=50kHz,PF>0.99,輸入電流脈動<10% 。

(1)BOOST電感L

L的選取應(yīng)滿足輸入電流紋波的要求,根據(jù)SPWM的調(diào)制原理,不難得到[4]。

式中,Uin(pk)為輸入電壓的峰值;△I為最大輸入電流紋波。

(2)輸出濾波電容Co

對輸入、輸出瞬時功率進(jìn)行分析,可以看出輸出電壓Uo包含有兩倍網(wǎng)頻(即100Hz)的紋波,為了使Uo滿足設(shè)計要求(脈動<5% ) ,

(3)諧振參數(shù)Lr、Cr

由前述原理可知,為了保證主管零電壓開通,主管的開通時刻應(yīng)比輔管延時一段時間td,

td≥t2-t1=t10+t21(4)

式中,t10為iL從VD換向Sr所需的時間,

t10=t1-t0=Lr·iLmax/Uo(5)

其中iLmax應(yīng)取最大輸入電流并考慮其紋波。

其中Tr為諧振周期。

改進(jìn)型ZVT-BOOST電路由于給輔管增加了無損吸收電路(緩沖強(qiáng)度可按強(qiáng)型設(shè)計),大大減小(甚至消除)了關(guān)斷損耗,進(jìn)一步減小整個電路的損耗。

圖4PSPICE仿真結(jié)果

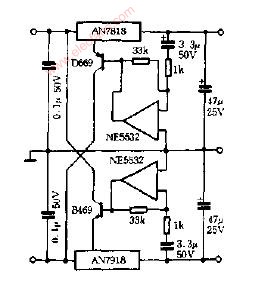

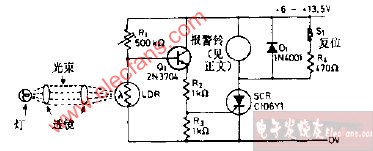

圖5改進(jìn)型ZVT—BOOST電路實驗波形

設(shè)計時,諧振頻率fr一般取開關(guān)頻率fs的5~10倍。過高,則諧振電流峰值太大;過小,則td過長,主電路不能利用的占空比太大,造成輸入電流的畸變和輸出電壓的不穩(wěn)。Cr的選取應(yīng)有利于減少主管的關(guān)斷損耗和不引起過大的諧振峰值電流。由于C1同樣對主管起到了關(guān)斷緩沖吸收的作用,因此Cr的值可取小,甚至不用外接。取Cr=1000pF(包括主管內(nèi)部輸出電容)、Lr=20μH,td=2μs。

(4)吸收電容C1

C1取大有利減小主管和輔管的關(guān)斷損耗,但過大,則會造成L中的能量不足以使UC1恢復(fù)回零,起不到緩沖的作用,實驗中取C1=1nF。

5實驗結(jié)果與結(jié)論

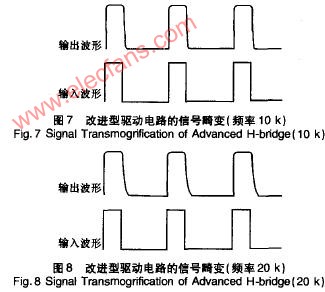

(a)主管驅(qū)動與主管端壓波形??(b)PFC電路輸入端電壓、電流波形

圖5給出了采用改進(jìn)型ZVT-BOOST電路實現(xiàn)PFC的實驗波形。

參考文獻(xiàn)

1 Hengchun Mao, Fred. C. Lee, “ Review of Power Factor Correction Techniques,” IPEMC'97

2 K. Dierberger, “ New U1trafast Recovery Diode Technology Improves Performance of High Frequency Power Circuit” , APT Application Note, APT9301.

3 Guichao Hua, Chingshang Leu et al,“ Novel Zero- voltage transition PWM Converters", IEEE TRANS. Power Electron., 94, 9(2): 213~ 218

4 Philip C.Tood, “ UC3854 Controlled Power Factor Correction Circuit Design” , Unitrode Application Note, U- 134, 95.

電子發(fā)燒友App

電子發(fā)燒友App

評論