摘要:以Altera公司MAX700舊系列為代表,介紹了CPLD在DSP系統中的應用實例。該方案具有一定的普遍適用性

DSP的速度較快,要求譯碼的速度也必須較快。利用小規模邏輯器件譯碼的方式已不能滿足DSP系統的要求。同時,DSP系統中經常需要外部快速部件的配合,這些部件往往是專門的電路,可由可編程器件實現。CPLD的時序嚴格、速度較快、可編程性好,非常適合于實現譯碼和專門電路。本文以MAX7000系列為例,具體介紹其在以TI公司的TMS320C6202為平臺的網絡攝像機系統中的應用。

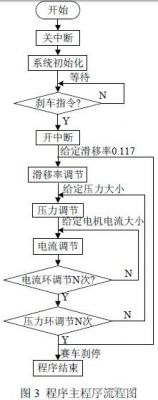

1 CPLD在DSP系統中的功能介紹

1.1 DSP系統簡介

本文所論述的編碼器系統是基于DSP的MPEG-4壓縮編碼器的,主要由前端視頻采集、數據預處理以及MPEG-4視頻壓縮編碼三部分組成。基于DSP的MPEG-4編解碼器由于其所選用的DSP運算能力強、編程靈活,且實現不同的圖像編碼算法時只需對DSP內部的程序進行改寫便可實現諸如MPEG、H.263等多種圖像編碼,因而具有良好的應用情景。CPLD芯片對整個編碼器起著邏輯控制作用,系統結構如圖1所示。

1.2 CPLD在系統中的功能要求

1.2.1 產生復位信號

系統上電時,CPLD產生復位信號,使整個系統中的FPGA和DSP模塊復位,進入初始狀態;系統上電后,數據采集模塊自動啟動。

系統內共使用三種電源:5V、3.3V、1.8V。其中,5V電源由供電電源接人,3.3V、1.8V電源由TPS56300(TI產品)提供。采用TPS3307(TI產品)為系統提供電源管理,該芯片可同時管理三種電源。當監測到電源電壓低于一定值時,產生復位信號。TPS3307在其自身電源電壓大于1V的情況下即可以輸出復位信號。?

當系統出現錯誤時,可以采用手工方式復位。

復位信號產生原理圖如圖2所示。其中,RST#為整個系統的復位信號,由MAX7000輸出。PBSW_RST#為手動復位信號,由按鍵接人MAX7000,經MAX7000去抖動后輸出給TPS3307。SVS_RST#為電源管理芯片TPS3307產生的復位信號(包括手動復位和電源監控功能)。

1.2.2 BOOT模式的實現

系統復位后,DSP需要進行BOOT自舉。在復位信號為低期間,BOOTMODE[4:0]管腳上的設置值被鎖存,決定芯片的存儲器映射方式以及自舉模式。但TMS320C6202沒有專門的管腳作為BOOTMODE[4:0]輸入管腳,而是將擴展總線的XD[4:0]映射為BOOTMODE[4:0],利用上拉/下拉電阻在復位時進行芯片啟動模式設置。總線上的其它位也在復位期間被鎖定,決定系統相應的設定值。而擴展總線XD在HPI口讀寫時要用到,所以使用MAX7000進行隔離。系統處在復位階段,則通過MAX7000使得DSP的相應管腳的值等于設定值,復位結束后,MAX7000相應管腳為高阻態,使得XD可以作為正常的總線使用。

DSP自舉有特定的時間要求。在復位結束后,XD的配置管腳必須保持一段時間,TMS320C6202要求時間為5個時鐘周期,例如在200MHz時鐘情況下必須保持25ns。

1.2.3 HPI口接口邏輯實現

MPEG-4壓縮編碼器壓縮后的數據,通過網絡傳輸控制模塊傳輸到網絡上去,從而實現網絡實時圖像傳輸。而DSP與網絡傳輸模塊(MCF5272)通過HPI口連接。其接口邏輯由CPLD完成。硬件連線圖如圖3所示。

根據系統的邏輯要求以及實際的仿真結果,CPLD選用EPM7128SLC84。該芯片共有2500門,128個宏單元,最多100個用戶自定義管腳。

2 CPLD邏輯控制的具體實現

2.1 復位信號的實現

復位信號邏輯產生較簡單,需要處理的是按鍵的去抖動。由于按鍵是機械觸點,當機械觸點斷開、閉合時會有抖動,為使每一次按鍵只作一次響應,就必須考慮去除抖動。在通過按鍵獲得復位信號為低的信息時,不是立即認定按鍵已被按下,而是延時一段時間后再次檢測復位信號。如果仍為低,說明按鍵的確按下了,這實際上是避開了按鍵按下時的抖動時間。同樣,在檢測到按鍵釋放后,再延時幾個毫秒,消除后沿的抖動,然后再對鍵值處理。由于抖動現象主要出現在按鍵按下后,采用延時方法可有效地減少按鍵的抖動現象。

2.2 BOOT模式的實現

為了滿足在復位有效期間對相應管腳進行配置,在復位無效時,使管腳進入高阻態。以其中一個管腳為例,采用Verilog語言,用如下語句實現該功能:

assign hd0=(tp4)?rst_hd0:1′bz;

//復位有效期間,tp4為1,hd=rst_hdo,即為設定值;復位無效時,tp4=0,hd為高阻態。

圖4

因為DSP自舉有特定的時間要求,在復位信號結束后,配置管腳的值必須至少保持25ns。通過對復位信號作一定的延時,可以滿足要求。采用CPLD將信號作一定的延時,并不能簡單地在信號后串接一些非門或其它門電路,因為開發軟件在綜合設計時會將這些門作為冗余邏輯處理,達不到延時的效果。所以采用高頻時鐘驅動一移位寄存器,對移位寄存器進行正確的設置后,輸出即為延時后的數據。語句如下:

always@(posedge eclkout2) //采用dsp的clkout=100MHz二分頻后作延時

begin

if(svs_rst_) //svs_rst_低電平,count始終置1010

begin

count=4′b1010;

end

else if(count==4′b0000) //0000則保持

begin

count=4′b0000;

end //svs_rst_高電平,count開始計數

else

begin

count=count+4′b0001; //記六次至0000

end

end

assign tp4=count[3];

仿真效果如圖4所示。由仿真波形可見,CPLD的信號輸出完全符合DSP BOOT的兩個要求。

2.3 HPI口接口邏輯的實現

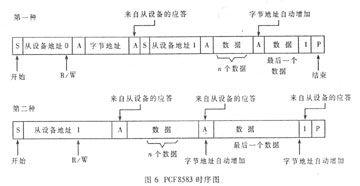

圖像壓縮編碼器通過DSP的HPI口與網絡模塊連接,實現圖像的網絡傳輸。TMS320C6202的HPI口是指其擴展總線的主機口接口部分。經過編碼器編碼后的MPEG-4圖像數據以幀為單位存放在DSP內部存儲器中,外部主機通過HPI口讀取。現以MCF5272微處理器與HPI口通信為例進行說明。

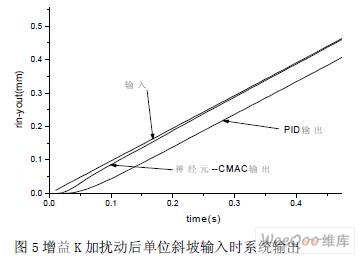

圖5

MCF5272將10/100MB以太網控制器和一個USB模塊等通信外圍設備結合起來,是一款高集成的ColdFire微處理器。詳見參考文獻[4]。

MCF5272與TMS320C6202連接采用異步從屬工作方式,MCF5272作為上行機,TMS320C6202作為從屬機。由MCF5272高位地址線模擬XCNL、XR_W信號,TMS320C6202的多功能串行口3工作在GPIO模式下模擬HINT信號,為MCF5272提供主機口中斷。本系統由CPLD——MAX7000編程實現兩者硬件接口。仿真后的時序如圖5所示,實驗證明可以滿足雙方時序要求,實現數據傳輸。

以上所討論的邏輯并不復雜,采用74系列在一定程度上說也可以完成。但是,采用CPLD具有以下優勢:體系結構和邏輯單元靈活、集成度高、適用范圍廣,因而采用CPLD的方案。? 在開發階段,通過硬件實現的控制信號往往不能確定,需要試驗驗證。而CPLD因其具有靈活性,逐漸成為DSP進行信號處理不可或缺的協處理器。將相關控制信號接人CPLD,只需通過簡單的編程即可實現各種需要的邏輯,避免了硬件上的改動,使硬件邏輯控制更加方便靈活,對類似設計具有普遍意義。文中討論的防抖動以及CPLD延時程序對于類似設計也有一定的借鑒意義。

本文介紹的CPLD在基于DSP的MPEG-4編碼壓縮模塊的系統中的應用實例,已通過下載驗證。應用在工程實踐中,結果表明該設計是方便靈活且正確有效的。

- cpld(168087)

- 應用設計(8445)

相關推薦

基于DSP的CPLD多方案現場可編程配置

961

961

CPLD在汽車制動性能檢測系統中的應用

DSP+CPLD下載程序失敗

DSP在電源設計中的應用

DSP與CPLD協同控制的高速圖像通信系統的設計

DSP與CPLD協同控制的高速圖像通信系統的設計介紹

DSP及FPGA在系統設計中的應用

DSP開發板上CPLD是用來擴展IO口嗎?

dsp+cpld系統,外接看門狗芯片,喂狗信號是誰給的?

【TL6748 DSP申請】基于DSP和CPLD的智能監測系統設計與開發

【下載】《CPLD/FPGA的開發與應用》

基于CPLD的DSP與聲卡的接口技術

基于CPLD的DSP人機接口方案

基于DSP+CPLD的無刷直流電機三環控制設計

基于DSP和CPLD的空間瞬態光輻射信號實時識別處理

如何用CPLD實現DSP2407A與S3C4480的通信?

如何設計一種基于CPLD和DSP器件的多分辨率圖像采集處理系統?

怎么實現基于DSP+CPLD的斷路器智能控制單元設計?

怎么實現基于DSP芯片和CPLD的剎車控制系統設計?

怎樣巧用DSP在電源設計中的應用?

有償找一位精通CPLD和DSP的高手

求一種基于DSP+CPLD的全數字化控制系統的實現方案

采用CPLD的DSP與聲卡的接口技術

采用CPLD的DSP與聲卡的接口電路設計

高速數據采集系統的硬件結構,CPLD在高速數據采集系統中的應用

基于CPLD 和DSP 的級聯型多電平逆變器控制系統的設計介

27

27用DSP實現CPLD多方案現場可編程配置

29

29基于CPLD的DSP和液晶模塊接口設計

22

22單片機應用系統的CPLD 應用設計

39

39用DSP實現CPLD多方案現場可編程配置

16

16CPLD在交流電機控制系統中的測速應用

23

23基于CPLD的DSP和液晶模塊接口設計

22

22基于DSP與CPLD的ADS7805多通道數據采集

58

58基于DSP+CPLD可重構數控系統的設計

23

23DSP和CPLD在分布式變電站遠動終端監控系統的應用

11

11基于CPLD和DSP的線陣CC 檢測系統的設計

22

22用CPLD實現DSP與背板VME總線之間的連接

51

51基于DSP與CPLD的ADS7805多通道數據采集

43

43基于CPLD的PSK系統設計

20

20基于DSP和CPLD的液晶模塊的設計

54

54基于CPLD+DSP的實時數字圖像穩定系統

35

35基于DSP+CPLD可重構數控系統的設計

13

13單片機應用系統的CPLD應用設計

39

39基于DSP和CPLD電能質量監測裝置的設計

31

31基于CPLD的清分機紙幣圖像采集系統

38

38基于DSP與CPLD的I2C總線接口的設計與實現

1105

1105

基于DSP和CPLD的寬帶信號源的設計

1031

1031

用CPLD實現DSP與PLX9054之間的連接

1294

1294

基于DSP和CPLD的液晶模塊的設計

744

744基于DSP和CPLD可重構數控系統的設計與仿真

576

576

基于DSP芯片和CPLD的剎車控制系統設計

998

998

CPLD的DSP多SPI端口通信設計

3294

3294

CPLD在TMS320F2812系統中的應用

2949

2949

基于DSP+CPLD的智能IED設計

1277

1277

基于DSP與CPLD的多通道數據采集系統設計

1810

1810DSP+CPLD實現指紋識別系統

156

156基于DSP+CPLD構架的電能質量檢測裝置

8

8ARM,DSP,FPGA,CPLD,SOPC,SOC的區別 FPGA與CPLD的區別詳解

4349

4349如何使用DSP和CPLD進行語音處理系統的設計資料說明

6

6 電子發燒友App

電子發燒友App

評論