SI(信號完整性)研究的是信號的波形質量,而PI(電源完整性)研究的是電源波形質量, PI研究的對象是PDN(Power Distribution Network,電源分配網絡),它是從更加系統

2023-04-18 12:07:45 7439

7439

損耗如何造成上升邊退化?分析介質損耗與耗散因子的特點,損耗 . 如何吃掉高頻分量?如何影響數據完整性?如何用眼圖分析符號間干擾及抖動?第七講 PCB 多網絡串擾分析與設計 基于互容、互感的傳輸線串擾分析

2010-12-16 10:03:11

PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB疊放準則在本博客中,將來自不同來源的許多準則收集在一起。 它們在這里匯總以供參考。 優質的PDN設計并不需要滿足所有要求。 而是應根據特定PCB電路的特性制定詳細的設計準則。...

2021-12-28 07:55:36

1.PCB走線線寬的重要性 PCB載流能力的計算一直缺乏權威的技術方法、公式,經驗豐富CAD工程師依靠個人經驗能作出較準確的判斷。但是對于CAD新手,不可謂遇上一道難題。 對于大電流電源走線

2023-04-12 16:02:23

確定該電路具有較好的信號完整性。反之,當信號不能正常響應時,就出現了信號完整性問題。 高速PCB的信號完整性問題主要包括信號反射、串擾、信號延遲和時序錯誤。 · 反射:信號在傳輸線上傳輸時,當高速

2018-11-27 15:22:34

PCB信號速率不高,需要考慮信號完整性么?

2014-12-10 10:28:44

商都能生產,但是價格比第一種情況稍貴,不會貴太多。二、銳角/直角銳角走線一般布線時禁止出現,直角走線一般是PCB布線中要求盡量避免的情況,也幾乎成為衡量布線好壞的標準之一。因影響信號的完整性,直角布線會產生

2022-12-02 10:21:03

PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB布局指南1.攜帶高速數字信號或時鐘的走線長度應最小化。高速數字信號和時鐘通常是最強的噪聲源。這些走

2021-12-28 06:37:30

本帖最后由 lee_st 于 2018-1-24 16:15 編輯

PCB電流與信號完整性設計

2018-01-24 16:13:42

比較直接的結果是從信號完整性上表現出來的,但我們絕不能因此忽略了電源完整性設計。因為電源完整性直接影響最終PCB板的信號完整性。電源完整性和信號完整性二者是密切關聯的,而且很多情況下,影響信號畸變的主要...

2021-12-28 07:48:43

直接的結果是從信號完整性上表現出來的,但我們絕不能因此忽略了電源完整性設計。因為電源完整性直接影響最終PCB板的信號完整性。電源完整性和信號完整性二者是密切關聯的,而且很多情況下,影響信號畸變

2018-09-11 16:19:05

本帖最后由 gk320830 于 2015-3-7 13:54 編輯

PCB設計中的電源信號完整性的考慮在電路設計中,一般我們很關心信號的質量問題,但有時我們往往局限在信號線上進行研究,而把

2013-10-11 11:03:03

直接的結果是從信號完整性上表現出來的,但我們絕不能因此忽略了電源完整性設計。因為電源完整性直接影響最終PCB板的信號完整性。電源完整性和信號完整性二者是密切關聯的,而且很多情況下,影響信號畸變

2018-09-13 16:00:59

。參考:PCB設計中要考慮電源信號的完整性電源完整性| PCB設計資源...

2021-12-27 07:17:16

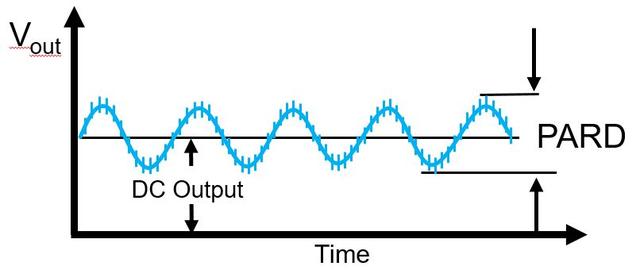

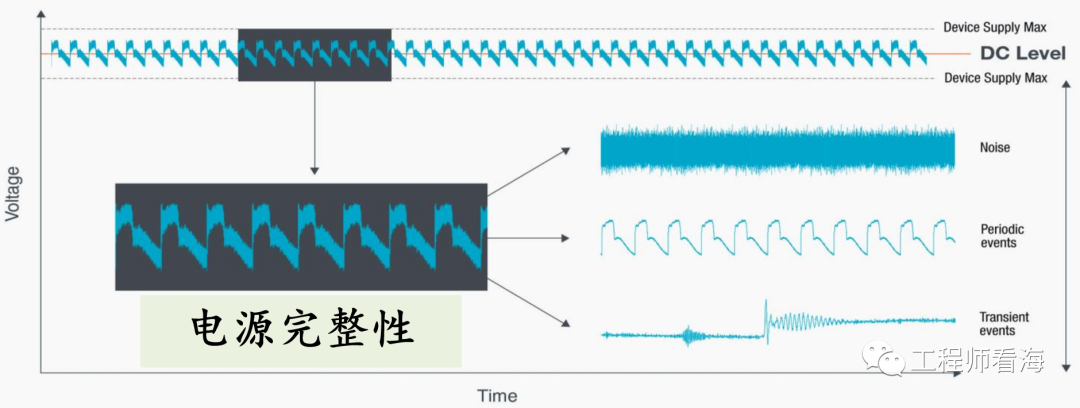

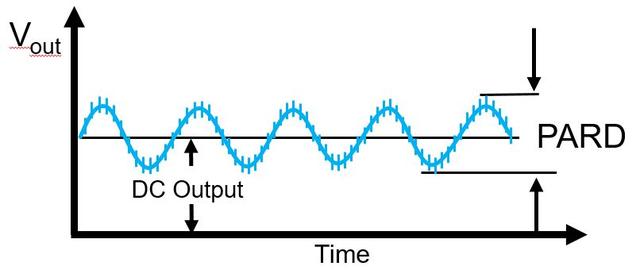

電源完整性是指電源波形的質量,研究的是電源分配網絡(PDN),并從系統供電網絡綜合考慮,消除或者減弱噪聲對電源的影響。電源完整性的設計目標是把電源噪聲控制在運行的范圍內,為芯片提供干凈穩定的電壓,并

2020-10-20 13:57:04

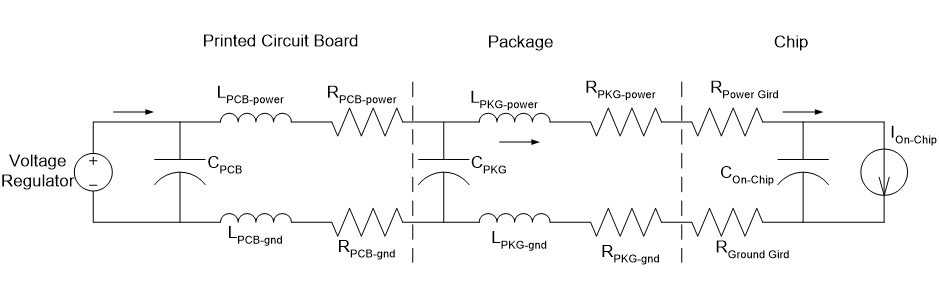

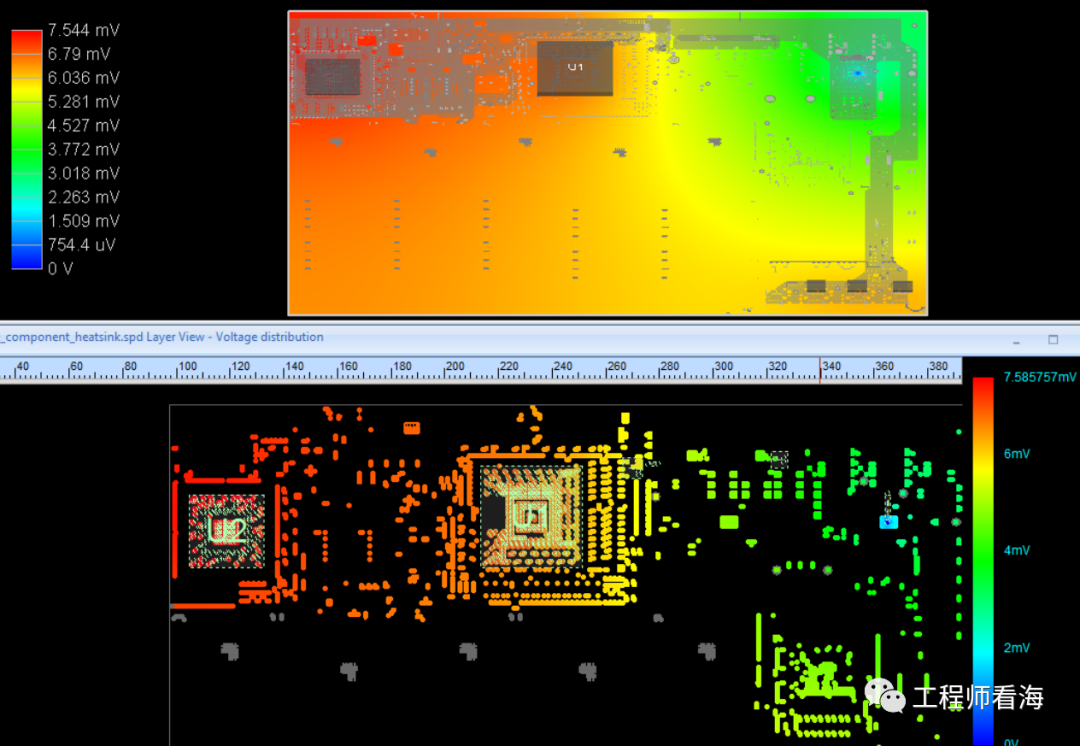

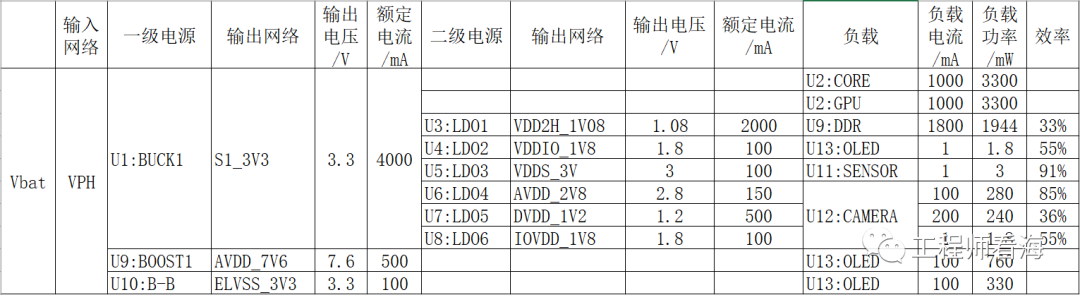

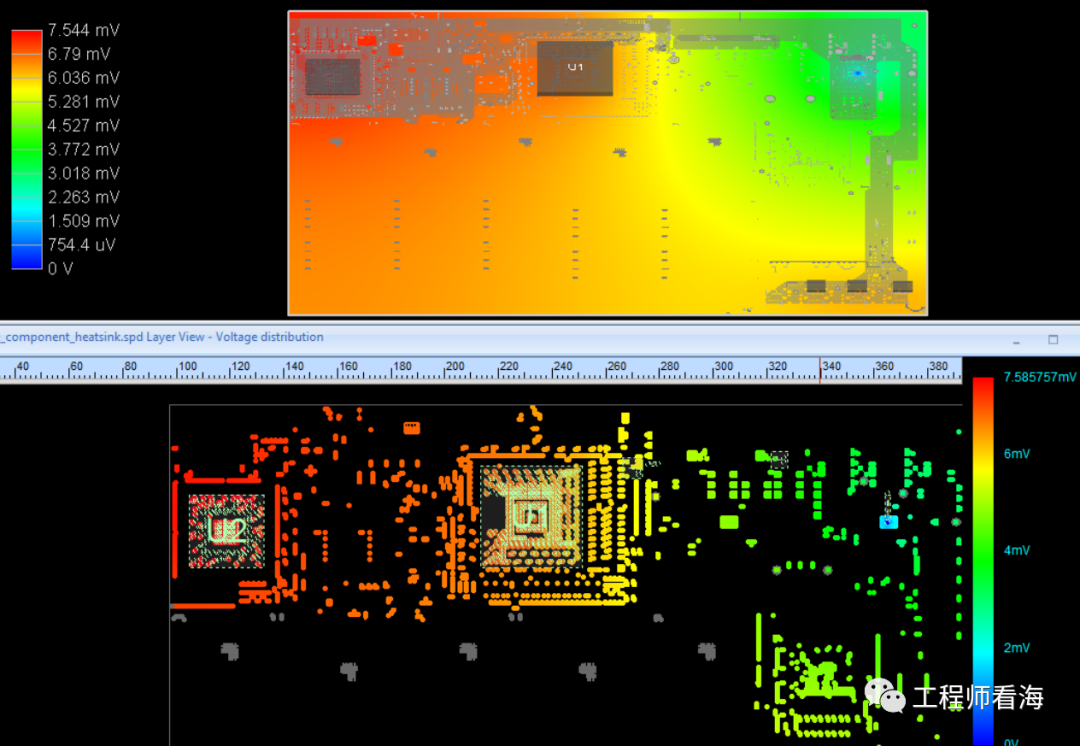

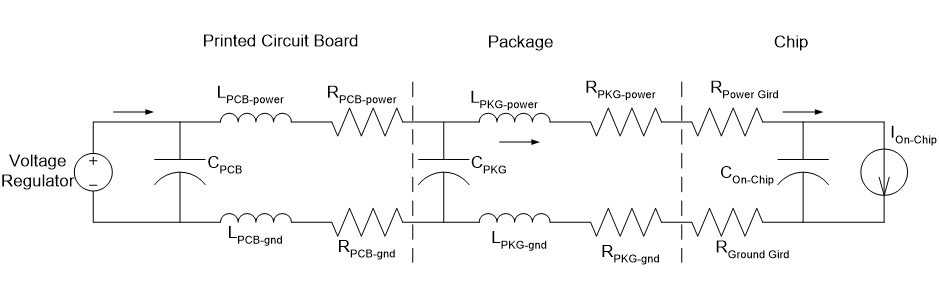

電流從電源變換器出來,經過PCB板上的走線、過孔,再經過芯片封裝焊球/引腳,封裝里面的Wirebond,最終到達芯片里的Die,將傳送電流的這些互聯通道稱為電源分配網絡(PDN)1、對PDN

2021-12-30 07:08:21

電源完整性(Power Integrity),簡稱為PI,也就是大家平常聽說的PI。PCB板上的電源設計也是非常重要的,不當的設計也會引起很重要的影響。所以電源完整性PI和信號完整性SI,是我們互連

2021-11-15 07:20:09

為PCB(印刷電路板)上的芯片提供電能不再是一種簡單的工作。過去,通過細走線將IC連接到電源和地就行了,這些走線占不了多少空間。當芯片速度升高時,就要用低阻抗電源為它們供電,如用PCB上的一個電源層

2019-05-21 09:23:34

,解3D的Maxwell方程。不過,3D場解算器要花很長時間才能得到結果,尤其是用于相對較大的物理項時,如PCB板。因此,電源完整性供應商在自己的電源完整性工具中設計了混合型解算器技術。在解算走線

2011-11-10 15:06:08

本文轉自電源研發圈為PCB(印刷電路板)上的芯片提供電能不再是一種簡單的工作。過去,通過細走線將IC連接到電源和地就行了,這些走線占不了多少空間。當芯片速度升高時,就要用低阻抗電源為它們供電,如用

2021-12-30 08:05:03

電源完整性分析,在別處下的,看了好幾遍,覺得是好東西,就給大家分享一下吧

2013-04-02 10:30:34

最近在論壇里看到一則關于電源完整性的提問,網友質疑大家普遍對信號完整性很重視,但對于電源完整性的重視好像不夠,主要是因為,對于低頻應用,開關電源的設計更多靠的是經驗,或者功能級仿真來輔助即可,電源

2021-10-29 08:29:10

`本專題詳細介紹了電源完整性各部分知識,包括電源完整性的基礎概述,電源完整性設計分析及仿真知識,還有具體應用中的一些小經驗分享等等,充分翔實的向大家描述了電源完整性。 `

2015-01-15 11:09:59

電源完整性是什么意思?能不能講解下

2022-06-27 22:23:39

電源完整性設計

2014-03-07 15:49:55

真正意義上的電源完整性。本文將深入探討這三個關鍵方面,為PCB設計提供實用的指導和策略。一、電源模塊布局布線電源模塊是電子設備的能量來源,其性能與布局直接影響到整個系統的穩定性和效率。正確的布局和走線

2024-02-21 21:37:07

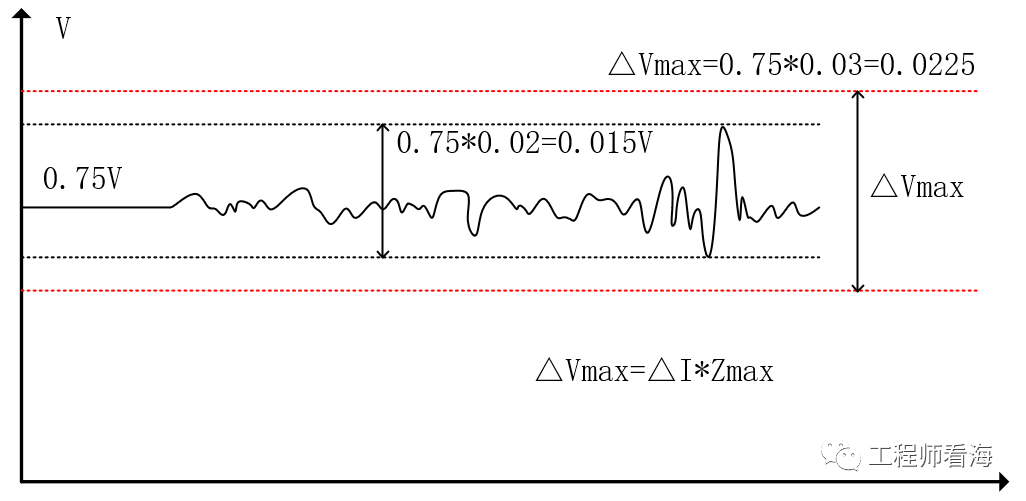

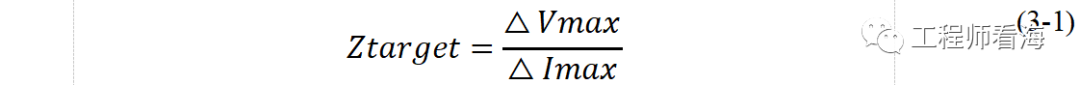

該文章對于剛開始學習的人理解電源完整性稍有一點作用。這里的內容不能直接在工程上應用,但是對于建立感覺還是有幫助的。文章中有些地方存在數值計算錯誤,沒有修改。對本文有興趣的看看就好,不必糾結具體數值,這篇文章主要的出發點是定性的說明,看完了能對電源完整性有點感覺就達到目的了

2019-02-26 08:30:00

電源完整性設計詳解_于博士

2012-08-18 08:08:16

要求的符合程度。

電源完整性研究的是電源分配網絡(Power Distribution Network,PDN),包含電源的源頭,供電模塊VRM、PCB上的儲能電容和去偶電容、PCB上的電源和地平

2023-04-24 11:46:21

分析及應用系列四 --- 實例分析3:同時多網絡仿真的極限分析4.1 對仿真故障進行分析4.2 識別電源完整性關

2021-12-31 08:02:17

后(PCB版圖設計階段)兩部分SI分析功能;采用成熟的傳輸線計算方法,以及I/O緩沖宏模型進行仿真。基于快速反射和串擾模型,信號完整性分析器使用完全可靠的算法,從而能夠產生出準確的仿真結果。布線前

2015-12-28 22:25:04

Cadenc高速電路設計SI PI 信號完整性電源完整性仿真視頻教程下載鏈接地址:鏈接:http://pan.baidu.com/s/1pJiPpzl密碼:3yjv

2015-07-30 21:44:10

。線寬為4mil。

我想問,在這種情況下,我是否可以通過控制這些信號走線的阻抗,再通過仿真這些信號,找到比較適合的阻抗值,從而同樣達到減少或消除反射的噪音,滿足信號完整性的要求。

2018-06-21 00:05:07

哪位同學有Hyperlynx的對PCB信號完整性仿真的相關教程分享一下???跪求!!!

2016-06-15 10:16:02

【PDF】電源完整性設計詳解附件:

2011-03-03 09:39:27

`編輯推薦本書全面論述了信號完整性與電源完整性問題。主要講述信號完整性分析及物理設計概論,6類信號完整性問題的實質含義,物理互連設計對信號完整性的影響,電容、電感、電阻和電導的特性分析,求解信號

2017-08-08 18:03:31

功能混亂。PCB信號完整性的步驟在信號完整的理想情況下,所有高速節點應該布線在阻抗控制內層(例如帶狀線)。要使SI最佳并保持電路板去耦,就應該盡可能將接地層/電源層成對布放。如果只能有一對接地層/電源層

2019-09-25 07:30:00

復雜。通常認為,電源完整性包括從穩壓器模塊(VRM)到片上核心電源線以及片上電容等范圍內的部分。電源分配網絡(PDN)是指在VRM和片上Vdd-Vss電源線之間的所有這些內部連接(通常是感性),以及刻意

2019-08-15 13:53:54

為什么要在意電源系統的信號完整性?電源系統的噪聲余量分析電源噪聲是如何產生的呢?

2021-02-24 08:00:33

首先我們定義下什么是電源和信號完整性?信號完整性 信號完整性(SI)分析集中在發射機、參考時鐘、信道和接收機在誤碼率(BER)方面的性能。電源完整性(PI)側重于電源分配網絡 (PDN) 提供恒定

2021-12-30 06:33:36

的符合程度。 電源完整性研究的是電源分配網絡(Power Distribution Network,PDN),包含電源的源頭,供電模塊VRM、PCB上的儲能電容和去偶電容、PCB上的電源和地平面、芯片

2023-04-11 15:17:05

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

做了電路設計有一段時間,發現信號完整性不僅需要工作經驗,也需要很強的理論指導,壇友能提供一些信號完整性的視頻資料么?非常感謝!

2019-02-14 14:43:52

在altium designer中想進行信號完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

。穿過過孔的快速、單端信號與配電網絡(PDN)進行強有力地交互。從這些過孔返回的電流穿過附近的縫合孔、縫合電容器和/或平面對(組成PDN且需要建模以進行電源完整性分析的相同元器件)。圖1:在走線橫截面

2019-06-17 10:23:53

在處理高速印刷電路板(PCB)時,必須理解信號完整性(SI)和電源完整性(PI)的基本原理。如今,速度是評估數字產品功能的主要因素之一。在幾種設計中,PCB布局對整體功能至關重要。對于高速設計,SI

2021-12-30 06:49:16

高速設計中的信號完整性和電源完整性分析

2021-04-06 07:10:59

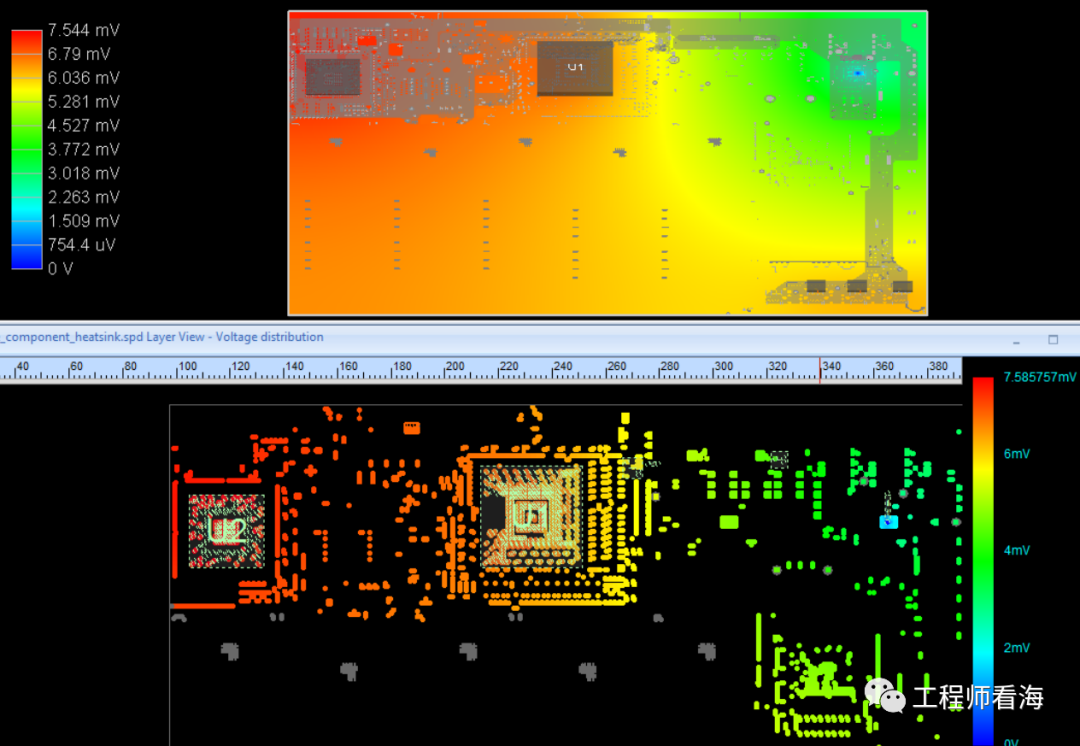

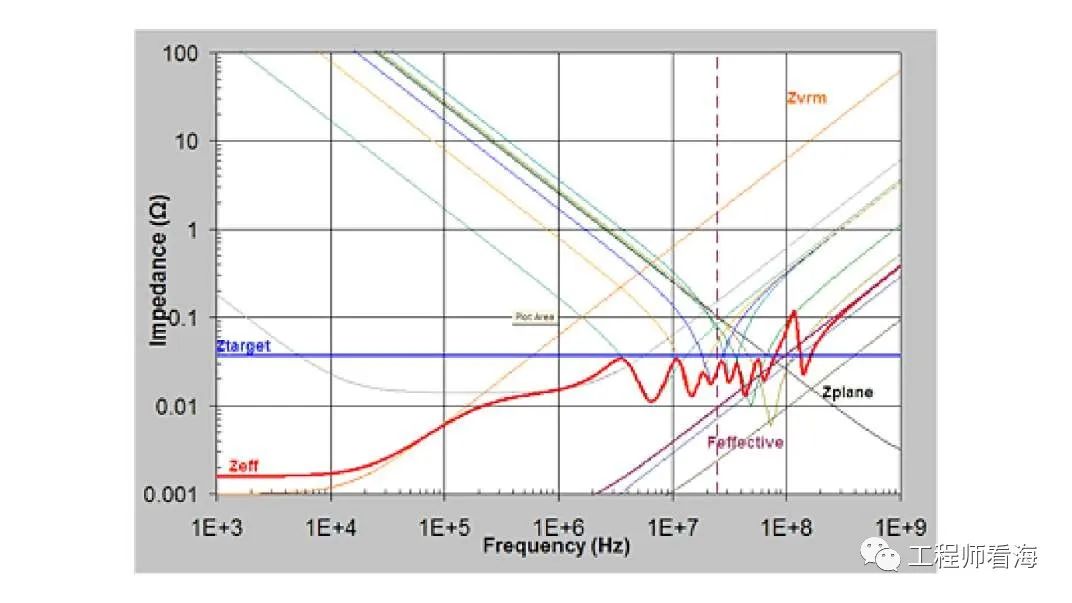

原本放在頂層的走線信號傳輸或串擾性能。 對于電源完整性來說,增加電源與地之間的容性耦合可以濾除電源中的交流波動。在實際應用中,往往采取加解耦電容的方法。電流密度的動態顯示可以幫助設計者直觀了解到電源

2015-01-07 11:33:53

信號完整性與電源完整性的仿真分析與設計,不看肯定后悔

2021-05-12 06:40:35

最近在論壇里看到一則關于電源完整性的提問,網友質疑大家普遍對信號完整性很重視,但對于電源完整性的重視好像不夠,主要是因為,對于低頻應用,開關電源的設計更多靠的是經驗,或者功能級仿真來輔助即可,電源

2021-11-15 09:07:04

其實電源完整性可做的事情有很多,今天就來了解了解吧。信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領域相關的分析,涉及數字電路正確操作。在信號完整性中,重點是確保傳輸

2021-11-15 07:37:08

先說一下,信號完整性為什么寫電源完整性? SI 只是針對高速信號的部分,這樣的理解沒有問題。如果提高認知,將SI 以大類來看,SI&PI&EMI 三者的關系:所以,基礎知識系列里還是

2021-11-15 06:32:45

高速PCB設計有很多比較考究的點,包括常規的設計要求、信號完整性的要求、電源完整性的要求、EMC的要求、特殊設計要求等等。本文主要是針對高速電路信號總線做了一些比較常規的要求列舉了一些檢查要點,其實

2021-01-14 07:11:25

中國電子電器可靠性工程協會關于組織召開“信號完整性仿真應用”高級研修班的邀請函各有關單位:為了幫助廣大從業人員詳細了解信號完整性(SI)和電源完整性(PI)的基本概念、分析方法和應用實例,幫助電子

2009-11-25 10:13:20

信號完整性資料

2015-09-18 17:26:36

信號完整性的定義信號完整性包含哪些內容

2021-03-04 06:09:35

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

、Sigrity,對于信號完整性工程師來講至少要熟悉一種仿真軟件。這樣才能增加你設計的信心。本資料系統整合了相關資料,工程師們可根據自身情況選擇適合自己的學習資料,以下為資料截圖:參與以下活動還可以獲得精美書籍:【送書福利】不懂PDN談何電源完整性?請收下這本PDN設計指導硬核書

2019-09-03 17:54:59

課程背景: 近 10 年電子行業面臨許多新情況:1. 高速寬帶數字系統中的各種完整性問題日益嚴重;2. 設計師正在用傳輸線/差分對的觀點設計芯片、PCB 及系統互連;3. 已有的USB3.0

2010-05-29 13:29:11

最近在論壇里看到一則關于電源完整性的提問,網友質疑大家普遍對信號完整性很重視,但對于電源完整性的重視好像不夠,主要是因為,對于低頻應用,開關電源的設計更多靠的是經驗,或者功能級仿真來輔助即可,電源

2021-11-11 07:29:10

時,必須考慮在需要的時候,信號能達到所必需的電壓電平數值,即信號具有良好的信號完整性。 串擾 串擾是指兩條信號線之間的信號發生耦合,即信號線之間的互感和互容會引起信號線上的噪聲。PCB板層的參數

2018-08-27 16:13:55

基于信號完整性分析的PCB設計流程如圖所示。 主要包含以下步驟: 圖 基于信號完整性分析的高速PCB設計流程 (1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立

2018-09-03 11:18:54

,與信號本身的頻率相比,信號邊沿的諧波頻率更高,信號快速變化的跳變(上升沿與下降沿)引發了信號傳輸的非預期效果。這也是信號完整性問題的根源所在。因此,如何在高速PCB設計過程中充分考慮信號完整性因素,并

2015-01-07 11:30:40

數字信號應該都具有一個連續的、可實現的解空間。即當PCB及元器件參數在一定的范圍內變化、元器件在PCB板上的布局以及信號線在PCB板上的布線方式具有一定的靈活性的情況下,仍然能夠保證對信號完整性的要求

2018-08-29 16:28:48

數字信號應該都具有一個連續的、可實現的解空間。即當PCB及元器件參數在一定的范圍內變化、元器件在PCB板上的布局以及信號線在PCB板上的布線方式具有一定的靈活性的情況下,仍然能夠保證對信號完整性的要求

2008-06-14 09:14:27

和朋友聊天時,經常會有人問我你現在從事什么工作呀?當我說我是從事電源完整性(Power Integrity)和信號完整性(Signal Integrity)性能測試方面的工作的時候,對方總是一臉蒙B

2021-12-30 06:10:21

常值得注意的問題。本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設計信號完整性的方法。PCB信號完整性的問題包括:PCB的信號完整性問題主要包括信號

2018-07-31 17:12:43

為PCB(印刷電路板)上的芯片提供電能不再是一種簡單的工作。過去,通過細走線將IC連接到電源和地就行了,這些走線占不了多少空間。當芯片速度升高時,就要用低阻抗電源為它們供電,如用PCB上的一個電源層

2021-12-28 08:08:01

高速數字PCB設計信號完整性解決方法

2021-03-29 08:12:25

何為信號完整性?信號完整性包括哪些?干擾信號完整性的因素有哪些?如何去解決?

2021-05-06 07:00:23

電源完整性是什么意思?可不可以在頂層或底層走電源部分線。然后在專門的電源層和地層走剩余的線。求指點。

2015-08-18 10:05:41

模擬電路設計(電源or信號鏈)和電源完整性,職業發展前景差距大嗎?

2023-06-07 11:31:37

在電路設計中,一般我們很關心信號的質量問題,但有時我們往往局限在信號線上進行研究,而把電源和地當成理想的情況來處理,雖然這樣做能使問題簡化,但在高速設計中,這種簡化已經是行不通的了。盡管電路設計比較直接的結果是從信號完整性上表現出來的,但我們絕不能因此忽略了電源完整性設計。因為電源完整性直...

2021-12-30 07:05:05

的頂層和底層使用組合微帶層時要小心。這可能導致相鄰板層間走線的串擾,危及信號完整性。

按信號組的最長延遲為時鐘(或選通)信號走線,這保證了在時鐘讀取前,數據已經建立。

在平面之間對嵌入式信號進行走線

2024-02-19 08:57:42

信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領域相關的分析,涉及數字電路正確操作。在信號完整性中,重點是確保傳輸的1在接收器中看起來就像 1(對0同樣如此)。在電源

2021-11-15 06:31:24

PCB設計中的電源信號完整性的考慮因素有哪些?

2021-04-23 06:54:29

有網友質疑大家普遍對信號完整性很重視,但對于電源完整性的重視好像不夠,主要是因為,對于低頻應用,開關電源的設計更多靠的是經驗,或者功能級仿真來輔助即可,電源完整性分析好像幫不上大忙,而對于50M

2019-09-20 14:44:25

有這樣一種錯誤認識,認為速率不高的PCB不用考慮信號完整性問題,可以隨便設計。盡管有時候PCB也會出問題,但并不認為是信號完整性的事。信號完整性和信號速率其實沒多大關系。舉一個例子,如果PCB板上有

2016-12-07 10:08:27

在高速PCB電路板的設計和制造過程中,工程師需要從布線、元件設置等方面入手,以確保這一PCB板具有良好的信號傳輸完整性。在今天的文章中,我們將會為各位新人工程師們介紹PCB信號完整性設計中常

2018-11-27 09:57:50

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

高速電路信號完整性分析與設計—PCB設計多層印制板分層及堆疊中應遵徇的基本原則;電源平面應盡量靠近接地平面。布線層應安排與映象平面層相鄰。重要信號線應緊臨地層。[hide] [/hide][此貼子已經被作者于2009-9-12 10:38:14編輯過]

2009-09-12 10:37:02

的各種完整性問題日益嚴重;2. 設計師正在用傳輸線/差分對的觀點設計芯片、PCB 及系統互連;3. 已有的USB3.0/IEEE1394C 接口逐漸取代并口,FPGA 新增LVDS 接口模塊等等。我國

2010-04-21 17:11:35

在設計 PCB 時,尤其是在涉及多種信號類型和電源方案的情況下,您將面臨為電路板找到正確的電源完整性解決方案的難題。盡管功率是電信號的屬性,但不要將功率完整性與信號完整性。但是,兩者對于您的電路板

2020-10-10 18:32:22 1410

1410 的電源噪聲抑制和電源配送網絡元件的建模與分析,最終借助于 Cadence 電源完整性工具 Allegro PCB PI 完成了實際電源分配網絡的設計。

2021-04-21 09:58:06 0

0 信號完整性(SI)分析集中在發射機、參考時鐘、信道和接收機在誤碼率(BER)方面的性能。電源完整性(PI)側重于電源分配網絡 (PDN) 提供恒定、干凈的電源和低阻抗返回路徑的技術。SI和PI具有

2021-09-03 11:11:52 1503

1503 信號完整性與電源完整性的仿真(5V40A開關電源技術參數)-信號完整性與電源完整性的仿真分析與設計!!!

2021-09-29 12:11:21 89

89 PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB疊放準則在本博客中,將來自不同來源的許多準則收集在一起。 它們在這里匯總以供參考。 優質的PDN設計并不需要滿足所有要求。 而是應根據特定PCB電路的特性制定詳細的設計準則。...

2022-01-06 12:19:32 11

11 PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB平面圖指南在開始進行PCB布局之前,必須注意正確放置組件。 較低等級的模擬,高速數字和噪聲電路

2022-01-06 12:22:33 4

4 比較直接的結果是從信號完整性上表現出來的,但我們絕不能因此忽略了電源完整性設計。因為電源完整性直接影響最終PCB板的信號完整性。電源完整性和信號完整性二者是密切關聯的,而且很多情況下,影響信號畸變的主要...

2022-01-06 12:28:34 6

6 首先我們定義下什么是電源和信號完整性?信號完整性 信號完整性(SI)分析集中在發射機、參考時鐘、信道和接收機在誤碼率(BER)方面的性能。電源完整性(PI)側重于電源分配網絡 (PDN) 提供恒定

2022-01-07 15:34:31 22

22 由于這個系列主要是講基于PCB的電源完整性仿真,所以只涉及VRM和PCB上面的設計。所以后文中提到的PDN都泛指VRM+PCB。

2023-06-16 10:52:18 2067

2067

電子發燒友網站提供《基于PDN共振峰的最壞情況數據模式分析電源完整性對FPGA DDR4存儲器接口中的信號完整性的影響.pdf》資料免費下載

2023-09-13 09:56:49 0

0 電源完整性(Power Integrity,PI)是衡量電源分配網絡PDN(Power Distribution Network,PDN)的源端及終端的電壓及電流是否符合需求。

2023-09-28 10:59:14 926

926

▼關注公眾號:工程師看海▼ ??大家好,我是工程師看海,原創文章感謝 點贊分享 ! SI(信號完整性)研究的是信號的波形質量,而PI(電源完整性)研究的是電源波形質量, PI研究的對象是PDN

2023-11-07 08:46:03 2243

2243

電子發燒友App

電子發燒友App

評論